Werbung

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt und detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag gegeben werden.

Einer der Hersteller, der vom Ökosystem von TSMC profitiert, ist das französische Unternehmen VSORA. Hier hat man einen KI-Beschleuniger von RISC-V-Basis entwickelt. Der Jotunn 8 bietet 288 GB HBM3E mit einer Speicherbandbreite von 8 TB/s. Die beiden Compute-Chiplets kommen auf 144 Milliarden Transistoren und erreichen eine Rechenleistung von 3,2 PFLOPS (Dense FP8). Zum Vergleich: AMDs Instinct MI355X kommt auf 10,1 PFLOPS, eine Blackwell-GPU bringt es auf 9 PFLOPS.

Für die Fertigung der Compute-Chiplets nutzt VSORA die Fertigung in N5 bei TSMC sowie das CoWoS-S-Packaging. Das gesamte Package bringt es auf 70 x 80 mm. Laut Angabe der Entwickler hat man nur rund 18 Monate Entwicklungszeit für den Chip benötigt.

Aber auch In-House spielt KI bei TSMC eine Rolle, wenngleich vieles davon bereits unter dem Begriff Machine Learning zum Einsatz kam. Dazu gehört die KI-Unterstützung für das Design und die Verifikation von Chips, aber auch in der Fertigung sowie das Testing.

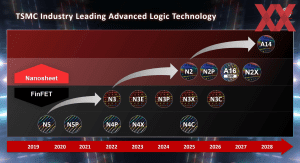

In den kommenden Monaten und Jahren stehen bei TSMC große Prozessschritte an. Von der N3-Familie geht es zur N2-Familien mit dem Einsatz der neuen Nanosheet-Transistoren. Im nächsten Schritt wird A16 die Nanosheet-Transistoren mit der rückseitigen Spannungsversorgung alias Super Power Rail (SPR) kombinieren. Mit A14 soll dann sogar ein verbessertes Nanosheet-Design eingeführt werden.

Der Zeitplan sieht aktuell wie folgt aus:

Die Fertigung in N2 befindet sich bereits in der Massenfertigung. N2P soll bereits Anfang 2026 starten und die ersten Chips in A16 mit SPR folgen bereits Ende 2026.

Für die günstigeren FinFET-Prozesse sieht TSMC weiterhin die verbesserten Versionen N3C und N4C vor, die im Falle von N4C bereits durch Kunden angeboten wird.

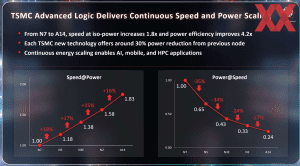

Dass es in den kommenden Jahren mit den kommenden Fertigungsschritten eine Weiterentwicklung geben wird, unterstreicht TSMC mit der Abbildung der ISO-Power von N7 bis zu A14. Teilweise kennen wir die genannten Zahlen für zum Beispiel N2 auf A16 schon. Worum es TSMC hier aber geht, ist die beständige Weiterentwicklung. Für N7 zu A14 wird eine verbesserte Leistung bei gleicher Leistungsaufnahme um den Faktor 1,8 angegeben. Für den Schritt von N2 auf A14 wird ein höherer Takt von 16 % bei gleicher Leistungsaufnahme angegeben. Die Entwicklung von A16 zu A14 lässt TSMC an dieser Stelle aus.

A16 mit SPR soll bei gleicher Spannung im Vergleich zu N2P 8 bis 10 % höhere Taktraten erreichen können. Bei gleicher Leistungsaufnahme sollen Chips in A16 eine um 15 bis 20 % geringere Leistungsaufnahme vorweisen können.

Die Effizienz sieht TSMC aber als weitaus wichtiger an. Von N7 zu A14 soll die Effizienz um den Faktor 4,2 gesteigert werden können. Aber für die Effizienz ist eine gewisse Verlangsamung in der Entwicklung zu erkennen.

Zudem verweist TSMC auf die NanoFlex-Technologie, welche zusammen mit der N2-Familie eingeführt wurde. Mittels NanoFlex kann das Zelldesign angepasst werden, was laut TSMC die Chips um 15 % schneller oder um 30 % effizienter machen kann.

An TSMC führt kein Weg vorbei

In den kommenden Jahren dürfte kein Fabless-Chipentwickler im HPC/KI-Segment an TSMC vorbeikommen. TSMC vereint die enge Verzahnung von Chipfertigung und EDA und setzt damit schon früh in der Entwicklung eines Chips an. Darüber hinaus bietet man mit seiner Chipfertigung die besten Prozesse am Markt und beherrscht mit dem Advanced Packaging auch die Integration der Chips in einem Multi-Chip-Design, mit HBM und vieles mehr.