News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Fertigung

-

Mehr CPUs statt SoCs: AMD übernimmt freie N4/N5-Kapazitäten

AMDs letzte Quartalszahlen sowie die eigene Einschätzung des Unternehmens sehen CPUs wieder im Kommen. Sie sollen mehr als nur der Host-Prozessor in einem KI-System sein, sondern vermehrt auch wieder die eigentlichen Rechenaufgaben übernehmen. Ein Problem für AMD ist allerdings, dass man hinsichtlich der Fertigungskapazitäten eingeschränkt ist und die Stückzahlen nicht in dem Maße hochgefahren werden können. Dem zu Pass kommt nun die Meldung,... [mehr]

AMDs letzte Quartalszahlen sowie die eigene Einschätzung des Unternehmens sehen CPUs wieder im Kommen. Sie sollen mehr als nur der Host-Prozessor in einem KI-System sein, sondern vermehrt auch wieder die eigentlichen Rechenaufgaben übernehmen. Ein Problem für AMD ist allerdings, dass man hinsichtlich der Fertigungskapazitäten eingeschränkt ist und die Stückzahlen nicht in dem Maße hochgefahren werden können. Dem zu Pass kommt nun die Meldung,... [mehr] -

Für Kamerasensoren: Sony und TSMC verkünden Partnerschaft

Sony und TSMC haben eine Absichtserklärung verkündet, nach der es ein Joint Venture beider Unternehmen geben soll, das sich mit der Entwicklung und Fertigung der Bildsensoren der nächsten Generation beschäftigt. Einen Namen hat das Joint Venture nocht nicht, bekannt ist aber, dass Sony die Leistung übernehmen wird. Eine Zusammenarbeit zwischen Sony und TSMC ist indes keine wirkliche Neuigkeit. Bereits 2021 gegründet wurde Japan Advanced... [mehr]

Sony und TSMC haben eine Absichtserklärung verkündet, nach der es ein Joint Venture beider Unternehmen geben soll, das sich mit der Entwicklung und Fertigung der Bildsensoren der nächsten Generation beschäftigt. Einen Namen hat das Joint Venture nocht nicht, bekannt ist aber, dass Sony die Leistung übernehmen wird. Eine Zusammenarbeit zwischen Sony und TSMC ist indes keine wirkliche Neuigkeit. Bereits 2021 gegründet wurde Japan Advanced... [mehr] -

Apple und Intel: Intel könnte bald wieder Chips für Cupertino fertigen

Etwa sechs Jahre nach dem Start von Apple Silicon könnte Intel wieder eine Rolle in Apples Hardware-Strategie spielen. Dieses Mal geht es allerdings nicht um eine Rückkehr klassischer Intel-CPUs in Apple-eigene Geräte wie dem MacBook, iMac oder den Mac mini. Einem Bericht von Bloomberg zufolge soll Apple erste Gespräche mit Intel über die Fertigung eigener Chips geführt haben. Auch Samsung Electronics sei im Gespräch. Konkrete... [mehr]

Etwa sechs Jahre nach dem Start von Apple Silicon könnte Intel wieder eine Rolle in Apples Hardware-Strategie spielen. Dieses Mal geht es allerdings nicht um eine Rückkehr klassischer Intel-CPUs in Apple-eigene Geräte wie dem MacBook, iMac oder den Mac mini. Einem Bericht von Bloomberg zufolge soll Apple erste Gespräche mit Intel über die Fertigung eigener Chips geführt haben. Auch Samsung Electronics sei im Gespräch. Konkrete... [mehr] -

N2U, A13, A12 und immer größere Packages: TSMC auf dem 2026 Technology Symposium

TSMC hat zu seinem 2026 Technology Symposium Neuigkeiten im Bereich der Chipfertigung und dem Packaging verraten. In den kommenden Wochen und Monaten wird TSMC im Rahmen des Symposiums in verschiedenen Städten in den USA, Europa und Asien Halt machen. Die großen Profiteure des KI-Booms heißen nicht nur NVIDIA, AMD, Intel sowie die weiteren Hardware-Hersteller oder sind KI-Infrastrukturanbieter, sondern auch TSMC, denn irgendwo müssen die Chips... [mehr]

TSMC hat zu seinem 2026 Technology Symposium Neuigkeiten im Bereich der Chipfertigung und dem Packaging verraten. In den kommenden Wochen und Monaten wird TSMC im Rahmen des Symposiums in verschiedenen Städten in den USA, Europa und Asien Halt machen. Die großen Profiteure des KI-Booms heißen nicht nur NVIDIA, AMD, Intel sowie die weiteren Hardware-Hersteller oder sind KI-Infrastrukturanbieter, sondern auch TSMC, denn irgendwo müssen die Chips... [mehr] -

Quartalszahlen: TSMC liefert mehr Wafer denn je

TSMC hat seine Vormachtstellung bei den Halbleiterherstellern unterstrichen und vermeldet für das erste Quartal 2026 weiterhin extrem hohe Umsätze und Gewinne. Mit 4,17 Millionen Wafern (300 mm Äquivalent) wurde mehr Chipfläche denn je belichtet. In den vergangenen drei Monaten erreichte TSMC einen Umsatz in Höhe von 35,9 Milliarden US-Dollar. Der Nettogewinn lag bei 18,1 Milliarden US-Dollar. TSMC verdient kräftig, es wird aber... [mehr]

TSMC hat seine Vormachtstellung bei den Halbleiterherstellern unterstrichen und vermeldet für das erste Quartal 2026 weiterhin extrem hohe Umsätze und Gewinne. Mit 4,17 Millionen Wafern (300 mm Äquivalent) wurde mehr Chipfläche denn je belichtet. In den vergangenen drei Monaten erreichte TSMC einen Umsatz in Höhe von 35,9 Milliarden US-Dollar. Der Nettogewinn lag bei 18,1 Milliarden US-Dollar. TSMC verdient kräftig, es wird aber... [mehr] -

Fab34: Intel kauft Fabrikanteile wieder vollständig zurück

Intels finanzielle Probleme und die Umstrukturierungen veranlassten das Unternehmen, 2024 für 49 % der Anteile an der Fab34 in Irland etwa 11,2 Milliarden US-Dollar vom Investor Apollo zu erhalten. Nun kündigte Intel an, dass man diese Anteile wieder zurückkaufen werde. Der Preis ist zwischenzeitlich aber gestiegen. Intel muss nun 14,2 Milliarden US-Dollar für die Anteile auf den Tisch legen. Für Apollo hat sich die... [mehr]

Intels finanzielle Probleme und die Umstrukturierungen veranlassten das Unternehmen, 2024 für 49 % der Anteile an der Fab34 in Irland etwa 11,2 Milliarden US-Dollar vom Investor Apollo zu erhalten. Nun kündigte Intel an, dass man diese Anteile wieder zurückkaufen werde. Der Preis ist zwischenzeitlich aber gestiegen. Intel muss nun 14,2 Milliarden US-Dollar für die Anteile auf den Tisch legen. Für Apollo hat sich die... [mehr] -

Yongin Semiconductor Cluster: Auch SK Hynix plant dreistöckige Reinraumanordnung

SK Hynix hat erste Pläne für die Bauten des Yongin Semiconductor Cluster veröffentlicht. In diesem planen Samsung und SK Hynix gewaltige Investitionen, die über das aktuelle und kommende Jahrzehnt im Bereich von 300 bzw. 410 Milliarden US-Dollar bewegen sollen. Dabei werden gewisse Parallelen zwischen den Plänen von Samsung und der Fab P5 und den Planungen von SK Hynix offensichtlich. In einer ersten Phase will SK Hynix nun... [mehr]

SK Hynix hat erste Pläne für die Bauten des Yongin Semiconductor Cluster veröffentlicht. In diesem planen Samsung und SK Hynix gewaltige Investitionen, die über das aktuelle und kommende Jahrzehnt im Bereich von 300 bzw. 410 Milliarden US-Dollar bewegen sollen. Dabei werden gewisse Parallelen zwischen den Plänen von Samsung und der Fab P5 und den Planungen von SK Hynix offensichtlich. In einer ersten Phase will SK Hynix nun... [mehr] -

HBM- und DRAM-Fertigung: Samsungs P5 bekommt mehr Reinräume in der Höhe

Als Reaktion auf die massive Nachfrage nach DRAM, vorwiegend für LPDDR und HBM, haben alle Speicherhersteller einen massiven Ausbau ihrer Fertigungskapazitäten angekündigt. Dabei vorn mit dabei sind natürlich die beiden südkoreanischen Größen SK Hynix und Samsung, die gleich mehrere hunderte Milliarden US-Dollar investieren wollen – zumindest im Heimatland. Neben neuen Clustern mit gleich mehreren Fabs plant Samsung auch den Ausbau... [mehr]

Als Reaktion auf die massive Nachfrage nach DRAM, vorwiegend für LPDDR und HBM, haben alle Speicherhersteller einen massiven Ausbau ihrer Fertigungskapazitäten angekündigt. Dabei vorn mit dabei sind natürlich die beiden südkoreanischen Größen SK Hynix und Samsung, die gleich mehrere hunderte Milliarden US-Dollar investieren wollen – zumindest im Heimatland. Neben neuen Clustern mit gleich mehreren Fabs plant Samsung auch den Ausbau... [mehr] -

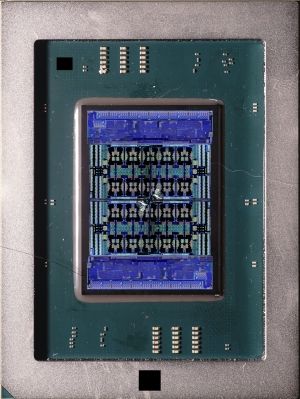

Zen-6-CCD mit 12 Kernen und 48 MB L3-Cache: Nur 7 % größere Chipfläche bei insgesamt 76 mm²

Leaker @9550pro liefert die vermeintliche Die-Größe der nächsten Ryzen-Generation alias Olympic Ridge oder Medusa Ridge. Diese wird genau wie die kommenden Epyc-Prozessoren auf bei TSMC in N2 gefertigte CCDs mit 12 Kernen setzen. Die Anzahl der Kerne je CCD steigt also von 8 auf 12 um 50 % und um eben diese 50 % beträgt auch das Plus beim L3-Cache, der dann 48 MB groß sein soll. Die Fläche von 76 mm² wäre beeindruckend, denn damit... [mehr]

Leaker @9550pro liefert die vermeintliche Die-Größe der nächsten Ryzen-Generation alias Olympic Ridge oder Medusa Ridge. Diese wird genau wie die kommenden Epyc-Prozessoren auf bei TSMC in N2 gefertigte CCDs mit 12 Kernen setzen. Die Anzahl der Kerne je CCD steigt also von 8 auf 12 um 50 % und um eben diese 50 % beträgt auch das Plus beim L3-Cache, der dann 48 MB groß sein soll. Die Fläche von 76 mm² wäre beeindruckend, denn damit... [mehr] -

ASML und Intel: Erster TWINSCAN EXE:5200B mit höherer Genauigkeit und Durchsatz installiert

ASML und Intel geben bekannt, dass man gemeinsam den ersten TWINSCAN EXE:5200B installiert und in Betrieb genommen hat. Intel war der erste Kunde, der einen TWINSCAN EXE:5000 der ersten Generation erhalten hat. In der D1X-Fab in Hillsboro, im US-Bundesstaat Oregon, steht dieser erste High-NA-EUV-Scanner nun seit fast zwei Jahren und wird hier zur Entwicklung zukünftiger Fertigungstechnologien genutzt. Ein erster Prozess, der High-NA EUV... [mehr]

ASML und Intel geben bekannt, dass man gemeinsam den ersten TWINSCAN EXE:5200B installiert und in Betrieb genommen hat. Intel war der erste Kunde, der einen TWINSCAN EXE:5000 der ersten Generation erhalten hat. In der D1X-Fab in Hillsboro, im US-Bundesstaat Oregon, steht dieser erste High-NA-EUV-Scanner nun seit fast zwei Jahren und wird hier zur Entwicklung zukünftiger Fertigungstechnologien genutzt. Ein erster Prozess, der High-NA EUV... [mehr] -

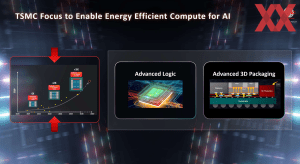

Advanced Silicon, Stacking und Packaging: TSMC baut weiter auf drei Säulen

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt bzw. detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag... [mehr]

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt bzw. detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag... [mehr] -

Snapdragon X2 Elite Extreme: Qualcomm nutzt TSMC FinFlex für N3X und N3P

Bereits bekannt ist, dass Qualcomm zur Fertigung des neuen Snapdragon X2 Elite Extreme den 3-nm-Prozess – genauer gesagt N3P von TSMC – verwendet. In einem Gespräch mit ComputerBase äußerte sich Mandar Deshpande, Senior Director of Product Management bei Qualcomm, zu weiteren Details. Der Snapdragon X2 Elite Extreme erreicht mit seinen Prime-Kernen erstmals für einen ARM-SoC einen maximalen Boost-Takt von 5 GHz. Um diesen Takt... [mehr]

Bereits bekannt ist, dass Qualcomm zur Fertigung des neuen Snapdragon X2 Elite Extreme den 3-nm-Prozess – genauer gesagt N3P von TSMC – verwendet. In einem Gespräch mit ComputerBase äußerte sich Mandar Deshpande, Senior Director of Product Management bei Qualcomm, zu weiteren Details. Der Snapdragon X2 Elite Extreme erreicht mit seinen Prime-Kernen erstmals für einen ARM-SoC einen maximalen Boost-Takt von 5 GHz. Um diesen Takt... [mehr] -

N2P und N3P: AMD geht auch für den kommenden IOD auf fortschrittliche Fertigung

Bereits bekannt ist, dass AMD den CCD für die kommenden Epyc-Prozessoren mit Zen-6-Kernen alias Venice bei TSMC in einem 2-nm-Prozess fertigen wird. Um welchen Prozess es sich genau handelt, war und ist noch nicht bekannt. Leaker Kepler_L2 vermerkt im Forum von AnandTech: Der N2P-Prozess und damit eine auf Leistung optimierte Variante soll es sein. In N2P gefertigt werden sollen die CCDs mit 12 Zen-6-Kernen je Chip. Auch die Dense-CCDs mit den... [mehr]

Bereits bekannt ist, dass AMD den CCD für die kommenden Epyc-Prozessoren mit Zen-6-Kernen alias Venice bei TSMC in einem 2-nm-Prozess fertigen wird. Um welchen Prozess es sich genau handelt, war und ist noch nicht bekannt. Leaker Kepler_L2 vermerkt im Forum von AnandTech: Der N2P-Prozess und damit eine auf Leistung optimierte Variante soll es sein. In N2P gefertigt werden sollen die CCDs mit 12 Zen-6-Kernen je Chip. Auch die Dense-CCDs mit den... [mehr] -

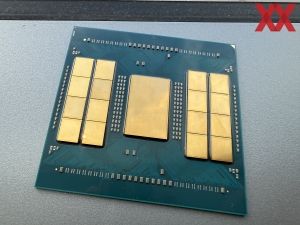

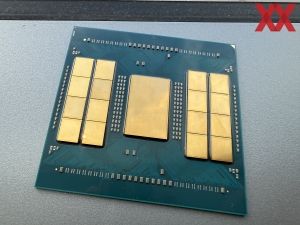

Huawei KunPeng 930: Details zur Fertigung bei TSMC und SMIC

Bereits 2019 stellte Huawei mit mem KunPeng 920 einen Serverprozessor mit 64 ARM-Kernen vor, der damals in 7 nm gefertigt wurde. Inzwischen gibt es mit dem KunPeng 930 den Nachfolger, zu dem es nun eine detaillierte Analyse gibt. Zunächst einmal handelt es sich beim KunPeng um ein Chiplet-Design bestehend aus zwei Compute- und ebenfalls zwei I/O-Dies. Der I/O-Die kommt auf eine Fläche von 172,3 mm² und das zentrale Compute-Die bringt es auf... [mehr]

Bereits 2019 stellte Huawei mit mem KunPeng 920 einen Serverprozessor mit 64 ARM-Kernen vor, der damals in 7 nm gefertigt wurde. Inzwischen gibt es mit dem KunPeng 930 den Nachfolger, zu dem es nun eine detaillierte Analyse gibt. Zunächst einmal handelt es sich beim KunPeng um ein Chiplet-Design bestehend aus zwei Compute- und ebenfalls zwei I/O-Dies. Der I/O-Die kommt auf eine Fläche von 172,3 mm² und das zentrale Compute-Die bringt es auf... [mehr] -

Wirbel bei TSMC: Geschäftsgeheimnisse abgeflossen und Fake News zu Milliardeninvestitionen

In den vergangenen Tagen gab es bei TSMC aus gleich zweierlei Richtungen großen Wirbel und auch einen handfesten Skandal rund um gestohlene Geschäftsgeheimnisse. Aufgrund der Brisanz und Wichtigkeit von TSMC als Unternehmen in Taiwan sind die örtlichen Online- und Fernsehmedien voll mit Meldungen zur Weitergabe von internen Informationen. Im Homeoffice tätig, sollen mehrere Verdächtige auf interne Dokumente zur Fertigung in 2 nm... [mehr]

In den vergangenen Tagen gab es bei TSMC aus gleich zweierlei Richtungen großen Wirbel und auch einen handfesten Skandal rund um gestohlene Geschäftsgeheimnisse. Aufgrund der Brisanz und Wichtigkeit von TSMC als Unternehmen in Taiwan sind die örtlichen Online- und Fernsehmedien voll mit Meldungen zur Weitergabe von internen Informationen. Im Homeoffice tätig, sollen mehrere Verdächtige auf interne Dokumente zur Fertigung in 2 nm... [mehr] -

AMD und Intel: Eine Übersicht der Codenamen, Zeiträume und geplanten Fertigung

Es gibt kontinuierlich Gerüchte zu den kommenden Prozessor-Generationen von AMD und Intel. Zusammen mit den dazugehörigen Fertigungsverfahren werfen wir dabei gerne mit Codenamen um uns, die sicherlich nicht jeder auf den ersten Blick korrekt zuordnen kann. Was für uns zum Alltag gehört, klingt für so manchen Leser gerne wie eine Fremdsprache. Aus diesem Grund wollen wir versuchen die aktuellen Pläne von AMD und Intel einmal etwas... [mehr]

Es gibt kontinuierlich Gerüchte zu den kommenden Prozessor-Generationen von AMD und Intel. Zusammen mit den dazugehörigen Fertigungsverfahren werfen wir dabei gerne mit Codenamen um uns, die sicherlich nicht jeder auf den ersten Blick korrekt zuordnen kann. Was für uns zum Alltag gehört, klingt für so manchen Leser gerne wie eine Fremdsprache. Aus diesem Grund wollen wir versuchen die aktuellen Pläne von AMD und Intel einmal etwas... [mehr] -

Verzögerungen bis 2026: NVIDIAs N1X-Chip hat weiterhin mit Problemen zu kämpfen

Bereits seit Monaten wird über NVIDIAs ARM-Prozessor N1X spekuliert. Dessen Existenz und die Tatsache, dass dieser zusammen mit MediaTek entwickelt wird, hat NVIDIA bereits bestätigt. Der N1X getauchte Chip könnte dem GB10 Blackwell Superchip sehr ähnlich sein. Allerdings dürfte die Anzahl der Kerne deutlich geringer ausfallen. Während der GB10-Chip in den NVIDIA-Spark-Systemen zum Einsatz kommen wird, soll der N1X ein Endkunden-Chip mit... [mehr]

Bereits seit Monaten wird über NVIDIAs ARM-Prozessor N1X spekuliert. Dessen Existenz und die Tatsache, dass dieser zusammen mit MediaTek entwickelt wird, hat NVIDIA bereits bestätigt. Der N1X getauchte Chip könnte dem GB10 Blackwell Superchip sehr ähnlich sein. Allerdings dürfte die Anzahl der Kerne deutlich geringer ausfallen. Während der GB10-Chip in den NVIDIA-Spark-Systemen zum Einsatz kommen wird, soll der N1X ein Endkunden-Chip mit... [mehr] -

In TSMC N2: Nova Lake soll Tape Out geschafft haben

Wie SemiAccurate berichtet, soll ein zukünftiges Produkt, bzw. ein dazugehöriger Chip bei Intel vor wenigen Wochen den wichtigen Meilenstein des Tape Out geschafft haben. Der Tape Out bezeichnet den finalen Schritt im Chipdesign, bei dem das vollständige Layout eines Chips zur Fertigung freigegeben wird. Es ist der Moment, in dem das Design an die Halbleiterfertigung übergeben wird, um Fotomasken für die Chipproduktion zu erstellen. Der... [mehr]

Wie SemiAccurate berichtet, soll ein zukünftiges Produkt, bzw. ein dazugehöriger Chip bei Intel vor wenigen Wochen den wichtigen Meilenstein des Tape Out geschafft haben. Der Tape Out bezeichnet den finalen Schritt im Chipdesign, bei dem das vollständige Layout eines Chips zur Fertigung freigegeben wird. Es ist der Moment, in dem das Design an die Halbleiterfertigung übergeben wird, um Fotomasken für die Chipproduktion zu erstellen. Der... [mehr] -

Intel-CEO: NVIDIA ist aktuell uneinholbar und "Wir müssen demütig sein"

In einem Video an die eigene Belegschaft hat sich Intels CEO Lip-Bu Tan zu einigen Problemen innerhalb des Unternehmens geäußert und nimmt dabei eine erstaunlich offene und ehrliche Einschätzung der Situation des Unternehmens vor. Das in Oregon ansässige Magazin The Oregon zitiert einige Passagen aus dem Video. Das es bei Intel alles andere als rund läuft, ist seit Monaten bekannt. vor fast genau sechs Monaten verließ der Heilsbringer Pat... [mehr]

In einem Video an die eigene Belegschaft hat sich Intels CEO Lip-Bu Tan zu einigen Problemen innerhalb des Unternehmens geäußert und nimmt dabei eine erstaunlich offene und ehrliche Einschätzung der Situation des Unternehmens vor. Das in Oregon ansässige Magazin The Oregon zitiert einige Passagen aus dem Video. Das es bei Intel alles andere als rund läuft, ist seit Monaten bekannt. vor fast genau sechs Monaten verließ der Heilsbringer Pat... [mehr] -

TSMC Arizona: Advanced Packaging ab 2028 auch in den USA

Bisher hat TSMC die Maßgabe herausgegeben, dass moderne Chips zwar auch außerhalb Taiwan in den eigenen Fabs gefertigt werden dürfen, die modernsten Prozesse aber gibt es nur aus dem Heimatland. Taiwan nutzt TSMC so als Silicon Shield und will sicherstellen, dass die Werke auf der Insel so extrem wichtig sind, dass eine eventuelle Besetzung Taiwans durch China den Weltmarkt von den modernsten Chips abschneiden würde. Aktuell fertigt TSMC in... [mehr]

Bisher hat TSMC die Maßgabe herausgegeben, dass moderne Chips zwar auch außerhalb Taiwan in den eigenen Fabs gefertigt werden dürfen, die modernsten Prozesse aber gibt es nur aus dem Heimatland. Taiwan nutzt TSMC so als Silicon Shield und will sicherstellen, dass die Werke auf der Insel so extrem wichtig sind, dass eine eventuelle Besetzung Taiwans durch China den Weltmarkt von den modernsten Chips abschneiden würde. Aktuell fertigt TSMC in... [mehr] -

Weitere Einsparungen: Intel soll 20 % seiner Fab-Belegschaft entlassen

Nachdem Intel im vergangenen Jahr als Gesamtunternehmen seine Belegschaft bereits um etwa 16.000 Mitarbeiter reduziert hatte, deuten sich nun weitere Einsparungen beim Personal an. Naga Chandrasekaran als Leiter der Foundry-Sparte soll die Einsparungen in einer E-Mail an die Belegschaft angekündigt haben. Zwischen 15 und 20 % der Arbeitsstellen sollen abgebaut werden. Im Dezember des letzten Jahres beschäftigte Intel noch 108.900... [mehr]

Nachdem Intel im vergangenen Jahr als Gesamtunternehmen seine Belegschaft bereits um etwa 16.000 Mitarbeiter reduziert hatte, deuten sich nun weitere Einsparungen beim Personal an. Naga Chandrasekaran als Leiter der Foundry-Sparte soll die Einsparungen in einer E-Mail an die Belegschaft angekündigt haben. Zwischen 15 und 20 % der Arbeitsstellen sollen abgebaut werden. Im Dezember des letzten Jahres beschäftigte Intel noch 108.900... [mehr] -

GaN-Wafer für Leistungselektronik: Infineon fährt hoch, TSMC fährt runter

Im vergangenen Jahr verkündete Infineon den Aufbau einer ersten Pilotlinie für die Herstellung von Leistungshalbleitern auf Basis von Galliumnitrid (GaN). Mit einer Fertigung mit Wafern in 300 mm will Infineon damit einerseits die technischen Vorteile dieser Leistungshalbleiter und andererseits auch die wirtschaftlichen Vorteile der großen Wafer mitnehmen. Die Leistungshalbleiter kommen in vielerlei Elektronik zum Einsatz – Von E-Autos,... [mehr]

Im vergangenen Jahr verkündete Infineon den Aufbau einer ersten Pilotlinie für die Herstellung von Leistungshalbleitern auf Basis von Galliumnitrid (GaN). Mit einer Fertigung mit Wafern in 300 mm will Infineon damit einerseits die technischen Vorteile dieser Leistungshalbleiter und andererseits auch die wirtschaftlichen Vorteile der großen Wafer mitnehmen. Die Leistungshalbleiter kommen in vielerlei Elektronik zum Einsatz – Von E-Autos,... [mehr] -

SF2P und SF2P+: Samsung spricht über Vorteile und Verzögerungen von SF1.4

Auf seinem SAFE Forum 2025 hat Samsung über einige Details seiner zukünftigen Fertigungsschritte gesprochen und nennt dabei Daten zu SF2P und SF2P+ sowie das, was danach kommen soll. Dies meldet ZDNET Korea. Nach dem Upgrade auf die zweite Generation des 2-nm-Prozesses namens SF2P soll die dritte Generation SF2P+ bereits im kommenden Jahr in die Produktion gehen. Zuletzt wurde gemutmaßt, dass Samsung womöglich die ersten größeren... [mehr]

Auf seinem SAFE Forum 2025 hat Samsung über einige Details seiner zukünftigen Fertigungsschritte gesprochen und nennt dabei Daten zu SF2P und SF2P+ sowie das, was danach kommen soll. Dies meldet ZDNET Korea. Nach dem Upgrade auf die zweite Generation des 2-nm-Prozesses namens SF2P soll die dritte Generation SF2P+ bereits im kommenden Jahr in die Produktion gehen. Zuletzt wurde gemutmaßt, dass Samsung womöglich die ersten größeren... [mehr] -

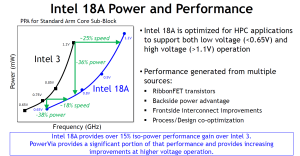

25 % schneller oder 36 % sparsamer: Intel vergleicht Intel 18A gegen Intel 3

Auf dem VLSI-Symposium in Japan hat Intel weitere Leistungsdaten zur ab der zweiten Jahreshälfte 2025 in die Massenproduktion übergehende Fertigung in Intel 18A präsentiert. Man könnte davon sprechen, dass Intel mit Intel 18A "All in" geht – zumindest wenn es um das Auftragsfertiger-Geschäft geht. Allerdings zeichnete sich zuletzt an, dass nicht Intel 18A, sondern wohl eher der Optimierungsschritt Intel 18A-P und der Nachfolger Intel 14A die... [mehr]

Auf dem VLSI-Symposium in Japan hat Intel weitere Leistungsdaten zur ab der zweiten Jahreshälfte 2025 in die Massenproduktion übergehende Fertigung in Intel 18A präsentiert. Man könnte davon sprechen, dass Intel mit Intel 18A "All in" geht – zumindest wenn es um das Auftragsfertiger-Geschäft geht. Allerdings zeichnete sich zuletzt an, dass nicht Intel 18A, sondern wohl eher der Optimierungsschritt Intel 18A-P und der Nachfolger Intel 14A die... [mehr] -

Mit EUV: Micron liefert ersten LPDDR5X mit 1γ-DRAM

Nachdem Micron Ende Februar dieses Jahres die Fertigung der ersten DRAM-Chips im neuen Fertigungsverfahren namens 1γ (1-gamma) begonnen hat, verkündet man nun die ersten LPDDR5X mit 10.700 MT/s ausgeliefert zu haben. Die sechste Generation der Fertigung von DRAM bei Micron hört auf den Namen 1γ (1-gamma) und befindet sich im Bereich einer 10-nm-Fertigung. Erstmals kommt hier eine Belichtung mittels EUV (Extreme Ultra Violet) zum... [mehr]

Nachdem Micron Ende Februar dieses Jahres die Fertigung der ersten DRAM-Chips im neuen Fertigungsverfahren namens 1γ (1-gamma) begonnen hat, verkündet man nun die ersten LPDDR5X mit 10.700 MT/s ausgeliefert zu haben. Die sechste Generation der Fertigung von DRAM bei Micron hört auf den Namen 1γ (1-gamma) und befindet sich im Bereich einer 10-nm-Fertigung. Erstmals kommt hier eine Belichtung mittels EUV (Extreme Ultra Violet) zum... [mehr] -

Anstatt TSMC: AMD soll I/O-Dies bei Samsung fertigen wollen

Laut eines Berichts von The Bell in Korea soll die Foundry-Abteilung von Samsung aktuell mit AMD in einer erweiterten Zusammenarbeit hinsichtlich der Fertigung neuer Chips sein. Konkret soll Samsung Test-Chips für AMD gefertigt haben, welche als I/O-Dies auf den zukünftigen EPYC-Prozessoren zum Einsatz kommen. Als Fertigungsgröße soll ein 4-nm-Prozess angedacht sein. Aktuell lässt AMD sowohl die I/O-Dies (IOD) wie auch die Chips mit den... [mehr]

Laut eines Berichts von The Bell in Korea soll die Foundry-Abteilung von Samsung aktuell mit AMD in einer erweiterten Zusammenarbeit hinsichtlich der Fertigung neuer Chips sein. Konkret soll Samsung Test-Chips für AMD gefertigt haben, welche als I/O-Dies auf den zukünftigen EPYC-Prozessoren zum Einsatz kommen. Als Fertigungsgröße soll ein 4-nm-Prozess angedacht sein. Aktuell lässt AMD sowohl die I/O-Dies (IOD) wie auch die Chips mit den... [mehr] -

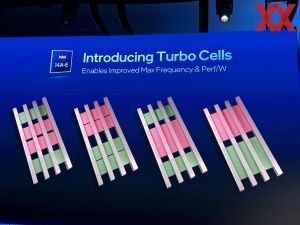

Intel 14A: Turbo Cells sollen den Taktturbo zünden

Mit Intel 18A und Intel 18A-P will Intel sowohl eigene Produkte als auch Chips für Kunden in einem der modernsten Fertigungsprozesse herstellen. Für den nächsten Schritt, Intel 14A, plant Intel zahlreiche Neuerungen – darunter die zweite Generation der RibbonFETs sowie PowerDirect als Weiterentwicklung der rückseitigen Stromversorgung PowerVia – und das alles unter Einsatz der High-NA-EUV-Lithografie. Mit Intel 14A möchte Intel neue... [mehr]

Mit Intel 18A und Intel 18A-P will Intel sowohl eigene Produkte als auch Chips für Kunden in einem der modernsten Fertigungsprozesse herstellen. Für den nächsten Schritt, Intel 14A, plant Intel zahlreiche Neuerungen – darunter die zweite Generation der RibbonFETs sowie PowerDirect als Weiterentwicklung der rückseitigen Stromversorgung PowerVia – und das alles unter Einsatz der High-NA-EUV-Lithografie. Mit Intel 14A möchte Intel neue... [mehr] -

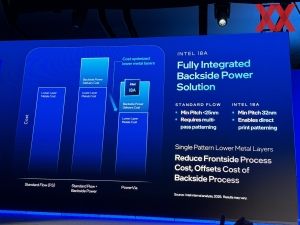

PowerVia: Die teure Technik soll sich letztendlich dennoch auszahlen

Mit der Fertigung in Intel 18A wird Intel erstmals auf das Backside Power Delivery Network (BSPDN) namens PowerVia setzen, über dessen Vor- und Nachteile wir seit der Ankündigung bereits vielfach berichtet haben. Auf der Direct-Connect-Konferenz sprachen Intel und die EDA-Partner nun über konkrete Details zur Kosteneinsparung sowie zu Leistungsverbesserungen im Design. Dass ein BSPDN nicht nur Vorteile mit sich bringt, wurde bereits mehrfach... [mehr]

Mit der Fertigung in Intel 18A wird Intel erstmals auf das Backside Power Delivery Network (BSPDN) namens PowerVia setzen, über dessen Vor- und Nachteile wir seit der Ankündigung bereits vielfach berichtet haben. Auf der Direct-Connect-Konferenz sprachen Intel und die EDA-Partner nun über konkrete Details zur Kosteneinsparung sowie zu Leistungsverbesserungen im Design. Dass ein BSPDN nicht nur Vorteile mit sich bringt, wurde bereits mehrfach... [mehr] -

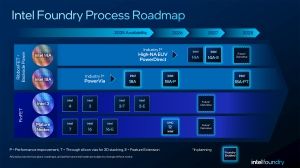

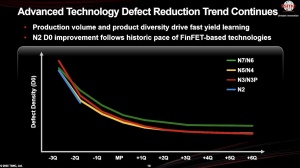

Intel 18A, 18A-P und 14A: Intel macht erste Angaben zur Leistung

Neben den ersten oder weiteren groben Details zu Intel 18A-P, Intel 18A-PT und Intel 14A machte Intel auf der Direct Connect 2025 auch konkretere Angaben zu den Leistungszielen und teilweise schon erreichten Zielen hinsichtlich der Leistung und Defektrate. Intel 18A wird gegenüber Intel 3 ein um mehr als 15 % höheres Performance/Watt-Verhältnis vorzuweisen haben. Die Transistordichte steigt um 30 % an. Diese groben Leistungsangaben sind... [mehr]

Neben den ersten oder weiteren groben Details zu Intel 18A-P, Intel 18A-PT und Intel 14A machte Intel auf der Direct Connect 2025 auch konkretere Angaben zu den Leistungszielen und teilweise schon erreichten Zielen hinsichtlich der Leistung und Defektrate. Intel 18A wird gegenüber Intel 3 ein um mehr als 15 % höheres Performance/Watt-Verhältnis vorzuweisen haben. Die Transistordichte steigt um 30 % an. Diese groben Leistungsangaben sind... [mehr] -

Foundry Direct Connect: Intel zu Intel 14A und Performance-Variante Intel 18A-P

Auf der Hausmesse Direct Connect kündigt Intel einige Neuerungen aus dem Foundry-Geschäft an. Einmal mehr liegt der Fokus dabei auf der etablierten Prozess-Technik, die in Form von Intel 18A bereits seit Jahren im Raum steht und durchaus gute Vorzeichen vorzuweisen hat. Aber auch beim Packaging will Intel ein Big Player für externe Kunden werden – ebenfalls etwas, was über die vergangenen Monate beinahe wie ein Mantra immer wiederholt... [mehr]

Auf der Hausmesse Direct Connect kündigt Intel einige Neuerungen aus dem Foundry-Geschäft an. Einmal mehr liegt der Fokus dabei auf der etablierten Prozess-Technik, die in Form von Intel 18A bereits seit Jahren im Raum steht und durchaus gute Vorzeichen vorzuweisen hat. Aber auch beim Packaging will Intel ein Big Player für externe Kunden werden – ebenfalls etwas, was über die vergangenen Monate beinahe wie ein Mantra immer wiederholt... [mehr] -

Technology Symposium 2025: TSMC ist bezüglich N2-Fertigung extrem zuversichtlich

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA aber bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden. In der Fertigung ein Fokus lag dabei auf N2 als nächster großer Schritt in der Fertigung. Zwar hat TSMC auch schon die Nachfolger A16 und A14... [mehr]

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA aber bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden. In der Fertigung ein Fokus lag dabei auf N2 als nächster großer Schritt in der Fertigung. Zwar hat TSMC auch schon die Nachfolger A16 und A14... [mehr] -

Intel ist weiterhin eine Option: Blackwell Ultra wird bereits in Arizona gefertigt

Für NVIDIA spielt China eine große Rolle: Einerseits, weil ein Teil der Fertigung der Systeme dort stattfindet und andererseits natürlich auch als Markt für die eigenen Produkte. Die zahlreiche Implikationen durch Handelsbeschränkungen, Strafzölle und Umgehung dieser soll an dieser Stelle aber keine Rolle spielen. Stattdessen wurde NVIDIA CEO Jensen Huang in einer Frage-und-Antwort-Runde auf der GTC gefragt, wie NVIDIA seine Investitionen... [mehr]

Für NVIDIA spielt China eine große Rolle: Einerseits, weil ein Teil der Fertigung der Systeme dort stattfindet und andererseits natürlich auch als Markt für die eigenen Produkte. Die zahlreiche Implikationen durch Handelsbeschränkungen, Strafzölle und Umgehung dieser soll an dieser Stelle aber keine Rolle spielen. Stattdessen wurde NVIDIA CEO Jensen Huang in einer Frage-und-Antwort-Runde auf der GTC gefragt, wie NVIDIA seine Investitionen... [mehr] -

Zusammenarbeit mit TSMC: Marvell demonstriert ersten in 2 nm gefertigten Chip

Marvell verkündet heute, dass man in Zusammenarbeit mit TSMC den ersten funktionsfähigen, in 2 nm gefertigten Chip hergestellt hat. Im Frühjahr 2024 verkündeten beide Unternehmen an einem entsprechenden Projekt zu arbeiten. Der von Marvell entwickelte Chip soll dabei in der KI- und Cloud-Infrastruktur zum Einsatz kommen – der IP-Domäne von Marvell. Zudem soll er Bestandteil eines Beschleuniger-Plattform (XPU) sein. Marvell entwickelt unter... [mehr]

Marvell verkündet heute, dass man in Zusammenarbeit mit TSMC den ersten funktionsfähigen, in 2 nm gefertigten Chip hergestellt hat. Im Frühjahr 2024 verkündeten beide Unternehmen an einem entsprechenden Projekt zu arbeiten. Der von Marvell entwickelte Chip soll dabei in der KI- und Cloud-Infrastruktur zum Einsatz kommen – der IP-Domäne von Marvell. Zudem soll er Bestandteil eines Beschleuniger-Plattform (XPU) sein. Marvell entwickelt unter... [mehr] -

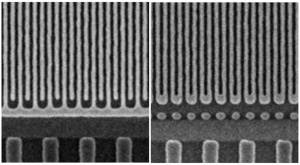

High-NA EUV: E-Tests bestätigen gute Weiterentwicklung bei Metallleitungsstrukturen

Das Forschungsinstitut imec informiert über erfolgreiche sogenannte E-Test-Ergebnisse in der High-NA-EUV-Lithografie für metallisierte Leitungsstrukturen mit einem Abstand von nur 20 nm. Diese Tests sind der nächste Schritt in der Entwicklung eines Fertigungs-Prozesses und in der Inbetriebnahme der High-NA-EUV-Scanner im gemeinsamen Forschungslabor von imec und ASML. Im Sommer des vergangenen Jahres vermeldete ASML, dass erstmals... [mehr]

Das Forschungsinstitut imec informiert über erfolgreiche sogenannte E-Test-Ergebnisse in der High-NA-EUV-Lithografie für metallisierte Leitungsstrukturen mit einem Abstand von nur 20 nm. Diese Tests sind der nächste Schritt in der Entwicklung eines Fertigungs-Prozesses und in der Inbetriebnahme der High-NA-EUV-Scanner im gemeinsamen Forschungslabor von imec und ASML. Im Sommer des vergangenen Jahres vermeldete ASML, dass erstmals... [mehr] -

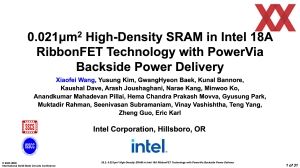

Intel 18A: Weitere Details die Hoffnung machen

Auf der International Solid-State Circuits Conference (ISSCC) zeigten zahlreiche Unternehmen aus der Halbleiterbranche ihre Weiter- und Neuentwicklungen aus den verschiedenen Bereichen. Dabei kommen auch immer wieder einige interessante Details zu Tage und aus dem Themenfeld der Fertigung sind dies einige Zahlen zu den Leistungsdaten der nächsten Fertigungsprozesse im Sub-2-nm-Bereich. Sowohl für TSMC wie auch Intel werden dies wichtige... [mehr]

Auf der International Solid-State Circuits Conference (ISSCC) zeigten zahlreiche Unternehmen aus der Halbleiterbranche ihre Weiter- und Neuentwicklungen aus den verschiedenen Bereichen. Dabei kommen auch immer wieder einige interessante Details zu Tage und aus dem Themenfeld der Fertigung sind dies einige Zahlen zu den Leistungsdaten der nächsten Fertigungsprozesse im Sub-2-nm-Bereich. Sowohl für TSMC wie auch Intel werden dies wichtige... [mehr] -

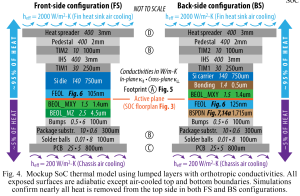

Thermische Hotspots: Backside Power Delivery hat nicht nur Vorteile

Eigentlich schon für den aus Kostengründen eingesparten Entwicklungsschritt Intel 20A geplant, wird PowerVia als rückseitige Stromversorgung der Transistoren in den Chips für Intel ab Intel 18A zu einem wichtigen Thema werden. Auch TSMC wird die Technik zum Einsatz bringen, allerdings erst ab der A16-Fertigung und auch Samsung hat mit SF2Z entsprechende Pläne in der Roadmap. Bei Intel als PowerVia bezeichnet, nennt TSMC die Technik Super Power... [mehr]

Eigentlich schon für den aus Kostengründen eingesparten Entwicklungsschritt Intel 20A geplant, wird PowerVia als rückseitige Stromversorgung der Transistoren in den Chips für Intel ab Intel 18A zu einem wichtigen Thema werden. Auch TSMC wird die Technik zum Einsatz bringen, allerdings erst ab der A16-Fertigung und auch Samsung hat mit SF2Z entsprechende Pläne in der Roadmap. Bei Intel als PowerVia bezeichnet, nennt TSMC die Technik Super Power... [mehr] -

ESMC-Chipfabrik: Finanzierungsmittel allesamt gesichert

Den symbolischen Spatenstich gab es bereits im August, doch erst vor dem vergangenen Wochenende hat das Bundesministerium für Wirtschaft und Klimaschutz (BMWK) verkündet, dass sämtliche Finanzierungsmittel für die ESMC-Chipfabrik nun genehmigt wurden, sodass die Finanzierung nun vollständig steht. Die European Semiconductor Manufacturing Company (ESMC) ist ein Joint Venture aus TSMC, Bosch, Infineon und NXP. Die gesamte Investitionssumme... [mehr]

Den symbolischen Spatenstich gab es bereits im August, doch erst vor dem vergangenen Wochenende hat das Bundesministerium für Wirtschaft und Klimaschutz (BMWK) verkündet, dass sämtliche Finanzierungsmittel für die ESMC-Chipfabrik nun genehmigt wurden, sodass die Finanzierung nun vollständig steht. Die European Semiconductor Manufacturing Company (ESMC) ist ein Joint Venture aus TSMC, Bosch, Infineon und NXP. Die gesamte Investitionssumme... [mehr] -

Foundry-Abspaltung noch nicht beschlossen: ES0 von Panther Lake bei Partnern

Im Rahmen der 22. Barclays Technology Conference sprachen die beiden Interim-CEOs von Intel David Zinsner und Michelle Johnston Holthaus über die aktuelle Situation und Herausforderungen bei Intel. Demnach konzentriert man sich weiterhin auf die Entwicklung neuer Produkte für Intel Products und neuer Fertigungstechnologien für Intel Foundry. Die Frage, ob es zu einer kompletten Abspaltung der Foundry-Sparte kommt, sehen Holthaus und... [mehr]

Im Rahmen der 22. Barclays Technology Conference sprachen die beiden Interim-CEOs von Intel David Zinsner und Michelle Johnston Holthaus über die aktuelle Situation und Herausforderungen bei Intel. Demnach konzentriert man sich weiterhin auf die Entwicklung neuer Produkte für Intel Products und neuer Fertigungstechnologien für Intel Foundry. Die Frage, ob es zu einer kompletten Abspaltung der Foundry-Sparte kommt, sehen Holthaus und... [mehr] -

Chipfertigung unverkäuflich: USA wollen nach Subventionen die Kontrolle behalten

In dieser Woche hat Intel 7,86 Milliarden US-Dollar aus dem US CHIPS Act erhalten und damit einher gehen auch einige Beschränkungen, falls Intel die inzwischen eigenständige Foundry-Sparte verkaufen oder an die Börse bringen möchte. In einem Schreiben an die US-Börsenaufsicht SEC werden die Bedingungen, an die die Förderungen geknüpft sind, deutlich.The Direct Funding Agreement contains restrictions on certain “change of control” transactions:... [mehr]

In dieser Woche hat Intel 7,86 Milliarden US-Dollar aus dem US CHIPS Act erhalten und damit einher gehen auch einige Beschränkungen, falls Intel die inzwischen eigenständige Foundry-Sparte verkaufen oder an die Börse bringen möchte. In einem Schreiben an die US-Börsenaufsicht SEC werden die Bedingungen, an die die Förderungen geknüpft sind, deutlich.The Direct Funding Agreement contains restrictions on certain “change of control” transactions:... [mehr] -

Wafer- und Chipfertigung: China stellt 1 Million Wafer her und YMTC belichtet knapp die Hälfte

Aktuelle Zahlen aus China sowie des japanischen Waferherstellers SUMCO ergeben ein neues Bild über den Umfang der Eigenständigkeit Chinas in der Chipfertigung. Inzwischen sollen chinesische Unternehmen in der Lage sein, rund eine Million Wafer selbst zu fertigen. Damit macht man sich weiter von westlichen Herstellern wie SUMCO unabhängig, was natürlich schlecht für deren Geschäft ist. Zu den weiteren Herstellern von Wafern... [mehr]

Aktuelle Zahlen aus China sowie des japanischen Waferherstellers SUMCO ergeben ein neues Bild über den Umfang der Eigenständigkeit Chinas in der Chipfertigung. Inzwischen sollen chinesische Unternehmen in der Lage sein, rund eine Million Wafer selbst zu fertigen. Damit macht man sich weiter von westlichen Herstellern wie SUMCO unabhängig, was natürlich schlecht für deren Geschäft ist. Zu den weiteren Herstellern von Wafern... [mehr] -

US CHIPS Act: Intel erhält final fast 8 Milliarden US-Dollar

Das lange Pokern hat nun endlich ein Ende gefunden und Intel erhält unter der Biden-Harris-Regierung 7,86 Milliarden US-Dollar aus dem US CHIPS Act. Ursprünglich geplant hatte Intel mit gut 500 Millionen Euro mehr, allerdings ist inzwischen auch eine Unterstützung in Höhe von drei Milliarden US-Dollar hinzugekommen, die Intel im Rahmen des Secure-Enclave-Programms erhält, welches eine lokale Lieferkette und Fertigung für eine... [mehr]

Das lange Pokern hat nun endlich ein Ende gefunden und Intel erhält unter der Biden-Harris-Regierung 7,86 Milliarden US-Dollar aus dem US CHIPS Act. Ursprünglich geplant hatte Intel mit gut 500 Millionen Euro mehr, allerdings ist inzwischen auch eine Unterstützung in Höhe von drei Milliarden US-Dollar hinzugekommen, die Intel im Rahmen des Secure-Enclave-Programms erhält, welches eine lokale Lieferkette und Fertigung für eine... [mehr] -

Zukunftstechnologien: Samsung eröffnet neuen Entwicklungskomplex

Samsung hat das Tool-in, also den Einbau des ersten Werkzeuges in seinem neuen Halbleiter-Forschungs- und Entwicklungskomplex (NRD-K) auf dem Giheung-Campus, groß gefeiert. Für das rund 14,4 Milliarden Euro teure Projekt, welches ab 2030 noch weiter ausgebaut werden soll. Mit der Einrichtung will Samsung die Entwicklung für Speicher, System-LSI und Foundry-Halbleiter vorantreiben. Der gesamte Komplex erstreckt sich über eine Fläche... [mehr]

Samsung hat das Tool-in, also den Einbau des ersten Werkzeuges in seinem neuen Halbleiter-Forschungs- und Entwicklungskomplex (NRD-K) auf dem Giheung-Campus, groß gefeiert. Für das rund 14,4 Milliarden Euro teure Projekt, welches ab 2030 noch weiter ausgebaut werden soll. Mit der Einrichtung will Samsung die Entwicklung für Speicher, System-LSI und Foundry-Halbleiter vorantreiben. Der gesamte Komplex erstreckt sich über eine Fläche... [mehr] -

Silicon Shield: TSMC darf nur auf Taiwan Chips in 2 nm fertigen

Es ist eine offenkundige Strategie seitens der Politik in Taiwan: TSMC ist inzwischen so wichtig für die Weltwirtschaft und den gesamten Chipmarkt, dass es die USA wohl kaum zulassen könnten, dass China sich den Auftragsfertiger einverleibt. Silicon Shield nennt sich diese Strategie. Nicht nur im Volumen an Chips, auch bei den fortschrittlichsten Fertigungstechnologien und dem Packaging ist das, was die Fabriken bei TSMC verlässt, das... [mehr]

Es ist eine offenkundige Strategie seitens der Politik in Taiwan: TSMC ist inzwischen so wichtig für die Weltwirtschaft und den gesamten Chipmarkt, dass es die USA wohl kaum zulassen könnten, dass China sich den Auftragsfertiger einverleibt. Silicon Shield nennt sich diese Strategie. Nicht nur im Volumen an Chips, auch bei den fortschrittlichsten Fertigungstechnologien und dem Packaging ist das, was die Fabriken bei TSMC verlässt, das... [mehr] -

300 mm Durchmesser und 20 µm dick: Infineon stellt extrem dünne Wafer her

Infineon hat die Herstellung und erste Nutzung von ultradünnen Wafern angekündigt, die auf eine Dicke von gerade einmal 20 µm kommen. Die Wafer haben den in der Halbleiterfertigung inzwischen üblichen Durchmesser von 300 mm. Mit einer Dicke von nur 20 µm stellen sie in der Fertigung und Handhabung in der Belichtung sowie der weiteren Verarbeitung eine besondere Herausforderung dar. Gemeinsam mit ersten Kunden will man diese jedoch gelöst haben... [mehr]

Infineon hat die Herstellung und erste Nutzung von ultradünnen Wafern angekündigt, die auf eine Dicke von gerade einmal 20 µm kommen. Die Wafer haben den in der Halbleiterfertigung inzwischen üblichen Durchmesser von 300 mm. Mit einer Dicke von nur 20 µm stellen sie in der Fertigung und Handhabung in der Belichtung sowie der weiteren Verarbeitung eine besondere Herausforderung dar. Gemeinsam mit ersten Kunden will man diese jedoch gelöst haben... [mehr] -

Galliumnitrid auf 300 mm: Infineon fertigt Leistungshalbleiter effizienter

Auch wenn sich in unserem Themenfeld vieles oder nahezu alles auf die Siliziumchips konzentriert, so kommen die meisten Menschen in ihrem alltäglichen Umfeld ohne Leistungshalbleiter nicht mehr weit – sei es im E-Auto, diversen Netzteilen, Solarwechselrichter und vielem mehr. Die Leistungshalbleiter werden in Siliziumkarbid (SiC) oder Galliumnitrid (GaN) gefertigt und entsprechend konzentrieren sich Firmen, die solche Bauteile... [mehr]

Auch wenn sich in unserem Themenfeld vieles oder nahezu alles auf die Siliziumchips konzentriert, so kommen die meisten Menschen in ihrem alltäglichen Umfeld ohne Leistungshalbleiter nicht mehr weit – sei es im E-Auto, diversen Netzteilen, Solarwechselrichter und vielem mehr. Die Leistungshalbleiter werden in Siliziumkarbid (SiC) oder Galliumnitrid (GaN) gefertigt und entsprechend konzentrieren sich Firmen, die solche Bauteile... [mehr] -

Granite Ridge und Strix Point: AMD macht Angaben zur Chipgröße

Im Nachgang der Berichterstattung zum Zen-5-Tech-Day bzw. unserem ausführlichen Artikel dazu hatten wir noch einige Fragen an AMD, die nun beantwortet wurden. Uns interessierte hier vor allem das Thema der Fertigung. Sowohl für die Ryzen-AI-300- wie auch Ryzen-9000-Prozessoren (bzw. die der CCDs mit den Zen-5-Kernen) setzt AMD auf eine Fertigung in 4 nm bei TSMC (N4P und N4X). Doch welchen Einfluss hat der Wechsel auf die neuen... [mehr]

Im Nachgang der Berichterstattung zum Zen-5-Tech-Day bzw. unserem ausführlichen Artikel dazu hatten wir noch einige Fragen an AMD, die nun beantwortet wurden. Uns interessierte hier vor allem das Thema der Fertigung. Sowohl für die Ryzen-AI-300- wie auch Ryzen-9000-Prozessoren (bzw. die der CCDs mit den Zen-5-Kernen) setzt AMD auf eine Fertigung in 4 nm bei TSMC (N4P und N4X). Doch welchen Einfluss hat der Wechsel auf die neuen... [mehr] -

Bericht und Analyse: Intel erläutert was hinter der Fertigung in Intel 3 steckt

Im vergangenen Jahr veröffentlichte Intel zur Eröffnung der Fab 34 im irischen Leixlip einige Details zur Fertigung in Intel 4, die dort in der Folge stattgefunden hat. Auf dem VLSI Symposium sprach Intel nun über Intel 3, den nächsten Schritt in der eigenen Fertigung. Intel 3 kommt vor allem für die Xeon-6-Prozessoren zum Einsatz – sprich die reinen E-Kern-Modelle alias Sierra Forest und die klassischen P-Kern-Modelle Granite Rapids. Für... [mehr]

Im vergangenen Jahr veröffentlichte Intel zur Eröffnung der Fab 34 im irischen Leixlip einige Details zur Fertigung in Intel 4, die dort in der Folge stattgefunden hat. Auf dem VLSI Symposium sprach Intel nun über Intel 3, den nächsten Schritt in der eigenen Fertigung. Intel 3 kommt vor allem für die Xeon-6-Prozessoren zum Einsatz – sprich die reinen E-Kern-Modelle alias Sierra Forest und die klassischen P-Kern-Modelle Granite Rapids. Für... [mehr] -

Intel 3-E und Intel 3-PT: Die weiteren Verbesserungen der 3-nm-Familie

Neben den Erläuterungen zu den Verbesserungen in Intel 3 – wie sie für Sierra Forest und Granite Rapids zum Einsatz kommen – sprach Intel auf dem VLSI Symposium 2024 über die Erweiterungen der Intel-3-Familie, wie man sie Anfang des Jahres vorstellte. Konkret sind die Intel 3-T, Intel 3-E und Intel 3-PT. In der Basis bietet Intel 3 eine um 18 % höhere ISO-Power – sprich bei gleicher Leistungsaufnahme kann die Leistung des Chips um 18 %... [mehr]

Neben den Erläuterungen zu den Verbesserungen in Intel 3 – wie sie für Sierra Forest und Granite Rapids zum Einsatz kommen – sprach Intel auf dem VLSI Symposium 2024 über die Erweiterungen der Intel-3-Familie, wie man sie Anfang des Jahres vorstellte. Konkret sind die Intel 3-T, Intel 3-E und Intel 3-PT. In der Basis bietet Intel 3 eine um 18 % höhere ISO-Power – sprich bei gleicher Leistungsaufnahme kann die Leistung des Chips um 18 %... [mehr] -

Samsung Foundry: SF2Z kommt mit BSPDN, SF3 mit GAA startet dieses Jahr und SF4U für hohe Volumina

Auf dem Samsung Foundry Forum hat der südkoreanische Großkonzern und Chiphersteller einige Details zu seinen Plänen hinsichtlich der Fertigung in den kommenden Jahren verkündet. Unter anderem wurden zwei neue Prozess-Nodes SF2Z und SF4U angekündigt. Mit SF2Z wird Samsung auf ein Backside Power Delivery Network (BSPDN) setzen. Bei Intel wird man diesen Schritt mit Intel 20A gehen und TSMC hat seine Pläne für eine BSPDN-Technik auf die... [mehr]

Auf dem Samsung Foundry Forum hat der südkoreanische Großkonzern und Chiphersteller einige Details zu seinen Plänen hinsichtlich der Fertigung in den kommenden Jahren verkündet. Unter anderem wurden zwei neue Prozess-Nodes SF2Z und SF4U angekündigt. Mit SF2Z wird Samsung auf ein Backside Power Delivery Network (BSPDN) setzen. Bei Intel wird man diesen Schritt mit Intel 20A gehen und TSMC hat seine Pläne für eine BSPDN-Technik auf die... [mehr] -

0,75 High-NA und Hyper-NA EUV: ASML zeigt neue Roadmap für EUV-Systeme

EUV-Belichtung mit High Numerical Aperture – oder kurz High-NA – wird in den kommenden Jahren die aus Sicht der Optik einer Wafer-Belichtung entscheidende Technologie sein. ASML hat inzwischen zwei Systeme als TWINSCAN NXE:5000, eines an Intel und eines für interne Forschungszwecke, fertiggestellt, bzw. ausgeliefert. Auch wenn 0,55 High-NA EUV erst ab 2025/26 eine wichtige Rolle spielen wird, die darauffolgenden Jahre werden alle neue... [mehr]

EUV-Belichtung mit High Numerical Aperture – oder kurz High-NA – wird in den kommenden Jahren die aus Sicht der Optik einer Wafer-Belichtung entscheidende Technologie sein. ASML hat inzwischen zwei Systeme als TWINSCAN NXE:5000, eines an Intel und eines für interne Forschungszwecke, fertiggestellt, bzw. ausgeliefert. Auch wenn 0,55 High-NA EUV erst ab 2025/26 eine wichtige Rolle spielen wird, die darauffolgenden Jahre werden alle neue... [mehr]