News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

N2

-

2 nm auf 5 nm: Broadcom liefert erstes 3.5D-XDSiP-Design an Fujitsu

Broadcom gibt bekannt, dass man den ersten in 2 nm gefertigten Chip ausgeliefert hat. Die Lösung, bei der es sich vermutlich um den Monaka als Testchip für den späteren Monaka-X für den Supercomputer FugakuNEXT handelt, wurde an Fujitsu geliefert. Damit sind es nicht AMD, Apple oder NVIDIA, die einen solchen Chip offiziell in Dienst stellen, sondern eben Broadcom. Der Monaka ist ein Armv9-A-Design mit SVE2-Erweiterungen. Pro Sockel... [mehr]

Broadcom gibt bekannt, dass man den ersten in 2 nm gefertigten Chip ausgeliefert hat. Die Lösung, bei der es sich vermutlich um den Monaka als Testchip für den späteren Monaka-X für den Supercomputer FugakuNEXT handelt, wurde an Fujitsu geliefert. Damit sind es nicht AMD, Apple oder NVIDIA, die einen solchen Chip offiziell in Dienst stellen, sondern eben Broadcom. Der Monaka ist ein Armv9-A-Design mit SVE2-Erweiterungen. Pro Sockel... [mehr] -

Zen-6-CCD mit 12 Kernen und 48 MB L3-Cache: Nur 7 % größere Chipfläche bei insgesamt 76 mm²

Leaker @9550pro liefert die vermeintliche Die-Größe der nächsten Ryzen-Generation alias Olympic Ridge oder Medusa Ridge. Diese wird genau wie die kommenden Epyc-Prozessoren auf bei TSMC in N2 gefertigte CCDs mit 12 Kernen setzen. Die Anzahl der Kerne je CCD steigt also von 8 auf 12 um 50 % und um eben diese 50 % beträgt auch das Plus beim L3-Cache, der dann 48 MB groß sein soll. Die Fläche von 76 mm² wäre beeindruckend, denn damit... [mehr]

Leaker @9550pro liefert die vermeintliche Die-Größe der nächsten Ryzen-Generation alias Olympic Ridge oder Medusa Ridge. Diese wird genau wie die kommenden Epyc-Prozessoren auf bei TSMC in N2 gefertigte CCDs mit 12 Kernen setzen. Die Anzahl der Kerne je CCD steigt also von 8 auf 12 um 50 % und um eben diese 50 % beträgt auch das Plus beim L3-Cache, der dann 48 MB groß sein soll. Die Fläche von 76 mm² wäre beeindruckend, denn damit... [mehr] -

Foundry-Gerüchteküche: AMD soll Samsung und Intel Foundry in Anspruch nehmen

Über das Wochenende gab es eine Reihe (teilweiser wilder) Gerüchte zur Fertigung zukünftiger Chips von AMD. Das koreanische Branchenmagazin Seoul Economic Daily, dass AMD derzeit Pläne habe, ein Chipdesign in 2 nm bei Samsung fertigen zu lassen. In einem ersten Schritt sollen dazu Multi-Project Wafer (MPW) gefertigt werden. Auf diesen können Kunden (auch mehrere gleichzeitig) ihre Designs oder einzelne Funktionen eines Chipdesigns... [mehr]

Über das Wochenende gab es eine Reihe (teilweiser wilder) Gerüchte zur Fertigung zukünftiger Chips von AMD. Das koreanische Branchenmagazin Seoul Economic Daily, dass AMD derzeit Pläne habe, ein Chipdesign in 2 nm bei Samsung fertigen zu lassen. In einem ersten Schritt sollen dazu Multi-Project Wafer (MPW) gefertigt werden. Auf diesen können Kunden (auch mehrere gleichzeitig) ihre Designs oder einzelne Funktionen eines Chipdesigns... [mehr] -

Advanced Silicon, Stacking und Packaging: TSMC baut weiter auf drei Säulen

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt bzw. detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag... [mehr]

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt bzw. detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag... [mehr] -

TSMC N2: MediaTek gibt Tape-Out von SoC bekannt

Per Pressemitteilung gibt MediaTek bekannt, dass man den Tape-Out eines SoC in 2 nm bei TSMC vollzogen hat. Bisher liegt die Pressemitteilung nur in chinesischer Sprache vor und dennoch ist diese für MediaTek und TSMC zugleich bedeutend. Im Frühjahr haben AMD und TSMC den Tape-Out der CCDs mit Zen-6-Kernen gefeiert. Beim Chip von MediaTek handelt es sich um einen neuen SoC, vermeintlich den Dimensity 9600. Der Vorgänger Dimensity 9500... [mehr]

Per Pressemitteilung gibt MediaTek bekannt, dass man den Tape-Out eines SoC in 2 nm bei TSMC vollzogen hat. Bisher liegt die Pressemitteilung nur in chinesischer Sprache vor und dennoch ist diese für MediaTek und TSMC zugleich bedeutend. Im Frühjahr haben AMD und TSMC den Tape-Out der CCDs mit Zen-6-Kernen gefeiert. Beim Chip von MediaTek handelt es sich um einen neuen SoC, vermeintlich den Dimensity 9600. Der Vorgänger Dimensity 9500... [mehr] -

Wirbel bei TSMC: Geschäftsgeheimnisse abgeflossen und Fake News zu Milliardeninvestitionen

In den vergangenen Tagen gab es bei TSMC aus gleich zweierlei Richtungen großen Wirbel und auch einen handfesten Skandal rund um gestohlene Geschäftsgeheimnisse. Aufgrund der Brisanz und Wichtigkeit von TSMC als Unternehmen in Taiwan sind die örtlichen Online- und Fernsehmedien voll mit Meldungen zur Weitergabe von internen Informationen. Im Homeoffice tätig, sollen mehrere Verdächtige auf interne Dokumente zur Fertigung in 2 nm... [mehr]

In den vergangenen Tagen gab es bei TSMC aus gleich zweierlei Richtungen großen Wirbel und auch einen handfesten Skandal rund um gestohlene Geschäftsgeheimnisse. Aufgrund der Brisanz und Wichtigkeit von TSMC als Unternehmen in Taiwan sind die örtlichen Online- und Fernsehmedien voll mit Meldungen zur Weitergabe von internen Informationen. Im Homeoffice tätig, sollen mehrere Verdächtige auf interne Dokumente zur Fertigung in 2 nm... [mehr] -

Chipfertigung: Intel 18A bei 70 % Ausbeute, Zen 6 in N2-Derivaten

Aus verschiedenen Quellen gibt es Wasserstandsmeldungen rund um den Zustand der Fertigung für zukünftige Chips von AMD und Intel. Während diese mit vermeintlichen Daten zu Panther Lake aber ein Produkt beschreiben, welches schon in wenigen Monaten auf den Markt kommen wird, schauen die Meldungen zur Fertigung der Zen-6-Chiplets noch etwas weiter in die Zukunft. Die für gewöhnlich gut informierte Quelle Kepler_L2, bei X und im Anandtech-Forum... [mehr]

Aus verschiedenen Quellen gibt es Wasserstandsmeldungen rund um den Zustand der Fertigung für zukünftige Chips von AMD und Intel. Während diese mit vermeintlichen Daten zu Panther Lake aber ein Produkt beschreiben, welches schon in wenigen Monaten auf den Markt kommen wird, schauen die Meldungen zur Fertigung der Zen-6-Chiplets noch etwas weiter in die Zukunft. Die für gewöhnlich gut informierte Quelle Kepler_L2, bei X und im Anandtech-Forum... [mehr] -

In TSMC N2: Nova Lake soll Tape Out geschafft haben

Wie SemiAccurate berichtet, soll ein zukünftiges Produkt, bzw. ein dazugehöriger Chip bei Intel vor wenigen Wochen den wichtigen Meilenstein des Tape Out geschafft haben. Der Tape Out bezeichnet den finalen Schritt im Chipdesign, bei dem das vollständige Layout eines Chips zur Fertigung freigegeben wird. Es ist der Moment, in dem das Design an die Halbleiterfertigung übergeben wird, um Fotomasken für die Chipproduktion zu erstellen. Der... [mehr]

Wie SemiAccurate berichtet, soll ein zukünftiges Produkt, bzw. ein dazugehöriger Chip bei Intel vor wenigen Wochen den wichtigen Meilenstein des Tape Out geschafft haben. Der Tape Out bezeichnet den finalen Schritt im Chipdesign, bei dem das vollständige Layout eines Chips zur Fertigung freigegeben wird. Es ist der Moment, in dem das Design an die Halbleiterfertigung übergeben wird, um Fotomasken für die Chipproduktion zu erstellen. Der... [mehr] -

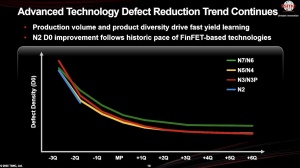

Technology Symposium 2025: TSMC ist bezüglich N2-Fertigung extrem zuversichtlich

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA aber bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden. In der Fertigung ein Fokus lag dabei auf N2 als nächster großer Schritt in der Fertigung. Zwar hat TSMC auch schon die Nachfolger A16 und A14... [mehr]

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA aber bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden. In der Fertigung ein Fokus lag dabei auf N2 als nächster großer Schritt in der Fertigung. Zwar hat TSMC auch schon die Nachfolger A16 und A14... [mehr] -

AMD EPYC Venice: AMD und TSMC zeigen in N2 gefertigten CCD mit Zen-6-Kernen

Aktuell bereist AMD-CEO Lisa Su Taiwan, um unter anderem TSMC, einen der zentralen Fertigungspartner, zu treffen. Im Rahmen eines gemeinsamen Events wurde bestätigt, dass die CCDs der kommenden EPYC-Generation "Venice" (Zen 6) im 2-nm-Prozess (N2) mit GAA-Nanosheet-Transistoren gefertigt werden. Laut AMD und TSMC zählen die Zen-6-basierten CCDs zu den ersten HPC-Dies, die im N2-Node in die Serienproduktion überführt werden. Die N2-Fertigung... [mehr]

Aktuell bereist AMD-CEO Lisa Su Taiwan, um unter anderem TSMC, einen der zentralen Fertigungspartner, zu treffen. Im Rahmen eines gemeinsamen Events wurde bestätigt, dass die CCDs der kommenden EPYC-Generation "Venice" (Zen 6) im 2-nm-Prozess (N2) mit GAA-Nanosheet-Transistoren gefertigt werden. Laut AMD und TSMC zählen die Zen-6-basierten CCDs zu den ersten HPC-Dies, die im N2-Node in die Serienproduktion überführt werden. Die N2-Fertigung... [mehr] -

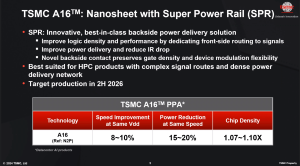

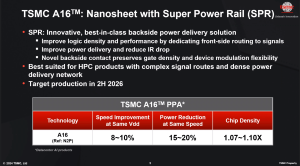

TSMC 2024 Technology Symposium: N2-Familie enthält NanoFlex für mehr Zellflexibilität

Neben der Vorstellung der ersten Umsetzung eines Back Side Power Delivery Network (BSPDN) in der A16-Fertigung verkündet TSMC laut Anandtech auf dem 2024 Technology Symposium deutliche Verbesserungen für die geplanten N2-Fertigungsschritte, die mittels NanoFlex-Technologie deutlich effizienter werden sollen. Alle bisher geplanten N2-Fertigungsschritte (N2, N2P, N2X) werden NanoFlex unterstützen. Dabei handelt es sich um eine Technologie,... [mehr]

Neben der Vorstellung der ersten Umsetzung eines Back Side Power Delivery Network (BSPDN) in der A16-Fertigung verkündet TSMC laut Anandtech auf dem 2024 Technology Symposium deutliche Verbesserungen für die geplanten N2-Fertigungsschritte, die mittels NanoFlex-Technologie deutlich effizienter werden sollen. Alle bisher geplanten N2-Fertigungsschritte (N2, N2P, N2X) werden NanoFlex unterstützen. Dabei handelt es sich um eine Technologie,... [mehr] -

Planänderung: TSMC verschiebt BSPDN auf die A16-Fertigung

Auf seinem 2024 Technology Symposium hat TSMC ein Update zu seinen Fertigungsplänen gegeben. Anandtech berichtet über die Neuerungen von einem der ersten Stops des Symposiums in Santa Clara. Trotz aktueller Vormachtstellung in der Wafer-Belichtung sowie dem Packaging (vor allem im Hinblick auf das Auftragsvolumen) gibt man sich wie immer recht zurückhaltend was neue Fertigungsgrößen und Technologien betrifft. Erstmals von TSMC offiziell... [mehr]

Auf seinem 2024 Technology Symposium hat TSMC ein Update zu seinen Fertigungsplänen gegeben. Anandtech berichtet über die Neuerungen von einem der ersten Stops des Symposiums in Santa Clara. Trotz aktueller Vormachtstellung in der Wafer-Belichtung sowie dem Packaging (vor allem im Hinblick auf das Auftragsvolumen) gibt man sich wie immer recht zurückhaltend was neue Fertigungsgrößen und Technologien betrifft. Erstmals von TSMC offiziell... [mehr] -

IEDM 2023: TSMC zeigt erstmals was nach N2 geplant ist

Bereits mit dem ersten Tag des diesjährigen IEEE International Electron Devices Meeting (IEDM 2023) haben wir über die Bemühungen von Intel und TSMC hinsichtlich der Materialforschung gesprochen, um Strukturbreiten von 2 nm und weniger in der Fertigung zu erreichen. Fokus der diesjährigen Konferenz ist aber sicherlich das Thema Backside Power Delivery Networks (BSPDN) – auch dazu hatten wir einen ausführlichen Bericht. In einem... [mehr]

Bereits mit dem ersten Tag des diesjährigen IEEE International Electron Devices Meeting (IEDM 2023) haben wir über die Bemühungen von Intel und TSMC hinsichtlich der Materialforschung gesprochen, um Strukturbreiten von 2 nm und weniger in der Fertigung zu erreichen. Fokus der diesjährigen Konferenz ist aber sicherlich das Thema Backside Power Delivery Networks (BSPDN) – auch dazu hatten wir einen ausführlichen Bericht. In einem... [mehr] -

N2 ab 2025: TSMC bekräftigt aktuelle Entwicklung

Auf dem Technology Symposium in Nordamerika (via Anandtech) hat TSMC über die aktuelle Entwicklung und die Pläne hinsichtlich seiner N2-Familie, also der Fertigung in 2 nm, gesprochen. Die Varianten der N2-Fertigung sollen 2025 bzw. 2026 die ersten fertigen Chips abwerfen. Bisher hatte TSMC nur seine N3-Familie detaillierter ausgeführt, während die Fertigung in N2 noch mehr oder weniger nur ein Ausblick war. Für die gesamte N2-Familie... [mehr]

Auf dem Technology Symposium in Nordamerika (via Anandtech) hat TSMC über die aktuelle Entwicklung und die Pläne hinsichtlich seiner N2-Familie, also der Fertigung in 2 nm, gesprochen. Die Varianten der N2-Fertigung sollen 2025 bzw. 2026 die ersten fertigen Chips abwerfen. Bisher hatte TSMC nur seine N3-Familie detaillierter ausgeführt, während die Fertigung in N2 noch mehr oder weniger nur ein Ausblick war. Für die gesamte N2-Familie... [mehr] -

TSMC: Fünf Fertigungsstufen in 3 nm und FinFlex für mehr Flexibilität

Auf dem Technology Symposium 2022 hat TSMC seine Roadmap für die Fertigung in den kommenden drei Jahren offengelegt. Für diese wird der Grundbaustein die Fertigung in 3 nm sein. Um auf die Anforderungen der Kunden besser eingehen zu können und die Wegstrecke bis zur Nutzung von Nanosheets überbrücken zu können, wird es neben N3 noch vier weitere Fertigungsschritte in der 3-nm-Klasse geben. Eine moderne Fertigung wird immer komplexer... [mehr]

Auf dem Technology Symposium 2022 hat TSMC seine Roadmap für die Fertigung in den kommenden drei Jahren offengelegt. Für diese wird der Grundbaustein die Fertigung in 3 nm sein. Um auf die Anforderungen der Kunden besser eingehen zu können und die Wegstrecke bis zur Nutzung von Nanosheets überbrücken zu können, wird es neben N3 noch vier weitere Fertigungsschritte in der 3-nm-Klasse geben. Eine moderne Fertigung wird immer komplexer... [mehr]