News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

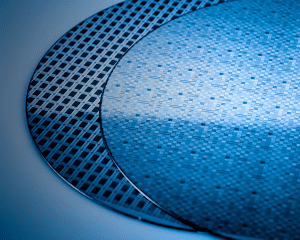

TSMC

-

Mehr CPUs statt SoCs: AMD übernimmt freie N4/N5-Kapazitäten

AMDs letzte Quartalszahlen sowie die eigene Einschätzung des Unternehmens sehen CPUs wieder im Kommen. Sie sollen mehr als nur der Host-Prozessor in einem KI-System sein, sondern vermehrt auch wieder die eigentlichen Rechenaufgaben übernehmen. Ein Problem für AMD ist allerdings, dass man hinsichtlich der Fertigungskapazitäten eingeschränkt ist und die Stückzahlen nicht in dem Maße hochgefahren werden können. Dem zu Pass kommt nun die Meldung,... [mehr]

AMDs letzte Quartalszahlen sowie die eigene Einschätzung des Unternehmens sehen CPUs wieder im Kommen. Sie sollen mehr als nur der Host-Prozessor in einem KI-System sein, sondern vermehrt auch wieder die eigentlichen Rechenaufgaben übernehmen. Ein Problem für AMD ist allerdings, dass man hinsichtlich der Fertigungskapazitäten eingeschränkt ist und die Stückzahlen nicht in dem Maße hochgefahren werden können. Dem zu Pass kommt nun die Meldung,... [mehr] -

Für Kamerasensoren: Sony und TSMC verkünden Partnerschaft

Sony und TSMC haben eine Absichtserklärung verkündet, nach der es ein Joint Venture beider Unternehmen geben soll, das sich mit der Entwicklung und Fertigung der Bildsensoren der nächsten Generation beschäftigt. Einen Namen hat das Joint Venture nocht nicht, bekannt ist aber, dass Sony die Leistung übernehmen wird. Eine Zusammenarbeit zwischen Sony und TSMC ist indes keine wirkliche Neuigkeit. Bereits 2021 gegründet wurde Japan Advanced... [mehr]

Sony und TSMC haben eine Absichtserklärung verkündet, nach der es ein Joint Venture beider Unternehmen geben soll, das sich mit der Entwicklung und Fertigung der Bildsensoren der nächsten Generation beschäftigt. Einen Namen hat das Joint Venture nocht nicht, bekannt ist aber, dass Sony die Leistung übernehmen wird. Eine Zusammenarbeit zwischen Sony und TSMC ist indes keine wirkliche Neuigkeit. Bereits 2021 gegründet wurde Japan Advanced... [mehr] -

Apple und Intel: Intel könnte bald wieder Chips für Cupertino fertigen

Etwa sechs Jahre nach dem Start von Apple Silicon könnte Intel wieder eine Rolle in Apples Hardware-Strategie spielen. Dieses Mal geht es allerdings nicht um eine Rückkehr klassischer Intel-CPUs in Apple-eigene Geräte wie dem MacBook, iMac oder den Mac mini. Einem Bericht von Bloomberg zufolge soll Apple erste Gespräche mit Intel über die Fertigung eigener Chips geführt haben. Auch Samsung Electronics sei im Gespräch. Konkrete... [mehr]

Etwa sechs Jahre nach dem Start von Apple Silicon könnte Intel wieder eine Rolle in Apples Hardware-Strategie spielen. Dieses Mal geht es allerdings nicht um eine Rückkehr klassischer Intel-CPUs in Apple-eigene Geräte wie dem MacBook, iMac oder den Mac mini. Einem Bericht von Bloomberg zufolge soll Apple erste Gespräche mit Intel über die Fertigung eigener Chips geführt haben. Auch Samsung Electronics sei im Gespräch. Konkrete... [mehr] -

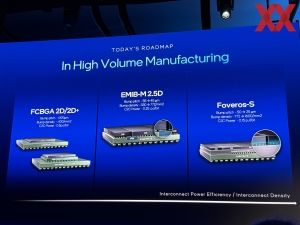

N2U, A13, A12 und immer größere Packages: TSMC auf dem 2026 Technology Symposium

TSMC hat zu seinem 2026 Technology Symposium Neuigkeiten im Bereich der Chipfertigung und dem Packaging verraten. In den kommenden Wochen und Monaten wird TSMC im Rahmen des Symposiums in verschiedenen Städten in den USA, Europa und Asien Halt machen. Die großen Profiteure des KI-Booms heißen nicht nur NVIDIA, AMD, Intel sowie die weiteren Hardware-Hersteller oder sind KI-Infrastrukturanbieter, sondern auch TSMC, denn irgendwo müssen die Chips... [mehr]

TSMC hat zu seinem 2026 Technology Symposium Neuigkeiten im Bereich der Chipfertigung und dem Packaging verraten. In den kommenden Wochen und Monaten wird TSMC im Rahmen des Symposiums in verschiedenen Städten in den USA, Europa und Asien Halt machen. Die großen Profiteure des KI-Booms heißen nicht nur NVIDIA, AMD, Intel sowie die weiteren Hardware-Hersteller oder sind KI-Infrastrukturanbieter, sondern auch TSMC, denn irgendwo müssen die Chips... [mehr] -

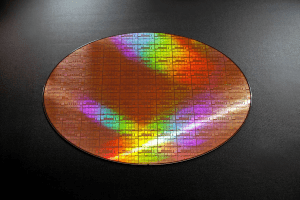

Quartalszahlen: TSMC liefert mehr Wafer denn je

TSMC hat seine Vormachtstellung bei den Halbleiterherstellern unterstrichen und vermeldet für das erste Quartal 2026 weiterhin extrem hohe Umsätze und Gewinne. Mit 4,17 Millionen Wafern (300 mm Äquivalent) wurde mehr Chipfläche denn je belichtet. In den vergangenen drei Monaten erreichte TSMC einen Umsatz in Höhe von 35,9 Milliarden US-Dollar. Der Nettogewinn lag bei 18,1 Milliarden US-Dollar. TSMC verdient kräftig, es wird aber... [mehr]

TSMC hat seine Vormachtstellung bei den Halbleiterherstellern unterstrichen und vermeldet für das erste Quartal 2026 weiterhin extrem hohe Umsätze und Gewinne. Mit 4,17 Millionen Wafern (300 mm Äquivalent) wurde mehr Chipfläche denn je belichtet. In den vergangenen drei Monaten erreichte TSMC einen Umsatz in Höhe von 35,9 Milliarden US-Dollar. Der Nettogewinn lag bei 18,1 Milliarden US-Dollar. TSMC verdient kräftig, es wird aber... [mehr] -

Quad-Die-Package: NVIDIA und TSMC sollen Probleme mit CoWoS-L für Rubin Ultra haben

NVIDIAs aktueller Fahrplan in den kommenden Jahren sieht wie folgt aus: Ab dem zweiten Halbjahr 2026 soll die Rubin-Generation ausgeliefert werden. Das dazugehörige Package besteht aus zwei Rubin-GPUs, die per NVLink-C2C miteinander verbunden sind. Hinzu kommen acht HBM4-Chips. Bis auf die HBM-Version ist dies identisch mit der aktuellen Blackwell-Generation. Mit Rubin Ultra will NVIDIA dann zwei bereits verbundene Rubin-Ultra-GPUs auf... [mehr]

NVIDIAs aktueller Fahrplan in den kommenden Jahren sieht wie folgt aus: Ab dem zweiten Halbjahr 2026 soll die Rubin-Generation ausgeliefert werden. Das dazugehörige Package besteht aus zwei Rubin-GPUs, die per NVLink-C2C miteinander verbunden sind. Hinzu kommen acht HBM4-Chips. Bis auf die HBM-Version ist dies identisch mit der aktuellen Blackwell-Generation. Mit Rubin Ultra will NVIDIA dann zwei bereits verbundene Rubin-Ultra-GPUs auf... [mehr] -

GTC 2026: Groq LPU erhielt gegenüber Rubin CPX den Vorzug

Gemeinsam mit der Rubin-Plattform stellte NVIDIA auf der GTC 2026 die Groq 3 LPU 3 als zusätzlichen Beschleuniger vor, der dafür sorgen soll, dass auch bei großen Modellen und Kontextfenstern noch ein effizientes Inferencing möglich ist. Für die Rubin-Generation ist dies der LP30-Chip (Groq 3). Mit Rubin Ultra soll dann schon der auf NVFP4 optimierte LP35 folgen. Im vergangenen Jahr stellte NVIDIA mit dem Rubin CPX einen eigenen Beschleuniger... [mehr]

Gemeinsam mit der Rubin-Plattform stellte NVIDIA auf der GTC 2026 die Groq 3 LPU 3 als zusätzlichen Beschleuniger vor, der dafür sorgen soll, dass auch bei großen Modellen und Kontextfenstern noch ein effizientes Inferencing möglich ist. Für die Rubin-Generation ist dies der LP30-Chip (Groq 3). Mit Rubin Ultra soll dann schon der auf NVFP4 optimierte LP35 folgen. Im vergangenen Jahr stellte NVIDIA mit dem Rubin CPX einen eigenen Beschleuniger... [mehr] -

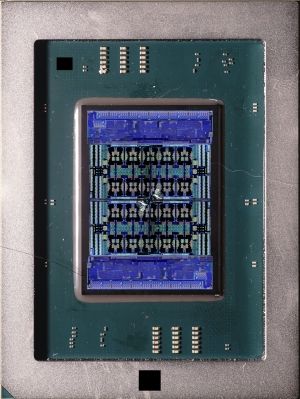

NVIDIA GB10: Fertigung in 3 nm braucht mehr Platz als in 5 nm

Kurnal hat Die-Shots und die dazugehörigen Beschriftungen zum GB10-SoC von NVIDIA veröffentlicht. Diesen hat MediaTek gemeinsam mit NVIDIA entwickelt – MediaTek zeichnet sich für den CPU-Chiplet verantwortlich und NVIDIA hat den GPU-Chiplet beigesteuert. Viele Details zum GB10-SoC hat NVIDIA zur Hot-Chips-Konferenz im vergangenen Sommer veröffentlicht. Was die Analyse von Kurnal und Vergleiche durch SemiAnalysis nun offenbaren, ist der... [mehr]

Kurnal hat Die-Shots und die dazugehörigen Beschriftungen zum GB10-SoC von NVIDIA veröffentlicht. Diesen hat MediaTek gemeinsam mit NVIDIA entwickelt – MediaTek zeichnet sich für den CPU-Chiplet verantwortlich und NVIDIA hat den GPU-Chiplet beigesteuert. Viele Details zum GB10-SoC hat NVIDIA zur Hot-Chips-Konferenz im vergangenen Sommer veröffentlicht. Was die Analyse von Kurnal und Vergleiche durch SemiAnalysis nun offenbaren, ist der... [mehr] -

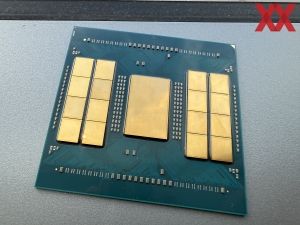

M5 Pro und M5 Max: Apple nun mit echtem Chiplet-Ansatz für seine SoCs

Apple hat heute das überarbeitete MacBook Pro und MacBook Air mit M5-Chip vorgestellt. Mit dem M5 Pro und M5 Max des MacBook Pro wechselt Apple auch erstmals auf eine echte Chiplet-Strategie, statt einfach nur zwei Chips zusammenzukleben. Die Chips werden aber weiterhin in N3P gefertigt, der N2-Prozess wird wohl erst für die nächste Generation zum Einsatz kommen. Ein Chiplet mit den 18 CPU-Kernen und ein Chiplet 20 und 40 Shader-Clustern... [mehr]

Apple hat heute das überarbeitete MacBook Pro und MacBook Air mit M5-Chip vorgestellt. Mit dem M5 Pro und M5 Max des MacBook Pro wechselt Apple auch erstmals auf eine echte Chiplet-Strategie, statt einfach nur zwei Chips zusammenzukleben. Die Chips werden aber weiterhin in N3P gefertigt, der N2-Prozess wird wohl erst für die nächste Generation zum Einsatz kommen. Ein Chiplet mit den 18 CPU-Kernen und ein Chiplet 20 und 40 Shader-Clustern... [mehr] -

2 nm auf 5 nm: Broadcom liefert erstes 3.5D-XDSiP-Design an Fujitsu

Broadcom gibt bekannt, dass man den ersten in 2 nm gefertigten Chip ausgeliefert hat. Die Lösung, bei der es sich vermutlich um den Monaka als Testchip für den späteren Monaka-X für den Supercomputer FugakuNEXT handelt, wurde an Fujitsu geliefert. Damit sind es nicht AMD, Apple oder NVIDIA, die einen solchen Chip offiziell in Dienst stellen, sondern eben Broadcom. Der Monaka ist ein Armv9-A-Design mit SVE2-Erweiterungen. Pro Sockel... [mehr]

Broadcom gibt bekannt, dass man den ersten in 2 nm gefertigten Chip ausgeliefert hat. Die Lösung, bei der es sich vermutlich um den Monaka als Testchip für den späteren Monaka-X für den Supercomputer FugakuNEXT handelt, wurde an Fujitsu geliefert. Damit sind es nicht AMD, Apple oder NVIDIA, die einen solchen Chip offiziell in Dienst stellen, sondern eben Broadcom. Der Monaka ist ein Armv9-A-Design mit SVE2-Erweiterungen. Pro Sockel... [mehr] -

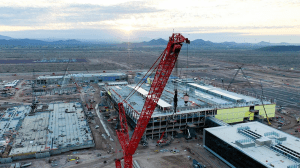

TSMC Arizona: Vier oder fünf Erweiterungen der Fab 21 geplant

Der Financial Times zufolge, wird TSMC noch in diesem Frühjahr eine größere Erweiterung seiner Fab 21 in Arizona ankündigen. Die USA und Taiwan haben in den vergangenen Wochen neue Handelsverträge verhandelt und dazu gehören neben Zollausnahmen auch weitere, große Investitionen von TSMC in den USA. Bereits am 7. Januar 2026 soll TSMC dazu eine Fläche von 4,5 km² direkt gegenüber den aktuellen Grundstücksflächen erstanden... [mehr]

Der Financial Times zufolge, wird TSMC noch in diesem Frühjahr eine größere Erweiterung seiner Fab 21 in Arizona ankündigen. Die USA und Taiwan haben in den vergangenen Wochen neue Handelsverträge verhandelt und dazu gehören neben Zollausnahmen auch weitere, große Investitionen von TSMC in den USA. Bereits am 7. Januar 2026 soll TSMC dazu eine Fläche von 4,5 km² direkt gegenüber den aktuellen Grundstücksflächen erstanden... [mehr] -

Zen-6-CCD mit 12 Kernen und 48 MB L3-Cache: Nur 7 % größere Chipfläche bei insgesamt 76 mm²

Leaker @9550pro liefert die vermeintliche Die-Größe der nächsten Ryzen-Generation alias Olympic Ridge oder Medusa Ridge. Diese wird genau wie die kommenden Epyc-Prozessoren auf bei TSMC in N2 gefertigte CCDs mit 12 Kernen setzen. Die Anzahl der Kerne je CCD steigt also von 8 auf 12 um 50 % und um eben diese 50 % beträgt auch das Plus beim L3-Cache, der dann 48 MB groß sein soll. Die Fläche von 76 mm² wäre beeindruckend, denn damit... [mehr]

Leaker @9550pro liefert die vermeintliche Die-Größe der nächsten Ryzen-Generation alias Olympic Ridge oder Medusa Ridge. Diese wird genau wie die kommenden Epyc-Prozessoren auf bei TSMC in N2 gefertigte CCDs mit 12 Kernen setzen. Die Anzahl der Kerne je CCD steigt also von 8 auf 12 um 50 % und um eben diese 50 % beträgt auch das Plus beim L3-Cache, der dann 48 MB groß sein soll. Die Fläche von 76 mm² wäre beeindruckend, denn damit... [mehr] -

2-nm-Prozess in den Startblöcken: TSMC schließt Rekordjahr ab

TSMC hat die Zahlen für das vierte Quartal 2025 veröffentlicht und damit das Gesamtjahr abgeschlossen. In Anbetracht des KI-Booms war von TSMC nichts anderes zu erwarten als Rekorde – im Umsatz, Gewinn, belichteten Wafern und ausgebuchten Fertigungslinien. Im vierten Quartal machte TSMC einen Umsatz von 33,7 Milliarden US-Dollar und eine Gewinnmarge von 48,3 %. Die Umsatzsteigerung von 25,5, 30,1, 33,1 und nun 33,7 Milliarden US-Dollar zeigt... [mehr]

TSMC hat die Zahlen für das vierte Quartal 2025 veröffentlicht und damit das Gesamtjahr abgeschlossen. In Anbetracht des KI-Booms war von TSMC nichts anderes zu erwarten als Rekorde – im Umsatz, Gewinn, belichteten Wafern und ausgebuchten Fertigungslinien. Im vierten Quartal machte TSMC einen Umsatz von 33,7 Milliarden US-Dollar und eine Gewinnmarge von 48,3 %. Die Umsatzsteigerung von 25,5, 30,1, 33,1 und nun 33,7 Milliarden US-Dollar zeigt... [mehr] -

Foundry-Gerüchteküche: AMD soll Samsung und Intel Foundry in Anspruch nehmen

Über das Wochenende gab es eine Reihe (teilweiser wilder) Gerüchte zur Fertigung zukünftiger Chips von AMD. Das koreanische Branchenmagazin Seoul Economic Daily, dass AMD derzeit Pläne habe, ein Chipdesign in 2 nm bei Samsung fertigen zu lassen. In einem ersten Schritt sollen dazu Multi-Project Wafer (MPW) gefertigt werden. Auf diesen können Kunden (auch mehrere gleichzeitig) ihre Designs oder einzelne Funktionen eines Chipdesigns... [mehr]

Über das Wochenende gab es eine Reihe (teilweiser wilder) Gerüchte zur Fertigung zukünftiger Chips von AMD. Das koreanische Branchenmagazin Seoul Economic Daily, dass AMD derzeit Pläne habe, ein Chipdesign in 2 nm bei Samsung fertigen zu lassen. In einem ersten Schritt sollen dazu Multi-Project Wafer (MPW) gefertigt werden. Auf diesen können Kunden (auch mehrere gleichzeitig) ihre Designs oder einzelne Funktionen eines Chipdesigns... [mehr] -

IVR, eDTC und UHPMIM: Intel und TSMC wollen 5+ kW an Chips liefern können

In einem LinkedIn-Beitrag verweist Igor Elkanovich vom taiwanesischen ASIC-Hersteller GUC (Global Unichip Corporation) auf die Möglichkeit, sogenannte IVRs (Integrated Voltage Regulator) in TSMCs CoWoS-L-Interposer zu integrieren und damit die Leistungsdichte deutlich zu steigern. Daneben verweisen die Kollegen von ComputerBase noch auf einen Vortrag von Intels Fellow Kaladhar Radhakrishnan auf dem ISSCC 2026 im Februar des kommenden Jahres... [mehr].

In einem LinkedIn-Beitrag verweist Igor Elkanovich vom taiwanesischen ASIC-Hersteller GUC (Global Unichip Corporation) auf die Möglichkeit, sogenannte IVRs (Integrated Voltage Regulator) in TSMCs CoWoS-L-Interposer zu integrieren und damit die Leistungsdichte deutlich zu steigern. Daneben verweisen die Kollegen von ComputerBase noch auf einen Vortrag von Intels Fellow Kaladhar Radhakrishnan auf dem ISSCC 2026 im Februar des kommenden Jahres... [mehr]. -

Silicon Photonics: TSMC will Partner frühzeitig mit einbeziehen

Neben weiteren Details zur Fertigung der Chips, dem Packaging und der zukünftigen Entwicklung beim Custom-HBM hat TSMC auf dem hauseigenen Open Innovation Platform Ecosystem Forum auch einige Details zur weiteren Entwicklung bei der optischen Datenübertragung verraten. An Technologien wie Silicon Photonics wird seit Jahrzehnten gearbeitet. Chiphersteller wie Intel und NVIDIA stellen die Vorteile einer optischen Datenübertragung auch für extrem... [mehr]

Neben weiteren Details zur Fertigung der Chips, dem Packaging und der zukünftigen Entwicklung beim Custom-HBM hat TSMC auf dem hauseigenen Open Innovation Platform Ecosystem Forum auch einige Details zur weiteren Entwicklung bei der optischen Datenübertragung verraten. An Technologien wie Silicon Photonics wird seit Jahrzehnten gearbeitet. Chiphersteller wie Intel und NVIDIA stellen die Vorteile einer optischen Datenübertragung auch für extrem... [mehr] -

TSMC 3DFabric und C-HBM4E: Advanced Packaging und (Custom) Base-Dies für HBM4(E)

Neben der Fertigung von Chips in den aktuellsten Herstellungsprozessen gehört das Advanced Packaging zu den Aushängeschildern von TSMC und ist für die allermeisten Chips auch unabdingbar. Entsprechend baut TSMC nicht nur die Kapazitäten seiner Fabs weitreichend aus, sondern auch die für das Advanced Packaging. Auf die Weiterentwicklungen in diesem Bereich kommen wir später. Im Rahmen des Advanced Packaging und der Integration von HBM4 wird den... [mehr]

Neben der Fertigung von Chips in den aktuellsten Herstellungsprozessen gehört das Advanced Packaging zu den Aushängeschildern von TSMC und ist für die allermeisten Chips auch unabdingbar. Entsprechend baut TSMC nicht nur die Kapazitäten seiner Fabs weitreichend aus, sondern auch die für das Advanced Packaging. Auf die Weiterentwicklungen in diesem Bereich kommen wir später. Im Rahmen des Advanced Packaging und der Integration von HBM4 wird den... [mehr] -

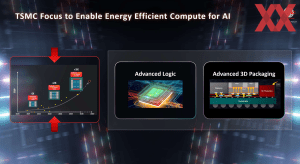

Advanced Silicon, Stacking und Packaging: TSMC baut weiter auf drei Säulen

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt bzw. detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag... [mehr]

Auf dem Open Innovation Platform Ecosystem Forum hat TSMC weite Teile seiner Pläne in den verschiedenen Bereichen wiederholt bzw. detaillierter ausgeführt. Natürlich kommt auch TSMC nicht daran vorbei, den aktuellen KI-Hype zu adressieren. Dabei sieht TSMC sowohl das Training, als auch das Inferencing von KI-Modellen gleichermaßen als wichtig an – entsprechend der Verteilung an Chips, welche von den Kunden bei TSMC in Auftrag... [mehr] -

Weitergabe von Geheimnissen an Intel: TSMC verklagt Ex-Mitarbeiter

Mitte diesen Jahres wehrte sich TSMC gegen die vermeintliche Weitergabe von internen Informationen an Rapidus. Mitarbeitern wurden vorgeworfen, interne Dokumente über den Zulieferer Tokyo Electron (TEL) an den Konkurrenten Rapidus weitergegeben zu haben. Sowohl TSMC wie auch TEL zogen entsprechende Konsequenzen und stellten den beschuldigten Mitarbeiter frei. Bereits in der vergangenen Woche wurde bekannt, dass der ehemalige Senior Vice... [mehr]

Mitte diesen Jahres wehrte sich TSMC gegen die vermeintliche Weitergabe von internen Informationen an Rapidus. Mitarbeitern wurden vorgeworfen, interne Dokumente über den Zulieferer Tokyo Electron (TEL) an den Konkurrenten Rapidus weitergegeben zu haben. Sowohl TSMC wie auch TEL zogen entsprechende Konsequenzen und stellten den beschuldigten Mitarbeiter frei. Bereits in der vergangenen Woche wurde bekannt, dass der ehemalige Senior Vice... [mehr] -

Aufregung um US-Startup: Röntgenlithografie soll ASML und TSMC Konkurrenz machen

Die Halbleiterindustrie befindet sich an einem kritischen Wendepunkt. Während konventionelle Extremultraviolett-Lithographie (EUV) mit einer Wellenlänge von 13,5 nm derzeit als etablierte Technologie in der Fertigung fortgeschrittener Chips dominiert, rücken alternative Ansätze in den Fokus des technologischen Interesses. Eine dieser vielversprechenden Technologien ist die Röntgenlithographie (XRL), die Wellenlängen von weniger als vier... [mehr]

Die Halbleiterindustrie befindet sich an einem kritischen Wendepunkt. Während konventionelle Extremultraviolett-Lithographie (EUV) mit einer Wellenlänge von 13,5 nm derzeit als etablierte Technologie in der Fertigung fortgeschrittener Chips dominiert, rücken alternative Ansätze in den Fokus des technologischen Interesses. Eine dieser vielversprechenden Technologien ist die Röntgenlithographie (XRL), die Wellenlängen von weniger als vier... [mehr] -

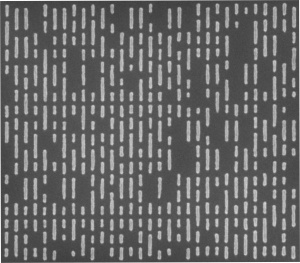

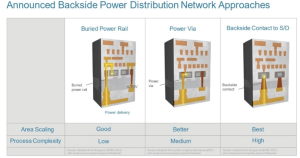

Für Feynman: NVIDIA soll erster Kunde für A16-Fertigung mit Backside-Power von TSMC sein

Das taiwanesische Branchenmagazin Commercial Times berichtet, dass NVIDIA mit dem KI-Chip der übernächsten Generation namens Feynman der erst Kunde von TSMC sein soll, der auf die Fertigung im A16-Prozess setzt. Dies stellt eine besondere Herausforderung dar, da die Chiphersteller für die allerneusten Prozesse üblicherweise auf deutlich kleinere Chips setzen. Ein Blick auf die aktuellen KI-Chips bei NVIDIA zeigt: Man nutzt auf die... [mehr]

Das taiwanesische Branchenmagazin Commercial Times berichtet, dass NVIDIA mit dem KI-Chip der übernächsten Generation namens Feynman der erst Kunde von TSMC sein soll, der auf die Fertigung im A16-Prozess setzt. Dies stellt eine besondere Herausforderung dar, da die Chiphersteller für die allerneusten Prozesse üblicherweise auf deutlich kleinere Chips setzen. Ein Blick auf die aktuellen KI-Chips bei NVIDIA zeigt: Man nutzt auf die... [mehr] -

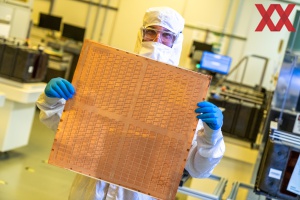

NVIDIA x TSMC: Erster Blackwell-Wafer in den USA hergestellt

Im Frühjahr, kurz nach der Hausmesse GTC, kündigte NVIDIA an, dass TSMC in der Fab 21 in Arizona bald auch Blackwell-GPUs fertigen werden. Die ersten Chips bzw. Wafer sollten zu diesem Zeitpunkt bereits in der Produktion sein. Zudem sollten Systemhersteller wie Foxconn in Houston und Wistron in Dallas entsprechende Werke errichten, die in den kommenden 12 bis 15 Monaten mit der Massenproduktion der kompletten Server beginnen... [mehr]

Im Frühjahr, kurz nach der Hausmesse GTC, kündigte NVIDIA an, dass TSMC in der Fab 21 in Arizona bald auch Blackwell-GPUs fertigen werden. Die ersten Chips bzw. Wafer sollten zu diesem Zeitpunkt bereits in der Produktion sein. Zudem sollten Systemhersteller wie Foxconn in Houston und Wistron in Dallas entsprechende Werke errichten, die in den kommenden 12 bis 15 Monaten mit der Massenproduktion der kompletten Server beginnen... [mehr] -

Quartalszahlen: TSMC macht Umsatzrekord und N2 geht in die Massenproduktion

TSMC hat seine Zahlen für das dritte Quartal 2025 veröffentlicht und vermeldet darin Umsatz- und Gewinnrekorde. Mit 33,1 Milliarden US-Dollar machte der Umsatz einen Sprung von rund 30 % mit einem leichten Anstieg von 6 % gegenüber dem vorherigen Quartal. Der Gewinn lag bei 15,1 Milliarden US-Dollar, was im Vorjahresvergleich ein Plus von 39 % darstellt. Limitiert wird TSMC im Grunde nur durch die Kapazitäten, die durch die eigenen Fabs... [mehr]

TSMC hat seine Zahlen für das dritte Quartal 2025 veröffentlicht und vermeldet darin Umsatz- und Gewinnrekorde. Mit 33,1 Milliarden US-Dollar machte der Umsatz einen Sprung von rund 30 % mit einem leichten Anstieg von 6 % gegenüber dem vorherigen Quartal. Der Gewinn lag bei 15,1 Milliarden US-Dollar, was im Vorjahresvergleich ein Plus von 39 % darstellt. Limitiert wird TSMC im Grunde nur durch die Kapazitäten, die durch die eigenen Fabs... [mehr] -

Snapdragon X2 Elite Extreme: Qualcomm nutzt TSMC FinFlex für N3X und N3P

Bereits bekannt ist, dass Qualcomm zur Fertigung des neuen Snapdragon X2 Elite Extreme den 3-nm-Prozess – genauer gesagt N3P von TSMC – verwendet. In einem Gespräch mit ComputerBase äußerte sich Mandar Deshpande, Senior Director of Product Management bei Qualcomm, zu weiteren Details. Der Snapdragon X2 Elite Extreme erreicht mit seinen Prime-Kernen erstmals für einen ARM-SoC einen maximalen Boost-Takt von 5 GHz. Um diesen Takt... [mehr]

Bereits bekannt ist, dass Qualcomm zur Fertigung des neuen Snapdragon X2 Elite Extreme den 3-nm-Prozess – genauer gesagt N3P von TSMC – verwendet. In einem Gespräch mit ComputerBase äußerte sich Mandar Deshpande, Senior Director of Product Management bei Qualcomm, zu weiteren Details. Der Snapdragon X2 Elite Extreme erreicht mit seinen Prime-Kernen erstmals für einen ARM-SoC einen maximalen Boost-Takt von 5 GHz. Um diesen Takt... [mehr] -

HBM4 von Micron: 11 GBit/s werden erreicht und TSMC fertigt den Base-Die

Nachdem SK Hynix bereits in der vergangenen Woche die Massenproduktion von HBM4 mit 10 GBit/s und mehr angekündigt hat und damit die Anforderungen von NVIDIA erfüllt, zog nun auch Micron nach. Im Rahmen der Bekanntgabe der Zahlen für das dritte Quartal 2025 widersprach der Speicherspezialist den Gerüchten der vergangenen Tage, der HBM4 von Micron könnte die geforderte Datenraten nicht erreichen. Laut Hersteller hat man allerdings bereits... [mehr]

Nachdem SK Hynix bereits in der vergangenen Woche die Massenproduktion von HBM4 mit 10 GBit/s und mehr angekündigt hat und damit die Anforderungen von NVIDIA erfüllt, zog nun auch Micron nach. Im Rahmen der Bekanntgabe der Zahlen für das dritte Quartal 2025 widersprach der Speicherspezialist den Gerüchten der vergangenen Tage, der HBM4 von Micron könnte die geforderte Datenraten nicht erreichen. Laut Hersteller hat man allerdings bereits... [mehr] -

TSMC N2: MediaTek gibt Tape-Out von SoC bekannt

Per Pressemitteilung gibt MediaTek bekannt, dass man den Tape-Out eines SoC in 2 nm bei TSMC vollzogen hat. Bisher liegt die Pressemitteilung nur in chinesischer Sprache vor und dennoch ist diese für MediaTek und TSMC zugleich bedeutend. Im Frühjahr haben AMD und TSMC den Tape-Out der CCDs mit Zen-6-Kernen gefeiert. Beim Chip von MediaTek handelt es sich um einen neuen SoC, vermeintlich den Dimensity 9600. Der Vorgänger Dimensity 9500... [mehr]

Per Pressemitteilung gibt MediaTek bekannt, dass man den Tape-Out eines SoC in 2 nm bei TSMC vollzogen hat. Bisher liegt die Pressemitteilung nur in chinesischer Sprache vor und dennoch ist diese für MediaTek und TSMC zugleich bedeutend. Im Frühjahr haben AMD und TSMC den Tape-Out der CCDs mit Zen-6-Kernen gefeiert. Beim Chip von MediaTek handelt es sich um einen neuen SoC, vermeintlich den Dimensity 9600. Der Vorgänger Dimensity 9500... [mehr] -

N2P und N3P: AMD geht auch für den kommenden IOD auf fortschrittliche Fertigung

Bereits bekannt ist, dass AMD den CCD für die kommenden Epyc-Prozessoren mit Zen-6-Kernen alias Venice bei TSMC in einem 2-nm-Prozess fertigen wird. Um welchen Prozess es sich genau handelt, war und ist noch nicht bekannt. Leaker Kepler_L2 vermerkt im Forum von AnandTech: Der N2P-Prozess und damit eine auf Leistung optimierte Variante soll es sein. In N2P gefertigt werden sollen die CCDs mit 12 Zen-6-Kernen je Chip. Auch die Dense-CCDs mit den... [mehr]

Bereits bekannt ist, dass AMD den CCD für die kommenden Epyc-Prozessoren mit Zen-6-Kernen alias Venice bei TSMC in einem 2-nm-Prozess fertigen wird. Um welchen Prozess es sich genau handelt, war und ist noch nicht bekannt. Leaker Kepler_L2 vermerkt im Forum von AnandTech: Der N2P-Prozess und damit eine auf Leistung optimierte Variante soll es sein. In N2P gefertigt werden sollen die CCDs mit 12 Zen-6-Kernen je Chip. Auch die Dense-CCDs mit den... [mehr] -

Vergleich zu Intel, TSMC und Samsung: Rapidus soll bei 2 nm auf Augenhöhe sein

Der durch den japanischen Staat und in gemeinsamen Anstrengungen mit IBM ins Leben gerufene Auftragsfertiger Rapidus will ab 2027 die ersten in 2 nm gefertigten Chips liefern. Auf der Hot-Chips-Konferenz präsentierte sich das Unternehmen vor allem im Hinblick auf die Turnaround Time (TAT), also der Zeit, die der Wafer benötigt, um in der Fab fertiggestellt zu werden. Mit 50 Tagen will sich Rapidus hier von der Konkurrenz absetzen... [mehr]

Der durch den japanischen Staat und in gemeinsamen Anstrengungen mit IBM ins Leben gerufene Auftragsfertiger Rapidus will ab 2027 die ersten in 2 nm gefertigten Chips liefern. Auf der Hot-Chips-Konferenz präsentierte sich das Unternehmen vor allem im Hinblick auf die Turnaround Time (TAT), also der Zeit, die der Wafer benötigt, um in der Fab fertiggestellt zu werden. Mit 50 Tagen will sich Rapidus hier von der Konkurrenz absetzen... [mehr] -

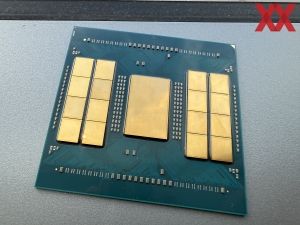

Huawei KunPeng 930: Details zur Fertigung bei TSMC und SMIC

Bereits 2019 stellte Huawei mit mem KunPeng 920 einen Serverprozessor mit 64 ARM-Kernen vor, der damals in 7 nm gefertigt wurde. Inzwischen gibt es mit dem KunPeng 930 den Nachfolger, zu dem es nun eine detaillierte Analyse gibt. Zunächst einmal handelt es sich beim KunPeng um ein Chiplet-Design bestehend aus zwei Compute- und ebenfalls zwei I/O-Dies. Der I/O-Die kommt auf eine Fläche von 172,3 mm² und das zentrale Compute-Die bringt es auf... [mehr]

Bereits 2019 stellte Huawei mit mem KunPeng 920 einen Serverprozessor mit 64 ARM-Kernen vor, der damals in 7 nm gefertigt wurde. Inzwischen gibt es mit dem KunPeng 930 den Nachfolger, zu dem es nun eine detaillierte Analyse gibt. Zunächst einmal handelt es sich beim KunPeng um ein Chiplet-Design bestehend aus zwei Compute- und ebenfalls zwei I/O-Dies. Der I/O-Die kommt auf eine Fläche von 172,3 mm² und das zentrale Compute-Die bringt es auf... [mehr] -

NVIDIA bestätigt Tape Out: Sechs neue Chips laufen bald bei TSMC vom Band

NVIDIAs CEO Jensen Huang hat einmal mehr Taiwan besucht und sich dabei auch mit seinem wichtigsten Auftragsfertiger TSMC getroffen. Erst vor wenigen Tagen wurden Gerüchten zu Verzögerungen bei der Rubin-GPU seitens NVIDIA widersprochen. Die KI-Beschleuniger auf Basis von Rubin werden im kommenden Jahr erwartet und sollen erstmals auf HBM4 setzen. Nach seinem kurzen Besuch äußerte sich Jensen Huang gegenüber der Presse wie folgt: My main... [mehr]

NVIDIAs CEO Jensen Huang hat einmal mehr Taiwan besucht und sich dabei auch mit seinem wichtigsten Auftragsfertiger TSMC getroffen. Erst vor wenigen Tagen wurden Gerüchten zu Verzögerungen bei der Rubin-GPU seitens NVIDIA widersprochen. Die KI-Beschleuniger auf Basis von Rubin werden im kommenden Jahr erwartet und sollen erstmals auf HBM4 setzen. Nach seinem kurzen Besuch äußerte sich Jensen Huang gegenüber der Presse wie folgt: My main... [mehr] -

Wirbel bei TSMC: Geschäftsgeheimnisse abgeflossen und Fake News zu Milliardeninvestitionen

In den vergangenen Tagen gab es bei TSMC aus gleich zweierlei Richtungen großen Wirbel und auch einen handfesten Skandal rund um gestohlene Geschäftsgeheimnisse. Aufgrund der Brisanz und Wichtigkeit von TSMC als Unternehmen in Taiwan sind die örtlichen Online- und Fernsehmedien voll mit Meldungen zur Weitergabe von internen Informationen. Im Homeoffice tätig, sollen mehrere Verdächtige auf interne Dokumente zur Fertigung in 2 nm... [mehr]

In den vergangenen Tagen gab es bei TSMC aus gleich zweierlei Richtungen großen Wirbel und auch einen handfesten Skandal rund um gestohlene Geschäftsgeheimnisse. Aufgrund der Brisanz und Wichtigkeit von TSMC als Unternehmen in Taiwan sind die örtlichen Online- und Fernsehmedien voll mit Meldungen zur Weitergabe von internen Informationen. Im Homeoffice tätig, sollen mehrere Verdächtige auf interne Dokumente zur Fertigung in 2 nm... [mehr] -

Quartalszahlen: TSMC liefert dank N3 und N5 Rekordergebnis ab

TSMC hat die Zahlen für das zweite Quartal 2025 veröffentlicht und vermeldet darin ein weiteres Rekordergebnis – vor allem dank der noch immer starken Nachfrage nach High-End-Chips und den gestiegenen Preisen. TSMC machte in den vergangenen drei Monaten einen Umsatz von 30 Milliarden US-Dollar und konnte dabei einen Gewinn von 12,8 Milliarden US-Dollar erzielen. Der Gewinn steigt im Vorjahresvergleich um satte 60 %. Den größten Anteil und... [mehr]

TSMC hat die Zahlen für das zweite Quartal 2025 veröffentlicht und vermeldet darin ein weiteres Rekordergebnis – vor allem dank der noch immer starken Nachfrage nach High-End-Chips und den gestiegenen Preisen. TSMC machte in den vergangenen drei Monaten einen Umsatz von 30 Milliarden US-Dollar und konnte dabei einen Gewinn von 12,8 Milliarden US-Dollar erzielen. Der Gewinn steigt im Vorjahresvergleich um satte 60 %. Den größten Anteil und... [mehr] -

Chipfertigung: Intel 18A bei 70 % Ausbeute, Zen 6 in N2-Derivaten

Aus verschiedenen Quellen gibt es Wasserstandsmeldungen rund um den Zustand der Fertigung für zukünftige Chips von AMD und Intel. Während diese mit vermeintlichen Daten zu Panther Lake aber ein Produkt beschreiben, welches schon in wenigen Monaten auf den Markt kommen wird, schauen die Meldungen zur Fertigung der Zen-6-Chiplets noch etwas weiter in die Zukunft. Die für gewöhnlich gut informierte Quelle Kepler_L2, bei X und im Anandtech-Forum... [mehr]

Aus verschiedenen Quellen gibt es Wasserstandsmeldungen rund um den Zustand der Fertigung für zukünftige Chips von AMD und Intel. Während diese mit vermeintlichen Daten zu Panther Lake aber ein Produkt beschreiben, welches schon in wenigen Monaten auf den Markt kommen wird, schauen die Meldungen zur Fertigung der Zen-6-Chiplets noch etwas weiter in die Zukunft. Die für gewöhnlich gut informierte Quelle Kepler_L2, bei X und im Anandtech-Forum... [mehr] -

In TSMC N2: Nova Lake soll Tape Out geschafft haben

Wie SemiAccurate berichtet, soll ein zukünftiges Produkt, bzw. ein dazugehöriger Chip bei Intel vor wenigen Wochen den wichtigen Meilenstein des Tape Out geschafft haben. Der Tape Out bezeichnet den finalen Schritt im Chipdesign, bei dem das vollständige Layout eines Chips zur Fertigung freigegeben wird. Es ist der Moment, in dem das Design an die Halbleiterfertigung übergeben wird, um Fotomasken für die Chipproduktion zu erstellen. Der... [mehr]

Wie SemiAccurate berichtet, soll ein zukünftiges Produkt, bzw. ein dazugehöriger Chip bei Intel vor wenigen Wochen den wichtigen Meilenstein des Tape Out geschafft haben. Der Tape Out bezeichnet den finalen Schritt im Chipdesign, bei dem das vollständige Layout eines Chips zur Fertigung freigegeben wird. Es ist der Moment, in dem das Design an die Halbleiterfertigung übergeben wird, um Fotomasken für die Chipproduktion zu erstellen. Der... [mehr] -

TSMC Arizona: Advanced Packaging ab 2028 auch in den USA

Bisher hat TSMC die Maßgabe herausgegeben, dass moderne Chips zwar auch außerhalb Taiwan in den eigenen Fabs gefertigt werden dürfen, die modernsten Prozesse aber gibt es nur aus dem Heimatland. Taiwan nutzt TSMC so als Silicon Shield und will sicherstellen, dass die Werke auf der Insel so extrem wichtig sind, dass eine eventuelle Besetzung Taiwans durch China den Weltmarkt von den modernsten Chips abschneiden würde. Aktuell fertigt TSMC in... [mehr]

Bisher hat TSMC die Maßgabe herausgegeben, dass moderne Chips zwar auch außerhalb Taiwan in den eigenen Fabs gefertigt werden dürfen, die modernsten Prozesse aber gibt es nur aus dem Heimatland. Taiwan nutzt TSMC so als Silicon Shield und will sicherstellen, dass die Werke auf der Insel so extrem wichtig sind, dass eine eventuelle Besetzung Taiwans durch China den Weltmarkt von den modernsten Chips abschneiden würde. Aktuell fertigt TSMC in... [mehr] -

GaN-Wafer für Leistungselektronik: Infineon fährt hoch, TSMC fährt runter

Im vergangenen Jahr verkündete Infineon den Aufbau einer ersten Pilotlinie für die Herstellung von Leistungshalbleitern auf Basis von Galliumnitrid (GaN). Mit einer Fertigung mit Wafern in 300 mm will Infineon damit einerseits die technischen Vorteile dieser Leistungshalbleiter und andererseits auch die wirtschaftlichen Vorteile der großen Wafer mitnehmen. Die Leistungshalbleiter kommen in vielerlei Elektronik zum Einsatz – Von E-Autos,... [mehr]

Im vergangenen Jahr verkündete Infineon den Aufbau einer ersten Pilotlinie für die Herstellung von Leistungshalbleitern auf Basis von Galliumnitrid (GaN). Mit einer Fertigung mit Wafern in 300 mm will Infineon damit einerseits die technischen Vorteile dieser Leistungshalbleiter und andererseits auch die wirtschaftlichen Vorteile der großen Wafer mitnehmen. Die Leistungshalbleiter kommen in vielerlei Elektronik zum Einsatz – Von E-Autos,... [mehr] -

Chipfertigung: Samsung will TSMC bei 2 nm überholen

In den vergangenen Jahren ist das Foundry-Geschäft bei Samsung nicht gerade durch eine leistungsstarke und planmäßige Ausführung aufgefallen. Immer wieder war von Problemen bei der Ausbeute die Rede, neue Technologien wurde auf spätere Fertigungsschritte verschoben und Umbenennungen sollten vorgenommen werden. Noch immer aber ist Samsung hinter Platzhirsch TSMC der zweitgrößte Auftragsfertiger und allesamt haben die Chiphersteller mit der... [mehr]

In den vergangenen Jahren ist das Foundry-Geschäft bei Samsung nicht gerade durch eine leistungsstarke und planmäßige Ausführung aufgefallen. Immer wieder war von Problemen bei der Ausbeute die Rede, neue Technologien wurde auf spätere Fertigungsschritte verschoben und Umbenennungen sollten vorgenommen werden. Noch immer aber ist Samsung hinter Platzhirsch TSMC der zweitgrößte Auftragsfertiger und allesamt haben die Chiphersteller mit der... [mehr] -

CoPoS-Packaging: TSMC ist auf der Suche nach Interposer-Alternativen

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei... [mehr]

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei... [mehr] -

Absage an Intel Foundry: NVIDIA nutzt weiter nur TSMC für das Packaging

Seit einigen Monaten wird Intel nicht müde durch seine Foundry-Sparte für ein (Advanced)-Packaging externer Kunden bei Intel Foundry zu werben. Man habe die Technologien, man habe die Kapazitäten und geopolitisch sei es sicherlich auch für viele Kunden interessant. Auf der Computex 2025 wurde NVIDIA CEO Jensen Huang in einer 90-minütigen Fragerunde darauf angesprochen, wie wichtig das Advanced Packaging für die Weiterentwicklung der KI-Hardware... [mehr]

Seit einigen Monaten wird Intel nicht müde durch seine Foundry-Sparte für ein (Advanced)-Packaging externer Kunden bei Intel Foundry zu werben. Man habe die Technologien, man habe die Kapazitäten und geopolitisch sei es sicherlich auch für viele Kunden interessant. Auf der Computex 2025 wurde NVIDIA CEO Jensen Huang in einer 90-minütigen Fragerunde darauf angesprochen, wie wichtig das Advanced Packaging für die Weiterentwicklung der KI-Hardware... [mehr] -

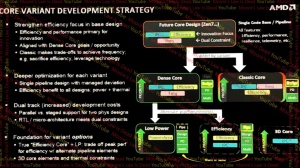

Gerüchte zu Zen-7-Architektur: AMD soll mit A14-Fertigung und neuen Kern-Varianten planen

Gerade erst hat AMD seine Zen-5-Familie mit den EPYC-4005-Prozessoren abgeschlossen, da kommt der für seine Leaks bekannte, aber nicht immer ganz treffsichere YouTuber Moore's Law Is Dead um die Ecke und lässt die ersten Informationshappen zur Zen-7-Architektur fallen. Dabei ist noch nicht viel über die Zen-6-Architektur bekannt, die für 2026 die Basis für AMDs Ryzen- und EPYC-Prozessoren bilden soll. Demnach will AMD mit dem Zen-7-Design eine... [mehr]

Gerade erst hat AMD seine Zen-5-Familie mit den EPYC-4005-Prozessoren abgeschlossen, da kommt der für seine Leaks bekannte, aber nicht immer ganz treffsichere YouTuber Moore's Law Is Dead um die Ecke und lässt die ersten Informationshappen zur Zen-7-Architektur fallen. Dabei ist noch nicht viel über die Zen-6-Architektur bekannt, die für 2026 die Basis für AMDs Ryzen- und EPYC-Prozessoren bilden soll. Demnach will AMD mit dem Zen-7-Design eine... [mehr] -

Anstatt TSMC: AMD soll I/O-Dies bei Samsung fertigen wollen

Laut eines Berichts von The Bell in Korea soll die Foundry-Abteilung von Samsung aktuell mit AMD in einer erweiterten Zusammenarbeit hinsichtlich der Fertigung neuer Chips sein. Konkret soll Samsung Test-Chips für AMD gefertigt haben, welche als I/O-Dies auf den zukünftigen EPYC-Prozessoren zum Einsatz kommen. Als Fertigungsgröße soll ein 4-nm-Prozess angedacht sein. Aktuell lässt AMD sowohl die I/O-Dies (IOD) wie auch die Chips mit den... [mehr]

Laut eines Berichts von The Bell in Korea soll die Foundry-Abteilung von Samsung aktuell mit AMD in einer erweiterten Zusammenarbeit hinsichtlich der Fertigung neuer Chips sein. Konkret soll Samsung Test-Chips für AMD gefertigt haben, welche als I/O-Dies auf den zukünftigen EPYC-Prozessoren zum Einsatz kommen. Als Fertigungsgröße soll ein 4-nm-Prozess angedacht sein. Aktuell lässt AMD sowohl die I/O-Dies (IOD) wie auch die Chips mit den... [mehr] -

TSMC-Fertigung: Unternehmen darf modernste Technik nicht im Ausland verwenden

Die taiwanische Regierung hat ihr Gesetz zur industriellen Innovation überarbeitet und damit formell festgelegt, dass Unternehmen wie TSMC ihre modernste Chipfertigung ausschließlich in Taiwan betreiben dürfen. Die Neuregelung verpflichtet taiwanische Firmen künftig dazu, größere Auslandsinvestitionen vom Wirtschaftsministerium genehmigen zu lassen. Im Zentrum der Reform steht insbesondere Artikel 22, der es den Behörden ermöglicht,... [mehr]

Die taiwanische Regierung hat ihr Gesetz zur industriellen Innovation überarbeitet und damit formell festgelegt, dass Unternehmen wie TSMC ihre modernste Chipfertigung ausschließlich in Taiwan betreiben dürfen. Die Neuregelung verpflichtet taiwanische Firmen künftig dazu, größere Auslandsinvestitionen vom Wirtschaftsministerium genehmigen zu lassen. Im Zentrum der Reform steht insbesondere Artikel 22, der es den Behörden ermöglicht,... [mehr] -

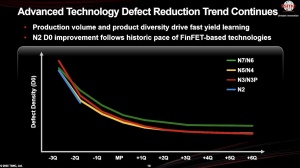

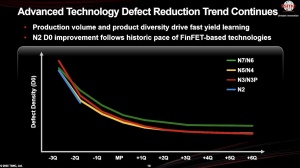

Technology Symposium 2025: TSMC ist bezüglich N2-Fertigung extrem zuversichtlich

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA aber bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden. In der Fertigung ein Fokus lag dabei auf N2 als nächster großer Schritt in der Fertigung. Zwar hat TSMC auch schon die Nachfolger A16 und A14... [mehr]

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA aber bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden. In der Fertigung ein Fokus lag dabei auf N2 als nächster großer Schritt in der Fertigung. Zwar hat TSMC auch schon die Nachfolger A16 und A14... [mehr] -

Technology Symposium 2025: TSMC zu CoWoS, SoIC, SoW als Packaging-Optionen

Neben der fortschreitenden Entwicklung in der Fertigung der einzelnen Chips ist TSMC in den vergangenen Jahren mindestens ebenso ambitioniert und erfolgreich, wenn es um das Packaging geht. Auf dem Technology Symposium 2025 präsentierte man einen Fahrplan für die kommenden Jahre. Beim Packaging steht TSMC auf zwei Grundpfeilern, die sich wiederum in weiteren Technologieblöcke aufteilen. Zum Advanced Packaging gehören CoWoS (Chip on Wafer on... [mehr]

Neben der fortschreitenden Entwicklung in der Fertigung der einzelnen Chips ist TSMC in den vergangenen Jahren mindestens ebenso ambitioniert und erfolgreich, wenn es um das Packaging geht. Auf dem Technology Symposium 2025 präsentierte man einen Fahrplan für die kommenden Jahre. Beim Packaging steht TSMC auf zwei Grundpfeilern, die sich wiederum in weiteren Technologieblöcke aufteilen. Zum Advanced Packaging gehören CoWoS (Chip on Wafer on... [mehr] -

AMD und NVIDIA: EPYC-CPUs und Blackwell-GPUs aus TSMCs Arizona-Fab

Bereits in einer Fragerunde nach der Keynote auf der GTC 2025 sagte NVIDIAs CEO Jensen Huang, dass man damit begonnen habe, gemeinsam mit TSMC in deren Fab im US-Bundesstaat Arizona erste Blackwell-GPUs zu fertigen. In einem Blog-Beitrag bestätigt dies NVIDIA nun offiziell und nennt nicht nur TSMC als Fertiger für die Blackwell-GPUs, sondern spricht auch davon, dass die Systemhersteller Foxconn in Houston und Wistron in Dallas... [mehr]

Bereits in einer Fragerunde nach der Keynote auf der GTC 2025 sagte NVIDIAs CEO Jensen Huang, dass man damit begonnen habe, gemeinsam mit TSMC in deren Fab im US-Bundesstaat Arizona erste Blackwell-GPUs zu fertigen. In einem Blog-Beitrag bestätigt dies NVIDIA nun offiziell und nennt nicht nur TSMC als Fertiger für die Blackwell-GPUs, sondern spricht auch davon, dass die Systemhersteller Foxconn in Houston und Wistron in Dallas... [mehr] -

AMD EPYC Venice: AMD und TSMC zeigen in N2 gefertigten CCD mit Zen-6-Kernen

Aktuell bereist AMD-CEO Lisa Su Taiwan, um unter anderem TSMC, einen der zentralen Fertigungspartner, zu treffen. Im Rahmen eines gemeinsamen Events wurde bestätigt, dass die CCDs der kommenden EPYC-Generation "Venice" (Zen 6) im 2-nm-Prozess (N2) mit GAA-Nanosheet-Transistoren gefertigt werden. Laut AMD und TSMC zählen die Zen-6-basierten CCDs zu den ersten HPC-Dies, die im N2-Node in die Serienproduktion überführt werden. Die N2-Fertigung... [mehr]

Aktuell bereist AMD-CEO Lisa Su Taiwan, um unter anderem TSMC, einen der zentralen Fertigungspartner, zu treffen. Im Rahmen eines gemeinsamen Events wurde bestätigt, dass die CCDs der kommenden EPYC-Generation "Venice" (Zen 6) im 2-nm-Prozess (N2) mit GAA-Nanosheet-Transistoren gefertigt werden. Laut AMD und TSMC zählen die Zen-6-basierten CCDs zu den ersten HPC-Dies, die im N2-Node in die Serienproduktion überführt werden. Die N2-Fertigung... [mehr] -

Intel ist weiterhin eine Option: Blackwell Ultra wird bereits in Arizona gefertigt

Für NVIDIA spielt China eine große Rolle: Einerseits, weil ein Teil der Fertigung der Systeme dort stattfindet und andererseits natürlich auch als Markt für die eigenen Produkte. Die zahlreiche Implikationen durch Handelsbeschränkungen, Strafzölle und Umgehung dieser soll an dieser Stelle aber keine Rolle spielen. Stattdessen wurde NVIDIA CEO Jensen Huang in einer Frage-und-Antwort-Runde auf der GTC gefragt, wie NVIDIA seine Investitionen... [mehr]

Für NVIDIA spielt China eine große Rolle: Einerseits, weil ein Teil der Fertigung der Systeme dort stattfindet und andererseits natürlich auch als Markt für die eigenen Produkte. Die zahlreiche Implikationen durch Handelsbeschränkungen, Strafzölle und Umgehung dieser soll an dieser Stelle aber keine Rolle spielen. Stattdessen wurde NVIDIA CEO Jensen Huang in einer Frage-und-Antwort-Runde auf der GTC gefragt, wie NVIDIA seine Investitionen... [mehr] -

Ende der Subventionen: Trump will US Chips Act begraben

Donald Trump ist bekanntermaßen kein Freund des US Chips Act. Nun hat der US-Präsident das Förderprogramm für die Halbleiterbranche aktiv ins Visier genommen und fordert dessen Abschaffung. Das Subventionspaket, das unter der Biden-Regierung verabschiedet wurde, soll die inländische Chipfertigung stärken und damit die Abhängigkeit von Importen reduzieren. Trump kritisierte das Programm in einer Rede vor dem US-Kongress scharf und... [mehr]

Donald Trump ist bekanntermaßen kein Freund des US Chips Act. Nun hat der US-Präsident das Förderprogramm für die Halbleiterbranche aktiv ins Visier genommen und fordert dessen Abschaffung. Das Subventionspaket, das unter der Biden-Regierung verabschiedet wurde, soll die inländische Chipfertigung stärken und damit die Abhängigkeit von Importen reduzieren. Trump kritisierte das Programm in einer Rede vor dem US-Kongress scharf und... [mehr] -

Weitere 100 Milliarden US-Dollar: TSMC verdoppelt die Anzahl seiner US-Chipfabriken

Drei große Chipfabriken hat TSMC in den USA bereits in Planung, von denen die erste im ersten Halbjahr 2025 in die Massenproduktion gehen soll. Phase 2 befindet sich aktuell im Bau und soll ab 2028 die ersten Chips ausspucken und die Planung für eine Phase 3 gab es bereits. Nun verkünden die US-Regierung und TSMC, dass der Bau dreier weiterer Chipfabriken geplant sei. Damit steigt das geplante Investitionsvolumen von 65 auf nun 165 Milliarden... [mehr]

Drei große Chipfabriken hat TSMC in den USA bereits in Planung, von denen die erste im ersten Halbjahr 2025 in die Massenproduktion gehen soll. Phase 2 befindet sich aktuell im Bau und soll ab 2028 die ersten Chips ausspucken und die Planung für eine Phase 3 gab es bereits. Nun verkünden die US-Regierung und TSMC, dass der Bau dreier weiterer Chipfabriken geplant sei. Damit steigt das geplante Investitionsvolumen von 65 auf nun 165 Milliarden... [mehr] -

Zusammenarbeit mit TSMC: Marvell demonstriert ersten in 2 nm gefertigten Chip

Marvell verkündet heute, dass man in Zusammenarbeit mit TSMC den ersten funktionsfähigen, in 2 nm gefertigten Chip hergestellt hat. Im Frühjahr 2024 verkündeten beide Unternehmen an einem entsprechenden Projekt zu arbeiten. Der von Marvell entwickelte Chip soll dabei in der KI- und Cloud-Infrastruktur zum Einsatz kommen – der IP-Domäne von Marvell. Zudem soll er Bestandteil eines Beschleuniger-Plattform (XPU) sein. Marvell entwickelt unter... [mehr]

Marvell verkündet heute, dass man in Zusammenarbeit mit TSMC den ersten funktionsfähigen, in 2 nm gefertigten Chip hergestellt hat. Im Frühjahr 2024 verkündeten beide Unternehmen an einem entsprechenden Projekt zu arbeiten. Der von Marvell entwickelte Chip soll dabei in der KI- und Cloud-Infrastruktur zum Einsatz kommen – der IP-Domäne von Marvell. Zudem soll er Bestandteil eines Beschleuniger-Plattform (XPU) sein. Marvell entwickelt unter... [mehr]