Werbung

Im Rahmen der Bekanntgabe der neusten Quartalszahlen hat AMD auch die Präsentation für aktuelle und mögliche Investoren erneuert. Diese enthält einige interessante Details.

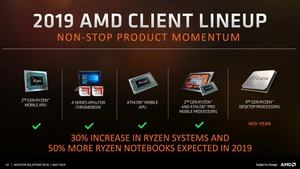

Während die dritte Generation der Ryzen-Threadripper-Prozessoren in der März-Version der Präsentation noch enthalten war, nennt AMD diese in der Mai-Version (PDF) nicht mehr. Allerdings überspring AMD die Nennung nicht einfach, sondern blendet im Falle der aktuellen Präsentation bei den Ryzen-Prozessoren der dritten Generation, die Mitte 2019 erscheinen sollen, einfach den weiteren Ausblick auf 2019 aus. Dies muss also nicht bedeuten, dass AMD die dritte Generation der Ryzen-Threadripper-Prozessoren einfach gestrichen hat.

Die EPYC-Prozessoren der zweiten Generation alias Rome werden laut AMD für das dritte Quartal 2019 erwartet. So richtig festlegen will sich das Unternehmen hier aber offenbar nicht. Einmal mehr betont man die Vorteile durch die Fertigung in 7 nm, das flexible Chiplet-Design und den Leistungsvorteil für Single-Socket-Systeme mit den bis zu 64 Kernen, die ein EPYC 7602 bieten wird.

Außerdem gibt AMD einen Ausblick auf die Entwicklung der weiteren Zen-Generationen. Alle Neuheiten, die in diesem Jahr im Bereich der Prozessoren auf den Markt kommen werden, basieren auf der Zen-2-Architektur. Die Entwicklung der Zen-3-Architektur befindet sich laut AMD "On Track". AMD befindet sich hier also innerhalb der eigenen Zielvorgaben – was auch immer das bedeutet. Die Zen-4-Architektur soll sich derzeit in der Design-Phase befinden.

Für die nächste EPYC-Generation bestätigt AMD ebenfalls die unter Milan geführte Entwicklung auf Basis der Zen-3-Architektur in der 7nm+-Fertigung.

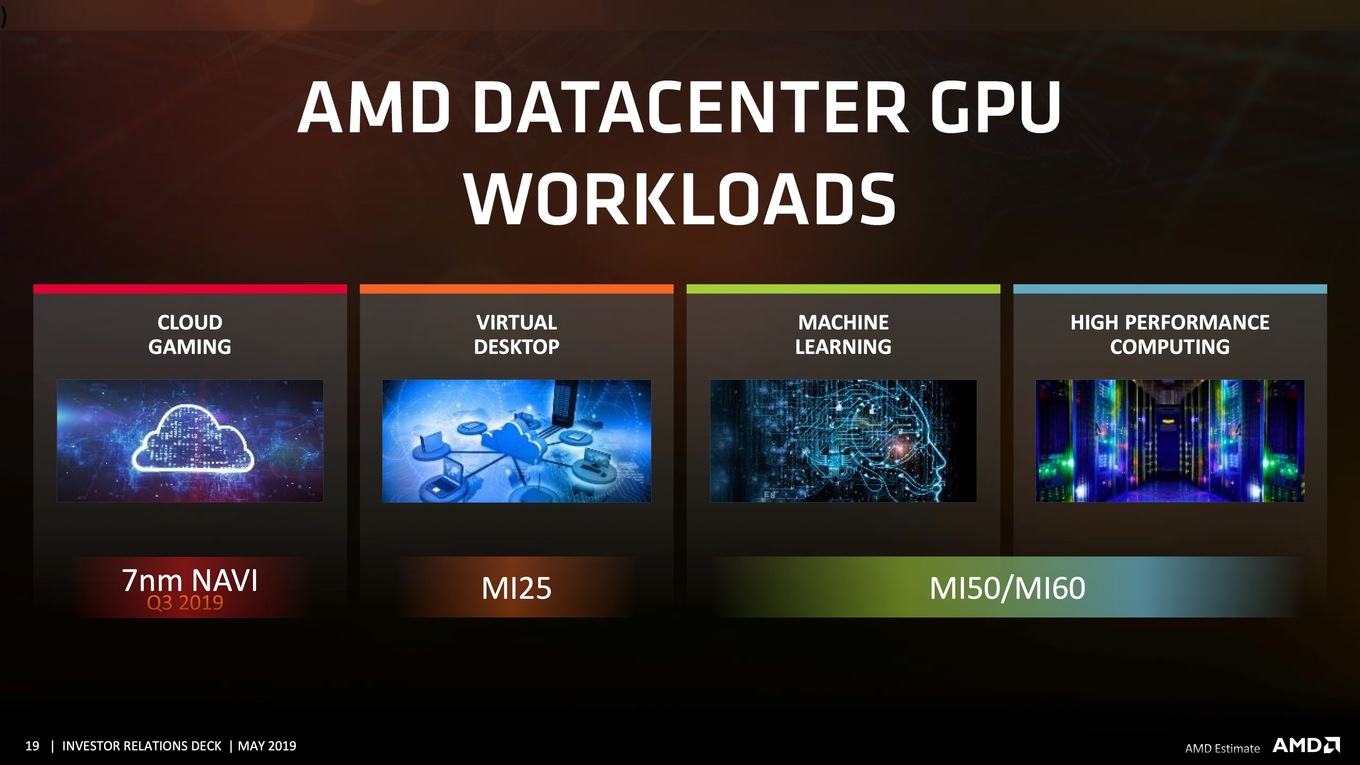

Für die GPU-Architekturen gibt es ebenfalls einen Ausblick. Die Grafikkarten auf Basis der Navi-Architektur werden im dritten Quartal erwartet. Dies hat Dr. Lisa Su im Rahmen der Bekanntgaben der Quartalszahlen noch einmal bestätigt. Hinsichtlich der preislichen Ausrichtung sollen sich die Karte unterhalb der Radeon VII bewegen. Zur Leistung will man jedoch noch nichts verraten.

Bei den GPUs ist AMDs Ausblick noch etwas wage. So ist Navi in 7 nm für 2019 geplant und Ende 2019 oder Anfang 2020 soll eine "Next-Gen"-Architektur erscheinen, die in 7nm+ gefertigt wird. Die von AMD gewählte Darstellung des Zeitstrahls lässt tatsächlich vermuten, dass es hier bald weitere Neuigkeiten gibt.

Darüber hinaus zeigt eine weitere Folie die Ambitionen im Datacenter-Bereich für die GPUs und hier auffällig ist die Nennung eines Cloud-Gaming-Dienstes, der die Navi-Architektur in 7 nm verwendet und ab dem dritten Quartal zum Einsatz kommen soll. Hier kann eigentlich nur Google Stadia gemeint sein.

Allerdings erwähnte Google den Einsatz von HBM2-Speicher und es macht eher den Anschein als käme hier die aktuelle Radeon-Instinct-Generation zum Einsatz. Navi wird aber wohl keinen HBM2- und stattdessen eher GDDR6-Speicher einsetzen – wenn man den Leaks und Bildern des ersten PCB-Designs Glauben schenken möchte.

Update:

Über das Wochenende entbrannte bei bei uns im Forum aber auch in den Kommentarspalten diverser anderen Seiten eine Diskussion über das Fehlen der Ryzen-Threadripper-Prozessoren der 3. Generation in der neusten Präsentation von AMD. Wir wollen dies aber noch einmal etwas einordnen.

In der Investoren-Präsentation fehlen unter dem Punkt "2019 AMD Client Lineup" alle Einträge, die noch im März diesen Jahres auf die Ryzen-Threadripper-Prozessoren der 3. Generation verwiesen haben. AMD nennt in der aktuellen Version der Präsentation nach den Ryzen-Desktop-Prozessoren der 3. Generation einfach keinerlei weitere Produkte. Dies muss aber nicht zwangsläufig bedeuten, dass es keine Ryzen-Threadripper-Prozessoren der 3. Generation in diesem Jahr geben wird. Diese könnten einfach später erscheinen und liegen zunächst einmal nicht im Fokus von AMD.

Auf einen Unterschied zur Positionierung im Vergleich zur Vergangenheit wollen wir aber hinweisen: Die Ryzen-Threadripper- und EPYC-Prozessoren der 1. Generation basierten zwar auf dem gleichen Chip, verwendeten aber unterschiedliche Steppings. Die Ryzen-Threadripper-Prozessoren verwendeten das B1-Stepping, während die EPYC-Prozessoren bis heute das neuere B2-Stepping verwenden. Das Gegenstück der Ryzen-Threadripper-Prozessoren der 2. Generation mit Zen+-Architektur gab es bei den EPYC-Prozessoren nicht. Erst mit der Zen-2-Architektur sind die Workstation- und Server-Prozessoren wieder auf gleichem (architektonischen) Stand. Ob auch hier wieder unterschiedliche Steppings verwendet werden, ist aktuell nicht bekannt.

Bisher hat AMD nach eigener Aussage immer die besten Chips für die Ryzen-Threadripper-Prozessoren verwendet. Für diese und die EPYC-Prozessoren wird AMD sicherlich eine Gewichtung vornehmen müssen und in diesem Jahr scheint klar die Serversparte im Fokus zu stehen. Insofern wäre es nicht verwunderlich, wenn sich AMD zunächst einmal auf den Servermarkt konzentriert, zumal mehr als 32 Kerne selbst für eine Worktstation nur noch schwer zu rechtfertigen sind. Die Anzahl der Anwendungen, die von derart vielen Kernen profitieren, lassen sich in der Praxis mit einer Hand abzählen. Dies hat auch unser Test des Intel Xeon W-3175X mit 28 Kernen gezeigt.

Wir werden einfach abwarten müssen ob und wann sich AMD zu den Ryzen-Threadripper-Prozessoren der 3. Generation äußert.