High Bandwidth Cache Controller

Werbung

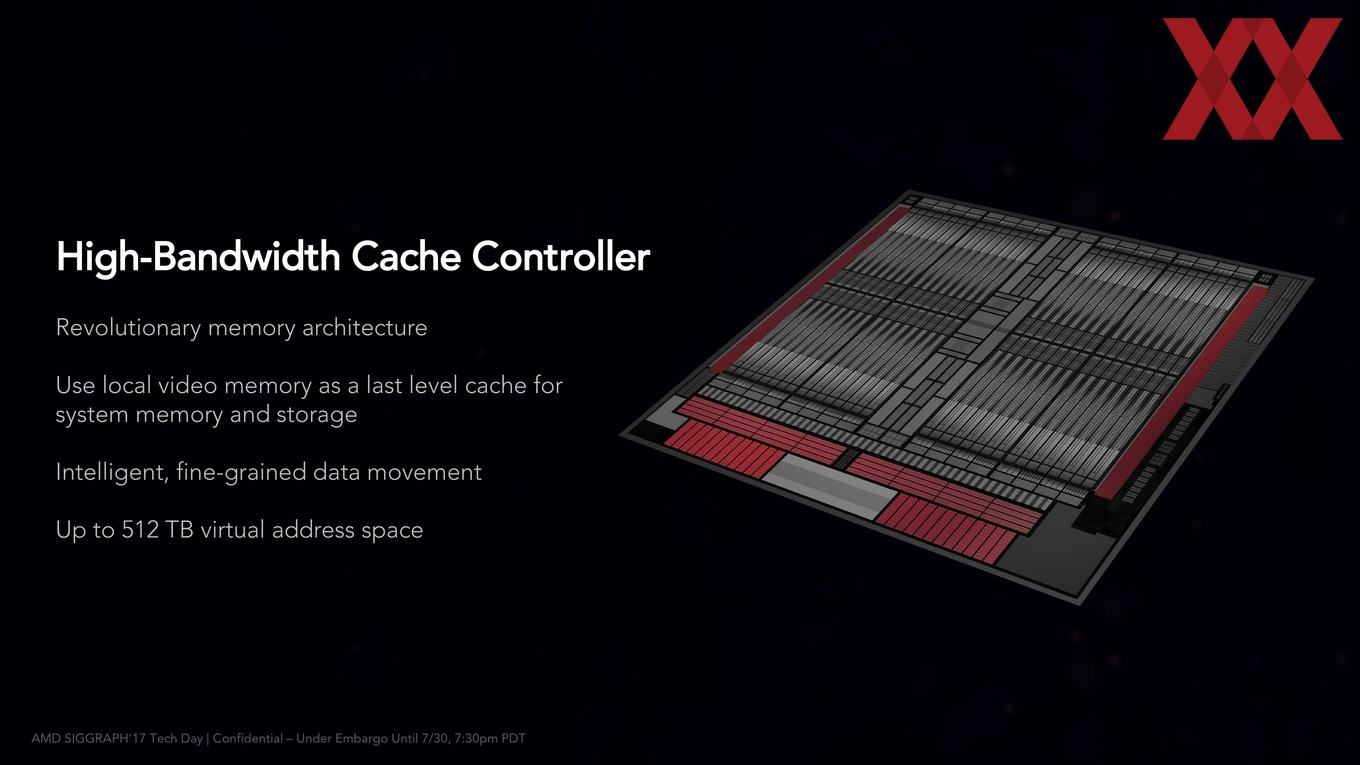

Für den HBM2-Speicher eine wichtige Rolle spielt der High Bandwidth Cache Controller (HBCC), der neben dem HB Cache (so benennt AMD den Grafikspeicher auf den Vega-Karten) auch angebundenen Massenspeicher (SSDs) und den Arbeitsspeicher verwalten kann. Insgesamt kann der HBCC 512 TB an virtuellem Adressraum verwalten. 49 Bit können als Shared Memory auf alle GPUs in einem System verteilt werden. Dazu werden Speicherpools angelegt. 256 TB kann ein einzelner physikalischer Speicher theoretisch groß werden.

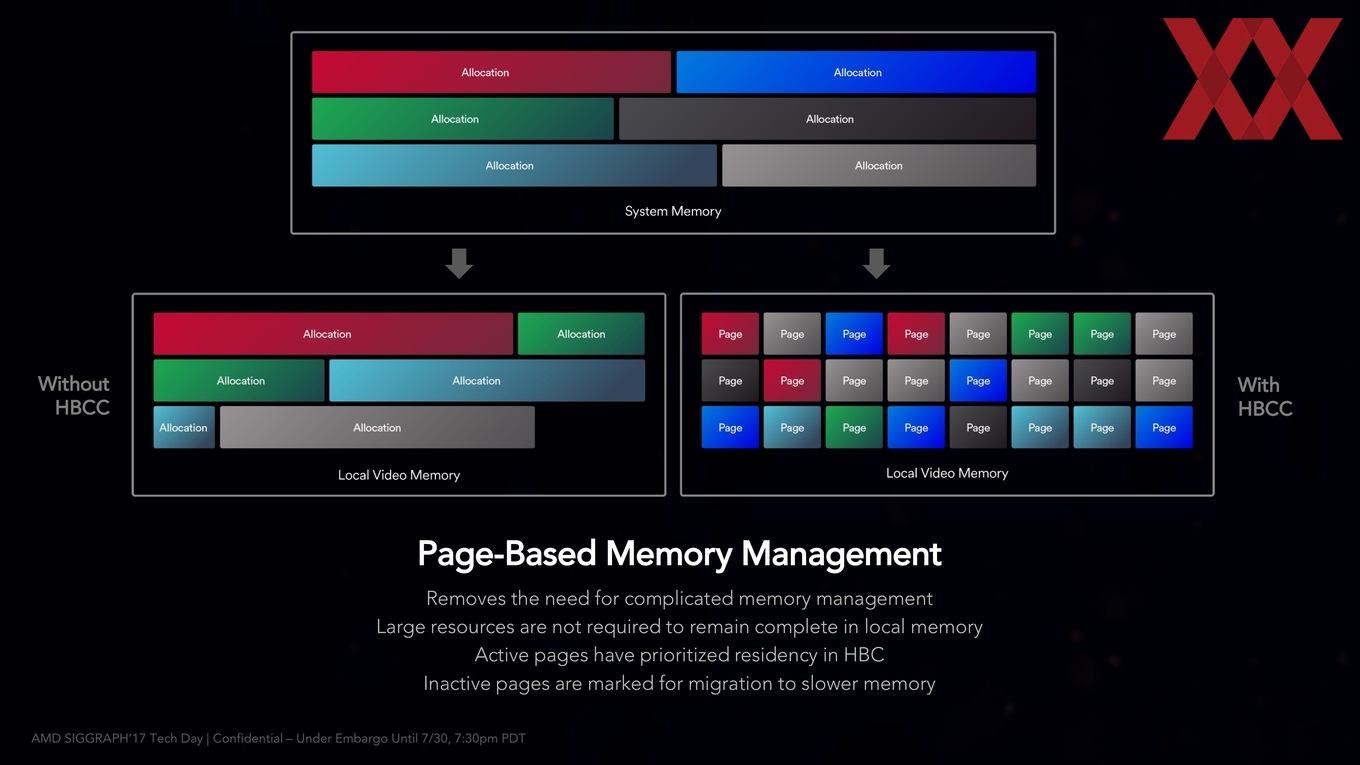

Zusammen mit dem HBCC führt AMD ein Page Based Memory Management ein. Daten liegen nicht mehr als große zusammenhängende Pakete im Speicher, sondern dieser ist in Pages aufgeteilt. Diese kleineren Pakete lassen sich schneller abrufen und nicht verwendete Daten können vom schnellen HBM2 in langsameren Speicher übertragen werden. Schaut man sich die Nutzung der Daten im Grafikspeicher an, stellt man fest, dass nur etwa 50 % der Daten im Grafikspeicher tatsächlich von der GPU genutzt werden.

Hat nun nicht die Game-Engine die Kontrolle über den Grafikspeicher, sondern der HBCC, können häufig benötigte Pages im schnellen Speicher verbleiben und hier zudem priorisiert werden. Die Größe dieser Pages ist variabel und hängt von den jeweiligen Daten ab. AMD sieht Page-Größen von 2 MB, 1 MB, 512 kB, 256 kB, ... usw. vor.

Es ist aber nicht so, dass alle Radeon RX Vega standardmäßig mit dem HBCC arbeiten. Der derzeitige Standardfall sieht noch eine Speicherverwaltung durch die Spiele selbst vor. Hier kann AMD durch den Treiber und den HBCC keinerlei Kontrolle übernehmen. Erst wenn diese vom Entwickler an AMD durch eine Option im Spiel übergeben wird, kann der HBCC aktiv werden. Dieser Standardfall ohne HBCC wird als Exclusive Cache Mode benannt. Im Inclusive Cache Mode kann der HBCC den HBM2 und Arbeitsspeicher gemeinsam verwenden und übernimmt außerdem die Kontrolle der Zuteilung.

Auf einer Radeon RX Vega mit 8 GB HBM2 bedeutet dies im Extremfall, dass selbst eine Speicherbelegung von 27 GB an Daten und ein Echtzeit-Rendering mit 500 Millionen Polygonen im Speicher gehalten und verarbeitet werden können. Der Nutzer hat dazu im Treiber die Möglichkeit, einen virtuellen Speicher aus Kombination der 8 GB an HBM2 plus dem zur Verfügung stehenden Arbeitsspeicher zu erstellen. Dies erfolgt über einen Schiebregler.

Draw Stream Binning Rasterizer

Änderungen hat es zudem bei der Pixel Engine gegeben. Diese kann nun neue sogenannte Draw Stream Binning Rasterizer ausführen, die für eine bessere Kompression der vorhandenen Daten sorgen. Damit soll der Speicherbedarf reduziert werden, was bei der Übertragung dieser Daten aus und in den Speicher Vorteile bei der Geschwindigkeit bringt. In einer Szene wird jedes Objekt nacheinander berechnet, dies alles muss durch den Rasterizer – ob sichtbar oder nicht spielt dabei zunächst einmal keine Rolle. Durch den Draw Stream Binning Rasterizer können Pixel entfernt werden, die nicht sichtbar sind. Ein Shading ist in diesem Fall nicht mehr notwendig. Dadurch wird Speicherkapazität und Speicherbandbreite eingespart. In bisherigen GPU-Architekturen von AMD ist der Pixel- und Texturspeicher nicht kohärent ausgelegt und musste daher teilweise doppelt verwendet werden. Mit der Vega-Architektur nutzen die Geometry Pipeline, die Compute Engine und die Pixel Engine den zur Verfügung stehenden L1- und L2-Cache parallel. Dies gilt auch für die Render Backends.

Der Draw Stream Binning Rasterizer ist nicht immer aktiv. AMD bzw. der Treiber entscheidet, bei welchem Spiel oder bei welcher Anwendung er aktiviert wird. Damit soll verhindert werden, dass es in einigen wenigen Spielen zu Einschränkungen in Form von geringerer Leistung kommt. Der Nutzer wird nicht merken, ob DSBR aktiv ist oder nicht. AMD denkt aber darüber nach, eine Treiberoption anzubieten.

Der Einsatz des Draw Stream Binning Rasterizer wird die Leistung in bestimmten Szenarien deutlich steigern können. Dies gelingt vor allem durch die Einsparung von Berechnungen durch die Erkennung der Überlappungen. Auch dazu stellte AMD einige Werte vor.

Display Engine

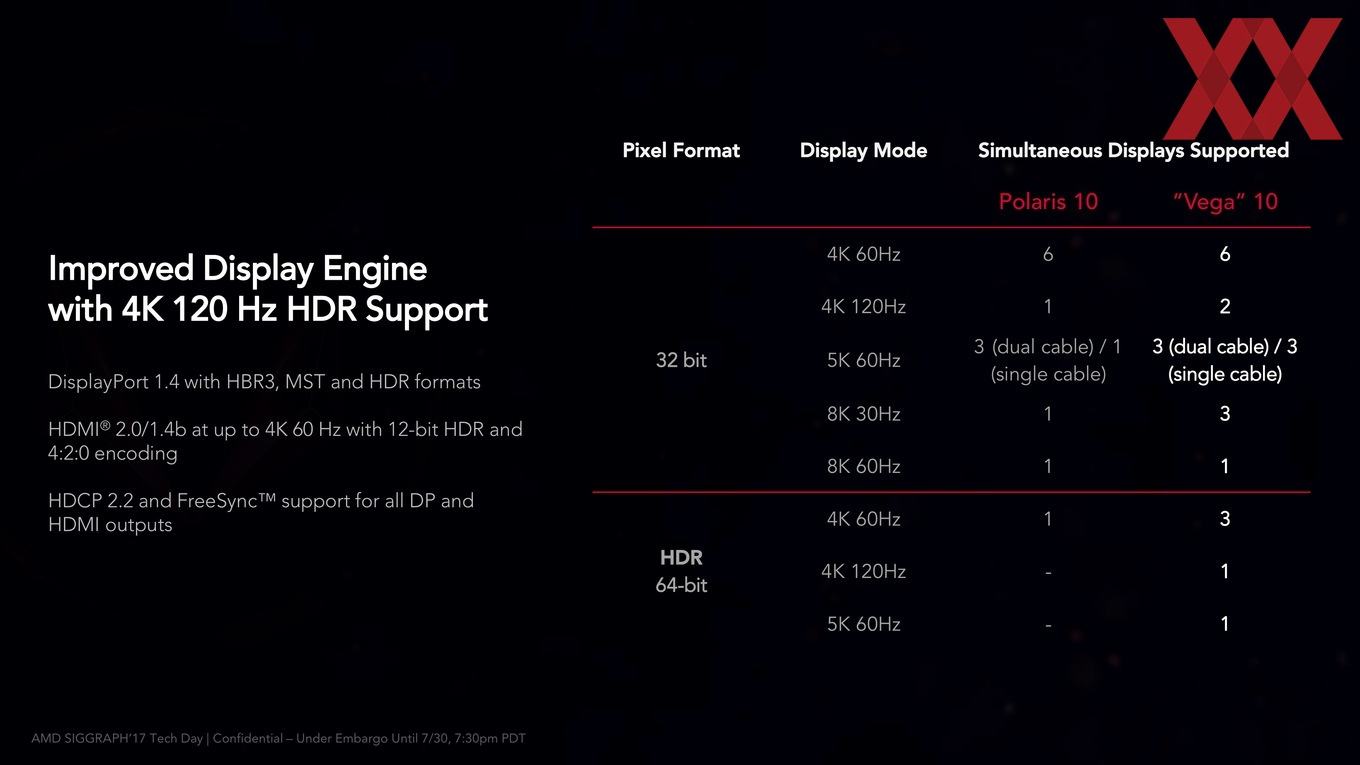

Die Display Engine der GPU wurde mit der Vega-Architektur leicht überarbeitet. Wir sehen allerdings nicht die großen Sprünge bei der Unterstützung neuer Standards, wie dies bei den vorherigen Architekturen öfter der Fall war.

DisplayPort 1.4 unterstützt auf den Vega-Karten nun den erweiterten Farbraum HBR3, MST für HDR. HDMI 2.0 ermöglicht eine UHD-Auflösung bei 60 Hz mit 12 Bit HDR und einen 4:2:0-Encoding. HDCP 2.2 und FreeSync werden auf allen DisplayPort- und HDMI-Ausgängen unterstützt.

Die Anzahl der Displays, die gleichzeitig mit bestimmten Auflösungen angesteuert werden können, hat sich ebenfalls erhöht.