Werbung

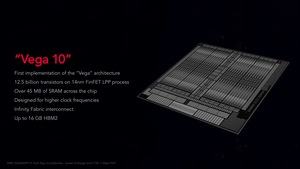

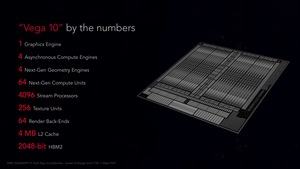

Wie bereits erwähnt, fertigt AMD die Vega-10-GPU in 14 nm im FinFET-Design. Insgesamt 12,5 Milliarden Transistoren sind in der GPU vorhanden und damit ist diese in etwa so komplex wie NVIDIAs GP102 auf der GeForce GTX 1080 Ti. Insgesamt verteilen sich 45 MB an SRAM auf der GPU und AMD hat den L2-Cache auf 4 MB verdoppelt. Im Folgenden wollen wir uns einige der neuen Komponenten der Vega-Architektur genauer ansehen.

High Bandwidth Memory der zweiten Generation

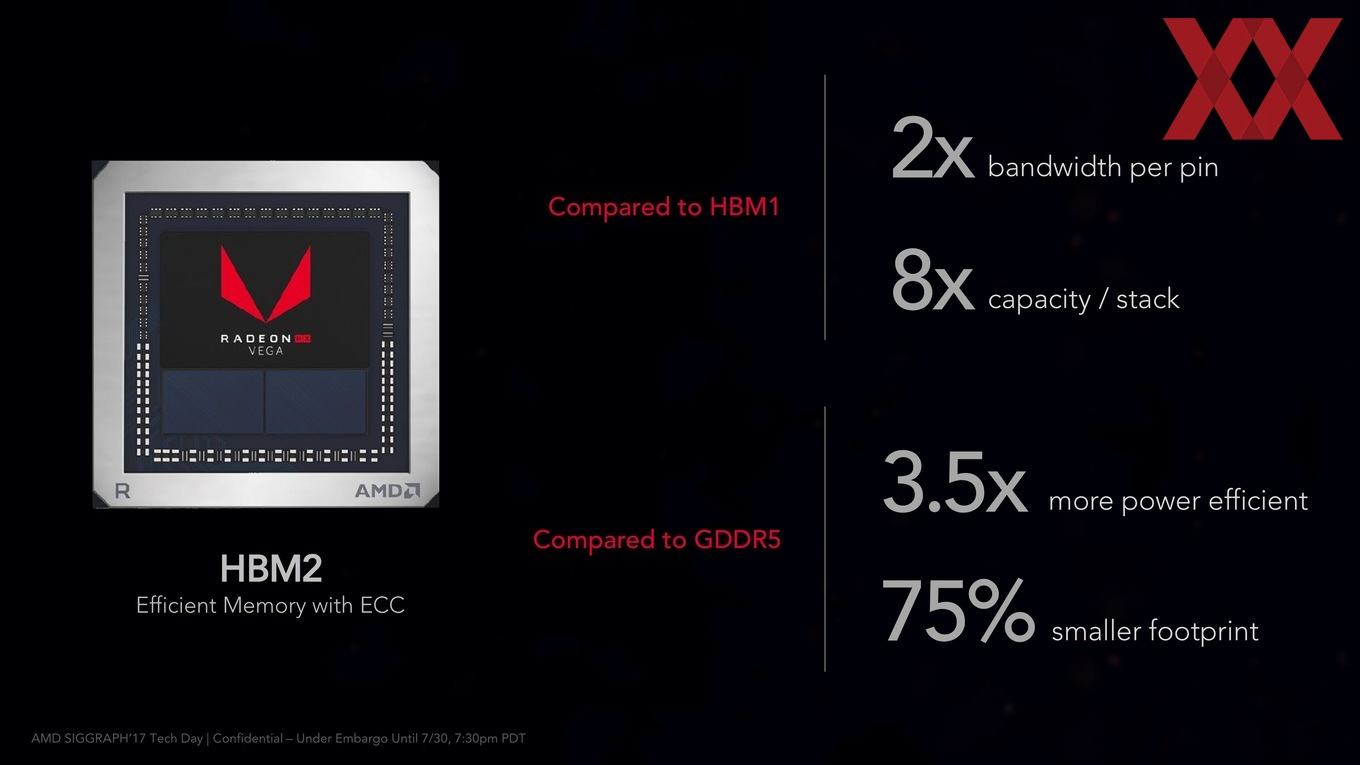

Zunächst einmal aber zum verwendeten Speicher. AMD setzt auf HBM der zweiten Generation. Die Verwendung von AMD als Grundbaustein des Designs der Vega-Architektur dürfte nicht ganz frei von Kritik sein, denn die Entwicklung und Fertigung von HBM2 hat sich nicht so entwickelt, wie AMD und NVIDIA dies prognostiziert haben. NVIDIA hat allerdings den Vorteil, dass man sich im Consumerbereich nicht derart abhängig von HBM2 gemacht hat und derzeit seine GPUs noch mit GDDR5X koppelt.

Bei AMD sieht dies anders aus. Die Vega-Architektur ist klar auf die Verwendung von HBM2 ausgelegt und so musste AMD auch sicherlich einige Verzögerungen hinnehmen, da die Entwicklung und Fertigung von HBM2 nicht in den Schritten erfolgt, wie man das geplant hatte.

Doch HBM2 soll, was den Speicherausbau betrifft, im Unterschied zu HBM1 deutlich flexibler sein. Spezifiziert ist HBM2 in Speicherstacks zu 2 (2Hi HBM2), 4 (4Hi HBM2), 8 GB (8Hi HBM2) sowie 16 GB (16Hi HBM2). Bisher haben SK Hynix und Samsung als Hersteller von HBM2 aber nur bis zu 8Hi HBM2 in der Produktion vorgesehen und auch vorgestellt. Ob AMD nun auf HBM2-Speicher von SK Hynix oder Samsung setzt, ist unklar.

16Hi HBM2 sind theoretisch bereits spezifiziert und damit umsetzbar. Je nachdem, wie viele Speicherstacks nun zum Einsatz kommen, kann der Speicherausbau und dessen Anbindung unterschiedlich ausgeführt werden. NVIDIA setzt bei der Tesla V100 auf vier Speicherstacks mit jeweils 4 GB, also 16 GB insgesamt. AMD sieht für die Radeon RX Vega einen Ausbau mit zweimal 4 GB, also 8 GB insgesamt vor.

Einige Vorteile des High Bandwidth Memory kennen wir bereits von der ersten Generation, die auf der Radeon R9 Fury X zum Einsatz kommt. Hier liegt die Speicherbandbreite mit 512 GB/s zwar auch schon auf einem recht hohen Niveau, schon damals war es aber wichtig festzuhalten, dass der HBM1 um den Faktor zwei effizienter, weil sparsamer, bei der Leistungsaufnahme ist. Um den Faktor 3,5 soll HBM2 im Vergleich zu GDDR5-Speicher effizienter sein. Hinzu kommt, dass der High Bandwidth Memory auf einem Interposer direkt neben der GPU und damit im GPU-Package platziert wird. Damit nimmt der Speicher deutlich weniger Platz auf dem PCB ein. AMD spricht hier von Einsparungen um 75 %.

Diese Vorteile gelten natürlich auch für die Radeon RX Vega. Aufgrund der Verwendung von nur zwei Speicherstacks und den damit verbundenen 2.048 Bit für das Speicherinterface ergibt sich eine Speicherbandbreite, die mit 484 bzw. 410 GB/s nur geringfügig langsamer ist.

Next Generation Compute Unit

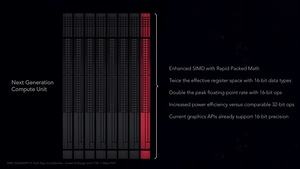

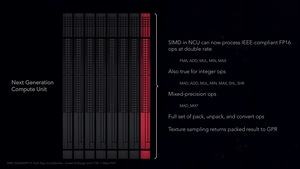

AMD hat die Shadereinheiten innerhalb der Vega-Architektur im Vergleich zu Polaris in weiten Teilen verbessert. Die wichtigsten Punkte sind die folgenden:

- verbessertes SIMD mit Rapid Packed Math

- 16 Bit Register doppelt so effizient

- 16 Bit Floating Point doppelt so schnell

- 32 Bit Effizienz verbessert

- IEEE2008 Kompatibilität hergestellt

- FP16 und Integer Ops mit doppelter Datenrate

- Mixed-Precision OPs

- Pack, Unpacked und Convert Ops

- Texture Sampling wird als Packed Data zurückgegeben

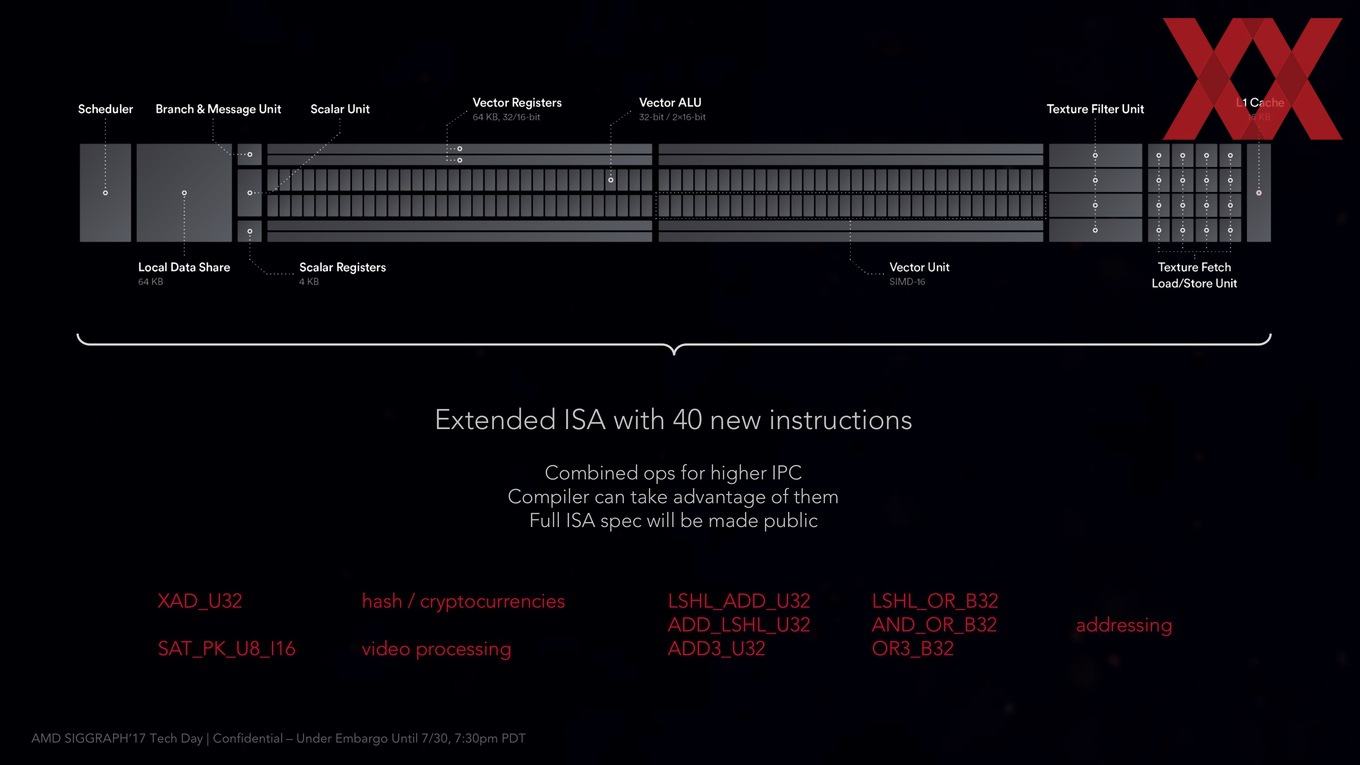

Dazu hat AMD eine neue Instruction Set Architecture (ISA) erstellt, die rund 40 neue Instruktionen enthält. Einige davon sind in der obigen Auflistung bereits zu finden, einige andere ermöglichen das Ausführen von 512 8-Bit Operationen pro Takt (QSAD und MQSAD Instructions), 256 16-Bit Operationen pro Takt und 128 32-Bit Operationen pro Takt. All diese Maßnahmen führen dazu, das die Vega-Architektur eine höhere IPC-Leistung (Instructions per Cycle) erreicht. Da AMD die ISA öffentlich macht, können auch Compiler von diesen neuen Instruktionen profitieren und diese anwenden.

Wie bereits erwähnt, verwendet AMD in der Vega-Architektur einen auf 4 MB verdoppelten L2-Cache im Vergleich zur Polaris-Architektur. Dieser größere L2-Cache macht es weniger häufig notwendig, dass Daten in und aus dem HBM2 heraus in den L2-Cache übertragen werden müssen. Zudem bekommen den Render Backends direkten Zugriff auf den L2-Cache. Das dazugehörige SRAM-Design und dessen Auslegung hat man von der Zen-Architektur übernommen und soll für eine um 18 % geringe Chipfläche und eine 43 % geringere Leistungsaufnahme in diesem Bereich sorgen.

Ein Ziel der Vega-Architektur war es außerdem, höhere Taktraten zu erreichen und hier spielen die NCUs eine wichtige Rolle. AMD stattet diese mit kürzeren Signalpfaden für geringere Latenzen aus und verwendet eine ALU mit einer 4-stufigen Pipeline. Drei NCUs teilen sich einen Instruction- und Data-Cache. All diese Maßnahmen sollen dazu beigetragen haben, dass eine wassergekühlte Radeon RX Vega 64 mit einem Boost-Takt von 1.750 MHz ausgeliefert werden kann.

Primitive Shaders und Rapid Packed Math

Neu innerhalb der Geometry Pipeline ist, dass Vertex Shader und Geometry Shader nicht mehr getrennt voneinander behandelt werden. Stattdessen können sogenannte Primitive Shader eingesetzt werden. Diese beinhalten Vertex- und Geometry-Berechnungen, lassen sich über einen verbesserten Load Balancer besser auf die zur Verfügung stehenden Hardware-Ressourcen verteilen. Damit sollen die Shadereinheiten besser ausgelastet werden. Die GPU überwacht sich bzw. die Auslastung ständig selbst und versucht die ideale Verteilung zu erreichen.

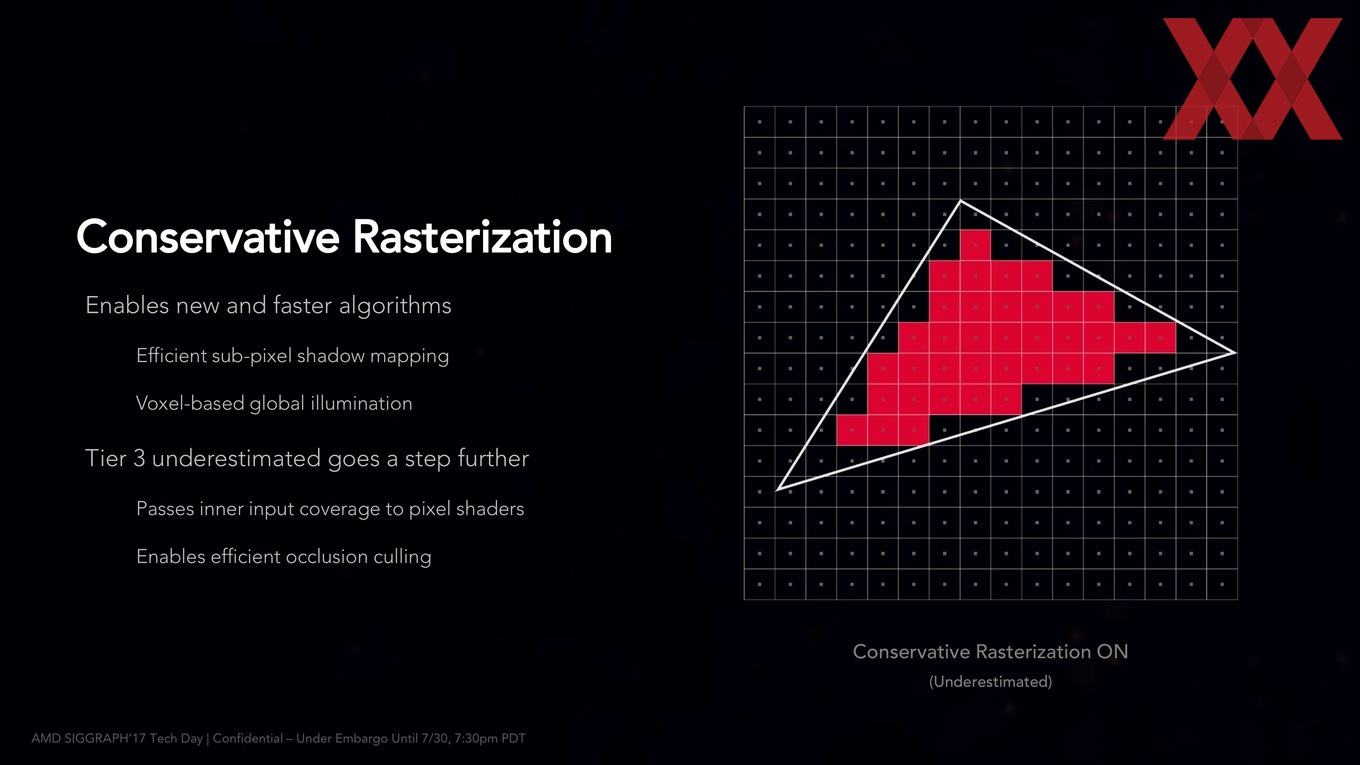

Diese Primitive Shaders kommen unter anderem für die Conservative Rasterization zum Einsatz. AMDs Vega-GPU beherrscht als bisher einzige diskrete GPU die DirectX 12_1 Conservative Rasterization Tier 3. Die Conservative Rasterization ermöglicht ein Shadowmapping im Subpixel-Bereich und zudem eine Voxel Based Global Illumination. Tier 3 ermöglicht die Aufteilung des inneren Bereiches, sodass diese direkt an die Pixel Shader weitergegeben werden können.

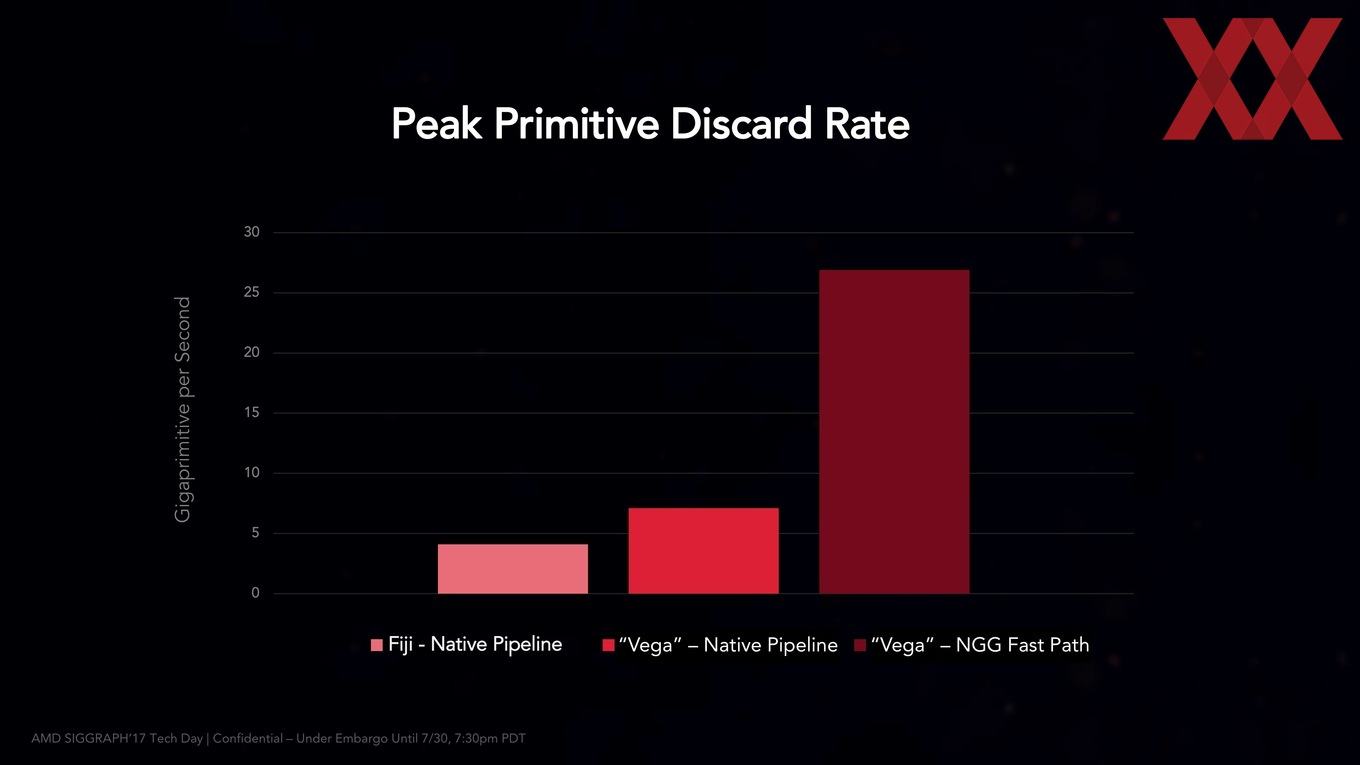

AMD nennt außerdem einige Werte zu den Primitive Shadern. Im Vergleich enthalten sind die Fiji-GPU mit nativer Pipeline, die Vega-GPU mit nativer Pipeline und die Vega NGG-Fast-Path-Implementierung. Die Balken lassen sich in dieser Form natürlich nicht auf die Spieleleistung übertragen. Die Frage ist, welche Auswirkungen dies auf die Leistung in der Praxis hat. NGG Fast Path wird zum Start wohl nicht verfügbar sein.