Werbung

Die EPYC-Prozessoren der zweiten Generation alias Rome sind bereits offiziell vorgestellt worden. Die dritte Generation der Ryzen-Threadripper-Prozessoren wird auf der gleichen Hardware basieren – verwendet also auch einen zentralen I/O-Die und bis zu acht Compute-Chiplets mit wiederum jeweils acht Kernen. Im November sollen die ersten der neuen Ryzen-Threadripper-Prozessoren auf den Markt kommen.

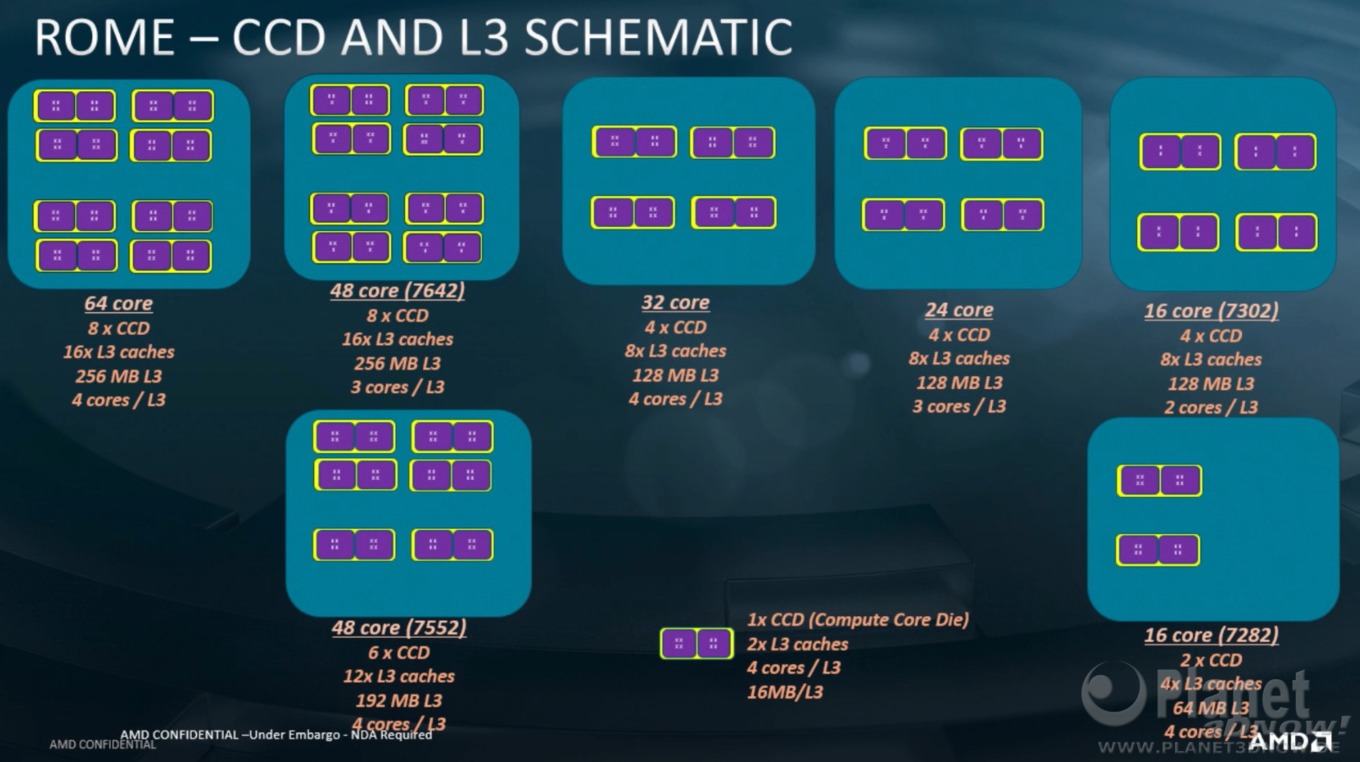

Ein Detail welches bisher noch wenig Beachtung findet ist, wie viele aktive Chiplets mit jeweils wie vielen aktiven Kernen für die einzelnen Modelle verwendet werden. Die EPYC-Prozessoren auf Basis von Rome sind in Varianten mit 16, 24, 32, 48 und 64 Kernen verfügbar. Bei den Ryzen-Threadripper-Prozessoren startet AMD mit 24 Kernen.

Auf dem HPC-AI Advisory Council in Leicester hat AMD nicht nur einige Details zur Zen-3-Architektur sowie den dazugehörigen EPYC-Prozessoren auf Basis von Milan verraten, sondern auch das Layout für die Verteilung der CCDs und des L3-Caches für die verschiedenen EPYC-Varianten. Das Video dazu ist inzwischen offline, die Kollegen von Planet3DNow! haben aber die dazugehörige Präsentation bzw. die Screenshots daraus.

Der Aufstellung zufolge gibt es für zwei EPYC-Modelle mit gleicher Anzahl an Kernen, aber einem unterschiedlichen L3-Cache, jeweils zwei unterschiedliche Layouts. Die 64 Kerne werden, wie nicht anders zu erwarten ist, mit acht CCDs zu jeweils acht Kernen realisiert. Es gibt pro CCD zwei L3-Abschnitte, den sich immer vier Kerne teilen. 16x 16 MB an L3-Cache ergeben die 256 MB an Gesamtkapazität, die zur Verfügung stehen.

Die 48-Kern-EPYCs gibt es mit acht (EPYC 7642) und sechs (EPYC 7552) aktiven CCDs. Bei nur sechs CCDs sind demzufolge auch nur 192 MB an L3-Cache verfügbar. Pro Kern steht also ein weniger großer L3-Cache zur Verfügung. Dafür verwendet AMD hier vollständig aktive CCDs mit 6 x 8 Kernen, während es beim EPYC 7642 8 x 6 Kerne sind – auf den acht CCDs sind jeweils zwei Kerne inaktiv.

Für die EPYC-Prozessoren mit 32 und 24 Kernen verwendet AMD immer vier aktive CCDs. Um auf 32 Kerne zu kommen müssen hier jeweils alle acht Kerne aktiv sein. Bei der 24-Kern-Variante sind wieder jeweils zwei Kerne nicht aktiviert, sodass wir bei 4 x 6 auf 24 Kerne insgesamt kommen. Der L3-Cache ist mit 8 x 16 = 128 MB immer gleich groß. Hier steht den 24 Kernen pro Kern wieder ein größerer L3-Cache zur Verfügung, als dies beim Modell mit 32 Kernen der Fall ist.

Für die EPYC-Prozessoren mit 16 Kernen gibt es wieder zwei Varianten. Eine besteht aus vier CCDs (EPYC 7302), bei denen jeweils vier Kerne aktiv sind. Auch hier haben wir also wieder 128 MB an L3-Cache und die Cache-Größe pro Kerne ist am höchsten. Eine zweite Variante (EPYC 7282) verwendet nur zwei aktive CCDs, in denen aber jeweils alle acht Kerne genutzt werden. Da aber nur die Hälfte an CCDs verwendet wird, wird die Größe des L3-Caches auf 64 MB halbiert.

Analog zu den bisherigen Chiplet-Designs von AMD, werden immer acht CCDs verbaut, aber nicht immer sind alle diese Chips auch aktiv. AMD wird hier defekte oder teildefekte Chips verwenden, um diese auf dem Package unterzubringen. Immer alle Chips im Package zu verbauen ist notwendig, damit der Heatspreader auch eine ausreichende Auflagefläche hat. Im Falle des EPYC 7282 wären sonst nur zwei von acht CCDs verbaut und würden den Heatspreader stützen. Den Druck des Kühlers könnte dieser kaum aufnehmen. AMD ist bisher bei den EPYC- und Ryzen-Threadripper-Prozessoren immer so verfahren. Einzig bei den neuen Ryzen-Prozessoren mit nur einem CCD ist auch wirklich nur ein CCD verbaut.

Was bedeutet dies für die Ryzen-Threadripper-Prozessoren

Die neuen Ryzen-Threadripper-Prozessoren starten mit einem Modell mit 24 Kernen. Ebenso wie bei einer Variante mit 32 Kernen ist der Aufbau hier unstrittig und wird analog zu den EPYC-Prozessoren erfolgen. Wir werden hier also vier CCDs mit einer unterschiedlichen Anzahl an aktiven Kernen sehen. Der L3-Cache dürfte immer 128 MB groß sein.

Gleiches gilt auch für einen potenziellen Ryzen-Threadripper-Prozessor mit 64 Kernen. Hier kann AMD nur acht CCDs mit jeweils acht Kernen einsetzen und kommt damit auch auf 256 MB an L3-Cache. Doch was macht man mit dem 48-Kerner? AMD hätte hier die Möglichkeit zwei verschiedene Designs zu verwenden. Ein Unterschied läge im Angebot an L3-Cache. Da der I/O-Die die Anbindung des Speicherinterfaces vornimmt und dieser dann die CCDs per Interconnect anbindet, dürfte sich kein großer Unterschied hinsichtlich der Speicheranbindung ergeben.

Die schematischen Zeichnungen geben in jedem Fall einen interessanten Einblick in den Aufbau und die Verteilung der CCDs und Kerne über die verschiedenen Varianten. Wie sich AMD bei den Ryzen-Threadripper-Prozessor bzw. beim 48-Kerner entscheiden wird, wird sich noch zeigen müssen.