Werbung

Das taiwanesische Branchenmagazin Commercial Times berichtet, dass NVIDIA mit dem KI-Chip der übernächsten Generation namens Feynman der erst Kunde von TSMC sein soll, der auf die Fertigung im A16-Prozess setzt. Dies stellt eine besondere Herausforderung dar, da die Chiphersteller für die allerneusten Prozesse üblicherweise auf deutlich kleinere Chips setzen.

Ein Blick auf die aktuellen KI-Chips bei NVIDIA zeigt: Man nutzt auf die eigenen Designs angepasste Designs, bleibt mit 4N aber einen Schritt hinter den neuesten Chips zurück. Diese bleiben den deutlich kleineren monolithischen Prozessoren, GPUs und Chiplets vorbehalten. Bei fast 100 Milliarden Transistoren und Flächen um die 800 mm² will man auf Nummer sicher gehen. Auch die Rubin-GPU, die gerade den Tape-Out hinter sich gebracht haben soll, wird auf eine angepasste N3P-Variante setzen, während zum gleichen Zeitpunkt auch schon die ersten in N2 gefertigten Chips im Band rollen. Unter anderem setzt AMD für seine CCDs mit Zen-6-Kernen auf N2 und ist damit einer der ersten Kunden – abseits der SoC-Kunden.

Mit der Fertigung in A16 soll auch TSMCs Lösung für eine rückseitige Stromversorgung (Backside Power Delivery Network, BSPDN) zum Einsatz kommen. Ursprünglich waren die von TSMC favorisierten Super Power Rail (SPR) schon für N2P geplant. Im vergangenen Jahr wurde verkündet, dass man diese Technik auf die A16-Fertigung verschiebt.

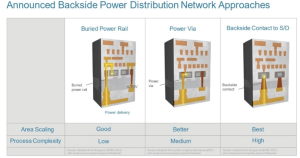

Ein BSPDN soll die Effizienz der Chips verbessern und das Design vereinfachen, da die Signal- und Strompfade von unterschiedlichen Seiten an die Transistoren herangeführt werden. Allerdings gibt es Unterschiede in der Umsetzung.

Die einfachste Methode sind die Buried Powe Rails, bei denen zwar eine rückseitige Versorgung stattfindet, in der untersten Metallebene aber immer noch eine frontseitige Lage zum Transistor hin verwendet wird. Die auch von Intel mit einer Fertigung in Intel 18A verwendeten PowerVias sind eine Art Zwischenlösung. Eine direkte Stromversorgung zu Source und Drain des Transistors ermöglichen die von TSMC verwendeten Super Power Rail. Damit sollen die Chips auch besonders effizient sein.

Der Verbrauch der KI-Chips wird dennoch steigen. Aktuell kommen die Blackwell-Lösungen schon auf 1.400 W. Mit Rubin und Rubin Ultra sollen es dann 2.300 W und mehr werden. Entsprechend gibt es vermehrt Berichte, NVIDIA arbeite mit verschiedenen Partnern auch Microchannel-Wasserkühlungslösungen, um die 2.000+ W noch beherrschen zu können.

Update:

Die Gerüchte aus Mitte September werden durch einen Bericht aus Korea bestärkt. NVIDIA wird voraussichtlich ab 2027 als erster Kunde TSMCs fortschrittlichsten A16-Prozess mit Backside Power Delivery Network (BSPDN) nutzen, zunächst für die Feynman-Generation. Damit weicht das Unternehmen erstmals von seiner bisherigen Strategie ab, ältere Prozessknoten zu bevorzugen, um Margen zu maximieren. Durch die Einführung des teureren 2-nm-Prozesses dürften die Produktionskosten ab 2027 deutlich steigen.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen