Ist halt nur das 1.45v Kit.Anhang anzeigen 1145292

Na, wer von euch hat die Dinger zurückgesendet?Wären immerhin knapp´80 € Ersparnis. ^^

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

[Sammelthread] Ryzen DDR5 RAM OC Thread

- Ersteller Reous

- Erstellt am

Ist im Prinzip nicht schlechter, wenn man Glück hatIst halt nur das 1.45v Kit.

seppelchen

Foto-Master of 03/11

- Mitglied seit

- 17.06.2005

- Beiträge

- 11.056

- Ort

- Bretten

- Desktop System

- X

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike X Edition (51/1000)

- Kühler

- Arctic Liquid Freezer lll 420

- Speicher

- G.Skill Trident Z5 RGB 48GB DDR5 @ 8000 CL36

- Grafikprozessor

- Zotac Gaming RTX 5090 AMP Extreme INFINITY

- Display

- Dell Alienware AW3423DWF

- SSD

- Crucial T710 SSD 4TB, PCIe 5.0 M.2

- Gehäuse

- DeepCool Morpheus

- Netzteil

- ASUS ROG Strix 1000P Platinum, 1000W

- Keyboard

- ASUS ROG Strix Flare II // Logitech MX Key

- Mouse

- ASUS ROG Harpe Ace Aim Lab Edition

- Betriebssystem

- Win 11

- Webbrowser

- Brave

- Sonstiges

- Edifier S351DB // UE4000

- Internet

- ▼1000 ▲50

Neue ZenTimings Beta.

Falls noch nicht gepostet wurde...

Neu z.B.

und

Falls noch nicht gepostet wurde...

Neu z.B.

Nitro on main window now!

und

VDDG display support in progress.

Induktor

Enthusiast

- Mitglied seit

- 03.11.2019

- Beiträge

- 3.579

- Laptop

- Lenovo Yoga Pro 7i - Intel-7 255H - 32GB LPDDR5x-8533 - 14,5" OLED (3000*1876) 120Hz - Samsung 990 Pro 2TB

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen-7 9800X3D (CO: +0/ per Core UV)

- Mainboard

- MSI X870E Carbon Wifi (A93)

- Kühler

- Arctic LF III 280 & 2x Toughfan 14 Pro + Noctua NA-IS1-14

- Speicher

- 32GB - 6200 MT/s (CL26-12-36-30 - tRFC 120ns)

- Grafikprozessor

- Gigabyte RTX 5080 Gaming OC (Shroud-Mod 3x T30)

- Display

- Alienware AW2725DF (OLED 360Hz) & AW2725QF (IPS 4K)

- SSD

- Samsung 990 Pro & 990 Evo+

- Gehäuse

- Open Benchtable V2 (vertikal)

- Netzteil

- Corsair AX850 (Titanium)

- Sonstiges

- Thermal Grizzly AM5 Frame

seppelchen

Foto-Master of 03/11

- Mitglied seit

- 17.06.2005

- Beiträge

- 11.056

- Ort

- Bretten

- Desktop System

- X

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike X Edition (51/1000)

- Kühler

- Arctic Liquid Freezer lll 420

- Speicher

- G.Skill Trident Z5 RGB 48GB DDR5 @ 8000 CL36

- Grafikprozessor

- Zotac Gaming RTX 5090 AMP Extreme INFINITY

- Display

- Dell Alienware AW3423DWF

- SSD

- Crucial T710 SSD 4TB, PCIe 5.0 M.2

- Gehäuse

- DeepCool Morpheus

- Netzteil

- ASUS ROG Strix 1000P Platinum, 1000W

- Keyboard

- ASUS ROG Strix Flare II // Logitech MX Key

- Mouse

- ASUS ROG Harpe Ace Aim Lab Edition

- Betriebssystem

- Win 11

- Webbrowser

- Brave

- Sonstiges

- Edifier S351DB // UE4000

- Internet

- ▼1000 ▲50

Der Defender springt nicht mehr an... und Nitro ist mit drinNeue ZenTimings Beta.

Falls noch nicht gepostet wurde...

RedF

Enthusiast

- Mitglied seit

- 07.03.2020

- Beiträge

- 5.698

- Ort

- am Main

- Desktop System

- Rechner

- Laptop

- Laptop

- Details zu meinem Desktop

- Prozessor

- Ryzen 7800X3D

- Mainboard

- ASrock X670E Taichi

- Kühler

- Core 1 360+1080 Radiator

- Speicher

- 32GB 6200MHz

- Grafikprozessor

- 7900XTX

- Display

- Samsung C32HG70

- SSD

- 2x960GB Corsair MP510 1x512GB Samsung PM961 1x2TB FireCuda

- HDD

- Seagate 4TB

- Opt. Laufwerk

- -

- Soundkarte

- GC7

- Gehäuse

- be quiet! 601 Silentbase / aufgesägt

- Netzteil

- Seasonic Prime 1000

- Keyboard

- logitech G815

- Mouse

- Xtrfy MZ1

- Betriebssystem

- W11

- Webbrowser

- Firefox

- Sonstiges

- 3D-Drucker: Qidi Plus 4, Ender 3V2 (war er mal)

Cool, WRPRE auf der main.

Beitrag automatisch zusammengeführt:

BTW kannst du mit WRPRE 3 bei tRDWR auf 15.Joa, schon ganz nett. PHY sind in der Info Tablle auch nebeneinander (war auch schon in der letzten Beta)

Anhang anzeigen 1145545

Induktor

Enthusiast

- Mitglied seit

- 03.11.2019

- Beiträge

- 3.579

- Laptop

- Lenovo Yoga Pro 7i - Intel-7 255H - 32GB LPDDR5x-8533 - 14,5" OLED (3000*1876) 120Hz - Samsung 990 Pro 2TB

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen-7 9800X3D (CO: +0/ per Core UV)

- Mainboard

- MSI X870E Carbon Wifi (A93)

- Kühler

- Arctic LF III 280 & 2x Toughfan 14 Pro + Noctua NA-IS1-14

- Speicher

- 32GB - 6200 MT/s (CL26-12-36-30 - tRFC 120ns)

- Grafikprozessor

- Gigabyte RTX 5080 Gaming OC (Shroud-Mod 3x T30)

- Display

- Alienware AW2725DF (OLED 360Hz) & AW2725QF (IPS 4K)

- SSD

- Samsung 990 Pro & 990 Evo+

- Gehäuse

- Open Benchtable V2 (vertikal)

- Netzteil

- Corsair AX850 (Titanium)

- Sonstiges

- Thermal Grizzly AM5 Frame

Ist das ne Frage? tRDWR 14 bei 6200 führt zu no boot. 15 bin ich mir jetzt gar nicht sicher, ob das ich schon mal probiert habe.kannst du mit WRPRE 3 bei tRDWR auf 15.

marc|nrw

Enthusiast

- Mitglied seit

- 22.12.2005

- Beiträge

- 1.713

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 9950X3D

- Mainboard

- MSI X870E Tomahawk

- Kühler

- Custom Loop - EK 360mm top,EK 280mm front, EK Quantum Kinetic 160 DDC, Bykski GPU Block, AC CPU

- Speicher

- 64GB - Patriot Viper DDR5 6000 CL30

- Grafikprozessor

- nvidia RTX 3090FE @ Bykski N-RTX3090FE-X-V2 Waterblock

- Display

- Samsung G9 OLED 49" DWQHD 1000R + Acer 34" WQHD 180hz 1800R

- SSD

- WD Black 2TB nvme + Samsung Evo 512GB nvme

- Opt. Laufwerk

- NA

- Soundkarte

- onboard

- Gehäuse

- Fractal Design Meshify S2

- Netzteil

- Be quiet! Pure Power 12M 850W

- Keyboard

- Cherry

- Mouse

- G502 Hero

- Betriebssystem

- WIN11

- Sonstiges

- SIM RIG ALU CUSTOM, MOZA R12 DD, MOZA CS2VP, SIMAGIC GT NEO , SIMLAB XP1 Pedals

- Internet

- ▼1000Mbit ▲40Mbit

nice kannst du mal einen Aida test posten ?

Beitrag automatisch zusammengeführt:

Anhang anzeigen 1145292

Na, wer von euch hat die Dinger zurückgesendet?Wären immerhin knapp´80 € Ersparnis. ^^

ich habe die 2x24Gb ( 1,35V ) für 330€ bekommen, ist schon nicht günstig aber du bezahlst halt den BIN ist nun mal so.

RediMischa

Enthusiast

- Mitglied seit

- 08.06.2008

- Beiträge

- 2.852

- Ort

- Vorarlberg

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800X3D

- Mainboard

- Asus ROG Strix X670E-A

- Kühler

- Custom WaKü

- Speicher

- 48GB G.Skill Trident Z5 NEO RGB DDR5-6400 28-37-32-44

- Grafikprozessor

- MSI GeForce RTX 4090 Suprim X

- Display

- LG OLED 42" C27LA

- SSD

- Samsung 990 PRO 2TB + 4TB / Western Digital SN850X 2x 4TB

- Soundkarte

- FiiO K11

- Gehäuse

- Corsair Obsidian 900D

- Netzteil

- Corsair AX1500i

- Keyboard

- SteelSeries Apex Pro TKL 2023

- Mouse

- Razer Viper V2 Pro white

- Betriebssystem

- Windows 10 Home

- Webbrowser

- Mozilla Firefox

- Internet

- ▼300 MBit ▲50 MBit

Schreibfehler oder gewollt?ich habe die 2x24Gb ( 1,35V ) für 330€ bekommen

1,35v wäre das CL28 Kit.

Die CL26 (1,45v) Kit`s gab es in den letzten Wochen/Tagen für ~290-310€ (je nach Farbe).

Hatte auch ein CL26 Kit hier, ging schlechter als mein CL28 Kit

marc|nrw

Enthusiast

- Mitglied seit

- 22.12.2005

- Beiträge

- 1.713

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 9950X3D

- Mainboard

- MSI X870E Tomahawk

- Kühler

- Custom Loop - EK 360mm top,EK 280mm front, EK Quantum Kinetic 160 DDC, Bykski GPU Block, AC CPU

- Speicher

- 64GB - Patriot Viper DDR5 6000 CL30

- Grafikprozessor

- nvidia RTX 3090FE @ Bykski N-RTX3090FE-X-V2 Waterblock

- Display

- Samsung G9 OLED 49" DWQHD 1000R + Acer 34" WQHD 180hz 1800R

- SSD

- WD Black 2TB nvme + Samsung Evo 512GB nvme

- Opt. Laufwerk

- NA

- Soundkarte

- onboard

- Gehäuse

- Fractal Design Meshify S2

- Netzteil

- Be quiet! Pure Power 12M 850W

- Keyboard

- Cherry

- Mouse

- G502 Hero

- Betriebssystem

- WIN11

- Sonstiges

- SIM RIG ALU CUSTOM, MOZA R12 DD, MOZA CS2VP, SIMAGIC GT NEO , SIMLAB XP1 Pedals

- Internet

- ▼1000Mbit ▲40Mbit

Schreibfehler oder gewollt?

1,35v wäre das CL28 Kit.

Die CL26 (1,45v) Kit`s gab es in den letzten Wochen/Tagen für ~290-310€ (je nach Farbe).

Hatte auch ein CL26 Kit hier, ging schlechter als mein CL28 Kit

ah ok dachte die hätten 1,35v, kann auch 1,45v im EXPO sein ! bin mir nicht sicher da ich kein EXPO betreibe.

Es sind aber definitv die CL26er M-DIE die gehen auch sehr gut ab.

Ich bin jedoch aktuell schon mit meinem 6400er CL28 @1,4v 1:1 Setting happy, dafür hätten es bestimmt auch günstigere getan ^^

CL26 zu CL28 bringt eh so gut wie gar nichts ausser das du deutlich mehr Spannung geben musst.

Beitrag automatisch zusammengeführt:

Ist halt nur das 1.45v Kit.

gibt es die CL26 jetzt auch mit 1,35 oder nicht ?

Ich steig nicht mehr durch...

NightFly2

Urgestein

- Mitglied seit

- 11.09.2011

- Beiträge

- 2.728

- Details zu meinem Desktop

- Prozessor

- i9 9900k@5Ghz

- Mainboard

- Asus Apex XI

- Kühler

- Custom wasserkühlung

- Speicher

- F4-3600C16D-32GTRS @4000 CL16

- Grafikprozessor

- ASUS GeForce RTX 3090 ROG STRIX OC GAMING

- Display

- LG OLED48CX8

- SSD

- Samsung 970 EVO 1 TB NVMe M.2

- Gehäuse

- Phanteks Enthoo primo

- Netzteil

- Seasonic Snow Silent 1050W

- Betriebssystem

- Win 10 Pro

Nein gibt es nichtgibt es die CL26 jetzt auch mit 1,35 oder nicht ?

seppelchen

Foto-Master of 03/11

- Mitglied seit

- 17.06.2005

- Beiträge

- 11.056

- Ort

- Bretten

- Desktop System

- X

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike X Edition (51/1000)

- Kühler

- Arctic Liquid Freezer lll 420

- Speicher

- G.Skill Trident Z5 RGB 48GB DDR5 @ 8000 CL36

- Grafikprozessor

- Zotac Gaming RTX 5090 AMP Extreme INFINITY

- Display

- Dell Alienware AW3423DWF

- SSD

- Crucial T710 SSD 4TB, PCIe 5.0 M.2

- Gehäuse

- DeepCool Morpheus

- Netzteil

- ASUS ROG Strix 1000P Platinum, 1000W

- Keyboard

- ASUS ROG Strix Flare II // Logitech MX Key

- Mouse

- ASUS ROG Harpe Ace Aim Lab Edition

- Betriebssystem

- Win 11

- Webbrowser

- Brave

- Sonstiges

- Edifier S351DB // UE4000

- Internet

- ▼1000 ▲50

nice kannst du mal einen Aida test posten ?

heute will ich mal testen wie stabil die 2200Mhz sind, danach gehts ans CO... ach ja, Nitro muss ich ja auch noch gucken.

RedF

Enthusiast

- Mitglied seit

- 07.03.2020

- Beiträge

- 5.698

- Ort

- am Main

- Desktop System

- Rechner

- Laptop

- Laptop

- Details zu meinem Desktop

- Prozessor

- Ryzen 7800X3D

- Mainboard

- ASrock X670E Taichi

- Kühler

- Core 1 360+1080 Radiator

- Speicher

- 32GB 6200MHz

- Grafikprozessor

- 7900XTX

- Display

- Samsung C32HG70

- SSD

- 2x960GB Corsair MP510 1x512GB Samsung PM961 1x2TB FireCuda

- HDD

- Seagate 4TB

- Opt. Laufwerk

- -

- Soundkarte

- GC7

- Gehäuse

- be quiet! 601 Silentbase / aufgesägt

- Netzteil

- Seasonic Prime 1000

- Keyboard

- logitech G815

- Mouse

- Xtrfy MZ1

- Betriebssystem

- W11

- Webbrowser

- Firefox

- Sonstiges

- 3D-Drucker: Qidi Plus 4, Ender 3V2 (war er mal)

Nein ein Tipp.Ist das ne Frage? tRDWR 14 bei 6200 führt zu no boot. 15 bin ich mir jetzt gar nicht sicher, ob das ich schon mal probiert habe.

Tatilica

Experte

- Mitglied seit

- 10.06.2020

- Beiträge

- 194

- Ort

- Romania

- Desktop System

- Tatili

- Details zu meinem Desktop

- Prozessor

- Ryzen 9900x3D

- Mainboard

- X870 TOMAHAWK Wifi

- Kühler

- ID Cooling FX240 PRO Black

- Speicher

- Gskill Neo 8000Mhz CL38

- Grafikprozessor

- Asus ProArt OC RTX 4070Super

- Display

- Asus Rog Swift 1440p/165hz

- SSD

- Corsair MP700 PRO 1TB PCI-e 5.0 x4.0

- Gehäuse

- Montech Sky Two GX

- Netzteil

- Corsair 2024 RM1000x ATX 3.1

- Betriebssystem

- Windows 11

Great, it's working with older Bios version too for 99xDNew ZenTimings beta.

Zuletzt bearbeitet:

webmi

Legende

- Mitglied seit

- 27.02.2013

- Beiträge

- 20.036

Nein ein Tipp.

Zusammenhang ist mir nicht ganz klar, kannst das erklären? Warum tRDWR 15 bei WRPRE 3?

tRDWR = WRPRE + 12 ?

Aber warum?

webmi

Legende

- Mitglied seit

- 27.02.2013

- Beiträge

- 20.036

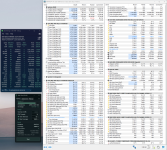

tRDWR 12 kein Boot

tRDWR 13 Error/Crash

tRDWR 14 läuft

Performance bringt das Absenken von vormals 16 auf 14 auf jeden Fall etwas, so konnte ich damit das erste Mal Reads > 70K mit Interleaving = CPU erreichen

Die JEDEC Formel ist ja eine andere als dein Tipp @RedF - Die würde mir aber eine tRDWR von mindestens 10 setzen, was ohnehin nicht läuft, ergo low as possible is fine und bringt was, wenn auch nur wieder mal sehr wenig

tRDWR 13 Error/Crash

tRDWR 14 läuft

Performance bringt das Absenken von vormals 16 auf 14 auf jeden Fall etwas, so konnte ich damit das erste Mal Reads > 70K mit Interleaving = CPU erreichen

Die JEDEC Formel ist ja eine andere als dein Tipp @RedF - Die würde mir aber eine tRDWR von mindestens 10 setzen, was ohnehin nicht läuft, ergo low as possible is fine und bringt was, wenn auch nur wieder mal sehr wenig

Führt die Verwendung von eCLK nicht zu Fehlern bei AIDA64-Messwerten? Ich glaube, das wurde bereits besprochen.Performance bringt das Absenken von vormals 16 auf 14 auf jeden Fall etwas, so konnte ich damit das erste Mal Reads > 70K mit Interleaving = CPU erreichen

Induktor

Enthusiast

- Mitglied seit

- 03.11.2019

- Beiträge

- 3.579

- Laptop

- Lenovo Yoga Pro 7i - Intel-7 255H - 32GB LPDDR5x-8533 - 14,5" OLED (3000*1876) 120Hz - Samsung 990 Pro 2TB

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen-7 9800X3D (CO: +0/ per Core UV)

- Mainboard

- MSI X870E Carbon Wifi (A93)

- Kühler

- Arctic LF III 280 & 2x Toughfan 14 Pro + Noctua NA-IS1-14

- Speicher

- 32GB - 6200 MT/s (CL26-12-36-30 - tRFC 120ns)

- Grafikprozessor

- Gigabyte RTX 5080 Gaming OC (Shroud-Mod 3x T30)

- Display

- Alienware AW2725DF (OLED 360Hz) & AW2725QF (IPS 4K)

- SSD

- Samsung 990 Pro & 990 Evo+

- Gehäuse

- Open Benchtable V2 (vertikal)

- Netzteil

- Corsair AX850 (Titanium)

- Sonstiges

- Thermal Grizzly AM5 Frame

@RedF Schließ mich der Frage mal an. 15 läuft soweit, hab aber noch nicht in TM5 getestet.Zusammenhang ist mir nicht ganz klar, kannst das erklären? Warum tRDWR 15 bei WRPRE 3?

Die 14 siehst du bei 6200+ auch nur bei den gebinnten G.Skill Kits.tRDWR 12 kein Boot

tRDWR 13 Error/Crash

tRDWR 14 läuft

magy77

Experte

- Mitglied seit

- 03.01.2021

- Beiträge

- 125

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen™ 9 9950X3D

- Mainboard

- MSI MEG X870E GODLIKE

- Kühler

- EK-Quantum Velocity³

- Speicher

- DDR5-6400 CL26-36-36-36 1.51V 2x32GB

- Grafikprozessor

- AORUS GeForce RTX™ 5090 XTREME WATERFORCE WB 32G

- Display

- Samsung Odyssey OLED G9

- SSD

- 4x2TB M.2 2280

- Gehäuse

- Fractal North XL Charcoal Black

- Netzteil

- be quiet! Dark Power Pro 12 1200 W

- Keyboard

- G815

- Mouse

- G502 Hero

- Betriebssystem

- Win 11 Professional

- Webbrowser

- Firefox

Wieviel Spannung vdd musstest du hierfür anlegen?tRDWR 12 kein Boot

tRDWR 13 Error/Crash

tRDWR 14 läuft

Performance bringt das Absenken von vormals 16 auf 14 auf jeden Fall etwas, so konnte ich damit das erste Mal Reads > 70K mit Interleaving = CPU erreichen

Anhang anzeigen 1145734

Die JEDEC Formel ist ja eine andere als dein Tipp @RedF - Die würde mir aber eine tRDWR von mindestens 10 setzen, was ohnehin nicht läuft, ergo low as possible is fine und bringt was, wenn auch nur wieder mal sehr wenig

Sind die beiden 1en bei trfc2 und trfcsb eigentlich auslesefehler oder wie kommt man da so tief?

Zuletzt bearbeitet:

HardyEbw

Experte

- Mitglied seit

- 17.01.2025

- Beiträge

- 1.249

- Desktop System

- Gaming-PC

- Laptop

- ASUS Zenbook S16 (AMD Ryzen AI 9 HX 370)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9850X3D, Optimus Signature V3

- Mainboard

- ASRock X870E Taichi OCF

- Kühler

- MORA 400 + Signature V3 CPU & CORE 1 GPU

- Speicher

- 32GB G.Skill F5-6000J2636H16GX2, ICE Block

- Grafikprozessor

- Gigabyte RTX 5090 Windforce OC, CORE 1 Block

- Display

- ASUS ROG Strix OLED XG32UCWMG 4K@240Hz

- SSD

- Kingston 1TB Gen5 & 2+2+4TB Gen4 NVME

- Gehäuse

- be quiet! LIGHT BASE 500

- Netzteil

- FSP MEGA TI 1650W 80 Plus Titanium

- Keyboard

- ASUS ROG Azoth

- Mouse

- ASUS ROG Harpe II Ace

- Betriebssystem

- MS Windows 11 Pro

- Webbrowser

- MS Edge

- Sonstiges

- Thermal Grizzly WireView Pro II

- Internet

- ▼250 MBit ▲40 MBit

RedF

Enthusiast

- Mitglied seit

- 07.03.2020

- Beiträge

- 5.698

- Ort

- am Main

- Desktop System

- Rechner

- Laptop

- Laptop

- Details zu meinem Desktop

- Prozessor

- Ryzen 7800X3D

- Mainboard

- ASrock X670E Taichi

- Kühler

- Core 1 360+1080 Radiator

- Speicher

- 32GB 6200MHz

- Grafikprozessor

- 7900XTX

- Display

- Samsung C32HG70

- SSD

- 2x960GB Corsair MP510 1x512GB Samsung PM961 1x2TB FireCuda

- HDD

- Seagate 4TB

- Opt. Laufwerk

- -

- Soundkarte

- GC7

- Gehäuse

- be quiet! 601 Silentbase / aufgesägt

- Netzteil

- Seasonic Prime 1000

- Keyboard

- logitech G815

- Mouse

- Xtrfy MZ1

- Betriebssystem

- W11

- Webbrowser

- Firefox

- Sonstiges

- 3D-Drucker: Qidi Plus 4, Ender 3V2 (war er mal)

tRDWR = tCL - tCWL + BC8 + ODTEnDly (1) + WRPRE + SafetyDly (1)@RedF Ich würde das auch gern wissen.😉

Bei mir ist tWRPRE = 2, insofern teste ich gleich einmal tRDWR = 14.

bzw. tCL- (tCL-2) +8 +1 + WRPRE +1

Beitrag automatisch zusammengeführt:

Wen man zu niedrig damit ist, merkt man es oft schon, dass sich das System "hakelig" anfühlt.

Beitrag automatisch zusammengeführt:

Das habe ich momentan als "Richtlinie"

| tRP | tCL+4 | |||

| tRAS | tRP+tRTP | |||

| tRC | tRAS+tRP | |||

| tFAW | tRRDS*4 | |||

| tWTRL | tWTRS*4 | |||

| tRFC (ns) | tRFC/(MT/s/2)*1000 | |||

| tRFC2 | tRFC*1,84375 | |||

| tRFCsb | tRFC*2,26923 | |||

| tCWL | tCL-2 | |||

| tRTP | 12 | |||

| tRDWR | tCL - tCWL + BC(8) + ODTEnDly (1) + WRPRE + SafetyDly (1) |

Beitrag automatisch zusammengeführt:

Zu bevorzugen sollen ganze zahlen als tRFC in ns sein.

Hat das schonmal jemand gegen getestet?

Also bei 6200MT/s

| tRFC | ns |

279 | 90 |

310 | 100 |

341 | 110 |

372 | 120 |

403 | 130 |

434 | 140 |

465 | 150 |

496 | 160 |

527 | 170 |

558 | 180 |

589 | 190 |

620 | 200 |

651 | 210 |

682 | 220 |

Ob das dem MC besser schmeckt? Er sonst rundet? Keine ahnung...

Zuletzt bearbeitet:

HardyEbw

Experte

- Mitglied seit

- 17.01.2025

- Beiträge

- 1.249

- Desktop System

- Gaming-PC

- Laptop

- ASUS Zenbook S16 (AMD Ryzen AI 9 HX 370)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9850X3D, Optimus Signature V3

- Mainboard

- ASRock X870E Taichi OCF

- Kühler

- MORA 400 + Signature V3 CPU & CORE 1 GPU

- Speicher

- 32GB G.Skill F5-6000J2636H16GX2, ICE Block

- Grafikprozessor

- Gigabyte RTX 5090 Windforce OC, CORE 1 Block

- Display

- ASUS ROG Strix OLED XG32UCWMG 4K@240Hz

- SSD

- Kingston 1TB Gen5 & 2+2+4TB Gen4 NVME

- Gehäuse

- be quiet! LIGHT BASE 500

- Netzteil

- FSP MEGA TI 1650W 80 Plus Titanium

- Keyboard

- ASUS ROG Azoth

- Mouse

- ASUS ROG Harpe II Ace

- Betriebssystem

- MS Windows 11 Pro

- Webbrowser

- MS Edge

- Sonstiges

- Thermal Grizzly WireView Pro II

- Internet

- ▼250 MBit ▲40 MBit

Ich würde sagen, 496 = 160ns läuft schlechter als meine 488. Muss ich einmal testen.

465 = 150ns sind 99%ig nicht möglich.

tRP = tCL+4 geht bei mir auch nicht, meine ich. Teste ich noch einmal.

465 = 150ns sind 99%ig nicht möglich.

tRP = tCL+4 geht bei mir auch nicht, meine ich. Teste ich noch einmal.

Ich habe 3 und 14 und es ist großartigBei mir ist tWRPRE = 2, insofern teste ich gleich einmal tRDWR = 14.

RedF

Enthusiast

- Mitglied seit

- 07.03.2020

- Beiträge

- 5.698

- Ort

- am Main

- Desktop System

- Rechner

- Laptop

- Laptop

- Details zu meinem Desktop

- Prozessor

- Ryzen 7800X3D

- Mainboard

- ASrock X670E Taichi

- Kühler

- Core 1 360+1080 Radiator

- Speicher

- 32GB 6200MHz

- Grafikprozessor

- 7900XTX

- Display

- Samsung C32HG70

- SSD

- 2x960GB Corsair MP510 1x512GB Samsung PM961 1x2TB FireCuda

- HDD

- Seagate 4TB

- Opt. Laufwerk

- -

- Soundkarte

- GC7

- Gehäuse

- be quiet! 601 Silentbase / aufgesägt

- Netzteil

- Seasonic Prime 1000

- Keyboard

- logitech G815

- Mouse

- Xtrfy MZ1

- Betriebssystem

- W11

- Webbrowser

- Firefox

- Sonstiges

- 3D-Drucker: Qidi Plus 4, Ender 3V2 (war er mal)

Wenn es das runden ist,Ich würde sagen, 496 = 160ns läuft schlechter als meine 488. Muss ich einmal testen.

465 = 150ns sind 99%ig nicht möglich.

tRP = tCL+4 geht bei mir auch nicht, meine ich. Teste ich noch einmal.

486 | 156,77 |

487 | 157,10 |

488 | 157,42 |

489 | 157,74 |

490 | 158,06 |

491 | 158,39 |

492 | 158,71 |

493 | 159,03 |

494 | 159,35 |

Beitrag automatisch zusammengeführt:

Vielleicht ist das Safety Delay +1 nicht immer nötig?

Beitrag automatisch zusammengeführt:

WRPRE wird bei meinem Board falsch von ZT ausgelesen.

Beitrag automatisch zusammengeführt:

Scheint an meinem Board zu liegen(war noch zur 1.36.1650) :

Oder doch nicht das Board:

Zuletzt bearbeitet:

- Mitglied seit

- 19.08.2003

- Beiträge

- 3.449

- Desktop System

- Lieselotte

- Details zu meinem Desktop

- Prozessor

- 16-Core AMD Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike (MS-7E48) BIOS 1: A30/ 2:A51

- Kühler

- CPU Cooler Alphacool Core 1 ; Supernova 1260mm ; EKWB Coolstream Xe 360; NexXxoS ST20 HPE; VPP Apex

- Speicher

- G Skill F5-8000J4048G24G

- Grafikprozessor

- INNO3D GeForce RTX 5090 X3 OC

- Display

- LG UltraGear 34GP950G-B

- SSD

- WD BLACK SN8100 2TB; WD_BLACK SN850X 2TB ; CT2000BX500SSD1

- HDD

- WD Black SATA 8TB

- Gehäuse

- PHANTEKS Enthoo 719

- Netzteil

- FSP Hydro PTM Pro 1350W

- Keyboard

- RAZER BLACKWIDOW V4 LOW-PROFILE HYPERSPEED

- Mouse

- Logitech G604; G502X ; Razer Naga V2

- Betriebssystem

- WIN 11 25H2

- Sonstiges

- RAZER Blackshark V2 Pro Headset

- Internet

- ▼250 Mbit/s ▲40 Mbit/s

..mal ne Frage, hat jemand auch mit Zentimings Probleme? Und zwar sucht Zentimings in letzter Zeit oft nach der Agesa Version , obwohl es schon mehrfach unter dem laufenden Bios, mit admin rechten, gestartet wurde. Manchmal kann es auch die Powertable nicht finden.....

Das folgende Setting hier habe ich zuletzt bzgl TRC; RCDWR und TWTRL und TWR angezogen. Das läuft zumindest mal 45minuten TM5 DDR5 Ryzen 3D @anta durch. Daran kanns ja wohl nicht liegen.

Ich habe das letzte Windows 11 Update da im Verdacht ((KB5065789) (26100.6725)) - wurde am 2.10.25 installiert. Leider habe ich just um die Zeit auch die Timings geändert.

Kennt jemand dieses Zentimings Verhalten? Auch mit der 48er debug Version tut es dies....

Edit: TM5 nach 45 minuten selbstabbruch -keine Fehler.

Das folgende Setting hier habe ich zuletzt bzgl TRC; RCDWR und TWTRL und TWR angezogen. Das läuft zumindest mal 45minuten TM5 DDR5 Ryzen 3D @anta durch. Daran kanns ja wohl nicht liegen.

Ich habe das letzte Windows 11 Update da im Verdacht ((KB5065789) (26100.6725)) - wurde am 2.10.25 installiert. Leider habe ich just um die Zeit auch die Timings geändert.

Kennt jemand dieses Zentimings Verhalten? Auch mit der 48er debug Version tut es dies....

Edit: TM5 nach 45 minuten selbstabbruch -keine Fehler.

magy77

Experte

- Mitglied seit

- 03.01.2021

- Beiträge

- 125

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen™ 9 9950X3D

- Mainboard

- MSI MEG X870E GODLIKE

- Kühler

- EK-Quantum Velocity³

- Speicher

- DDR5-6400 CL26-36-36-36 1.51V 2x32GB

- Grafikprozessor

- AORUS GeForce RTX™ 5090 XTREME WATERFORCE WB 32G

- Display

- Samsung Odyssey OLED G9

- SSD

- 4x2TB M.2 2280

- Gehäuse

- Fractal North XL Charcoal Black

- Netzteil

- be quiet! Dark Power Pro 12 1200 W

- Keyboard

- G815

- Mouse

- G502 Hero

- Betriebssystem

- Win 11 Professional

- Webbrowser

- Firefox

Gibt es einen Grund für die das A30 Bios vom März?..mal ne Frage, hat jemand auch mit Zentimings Probleme? Und zwar sucht Zentimings in letzter Zeit oft nach der Agesa Version , obwohl es schon mehrfach unter dem laufenden Bios, mit admin rechten, gestartet wurde. Manchmal kann es auch die Powertable nicht finden.....

Das folgende Setting hier habe ich zuletzt bzgl TRC; RCDWR und TWTRL und TWR angezogen. Das läuft zumindest mal 45minuten TM5 DDR5 Ryzen 3D @anta durch. Daran kanns ja wohl nicht liegen.

Ich habe das letzte Windows 11 Update da im Verdacht ((KB5065789) (26100.6725)) - wurde am 2.10.25 installiert. Leider habe ich just um die Zeit auch die Timings geändert.

Kennt jemand dieses Zentimings Verhalten? Auch mit der 48er debug Version tut es dies....

Anhang anzeigen 1145856

Edit: TM5 nach 45 minuten selbstabbruch -keine Fehler.

- Mitglied seit

- 19.08.2003

- Beiträge

- 3.449

- Desktop System

- Lieselotte

- Details zu meinem Desktop

- Prozessor

- 16-Core AMD Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike (MS-7E48) BIOS 1: A30/ 2:A51

- Kühler

- CPU Cooler Alphacool Core 1 ; Supernova 1260mm ; EKWB Coolstream Xe 360; NexXxoS ST20 HPE; VPP Apex

- Speicher

- G Skill F5-8000J4048G24G

- Grafikprozessor

- INNO3D GeForce RTX 5090 X3 OC

- Display

- LG UltraGear 34GP950G-B

- SSD

- WD BLACK SN8100 2TB; WD_BLACK SN850X 2TB ; CT2000BX500SSD1

- HDD

- WD Black SATA 8TB

- Gehäuse

- PHANTEKS Enthoo 719

- Netzteil

- FSP Hydro PTM Pro 1350W

- Keyboard

- RAZER BLACKWIDOW V4 LOW-PROFILE HYPERSPEED

- Mouse

- Logitech G604; G502X ; Razer Naga V2

- Betriebssystem

- WIN 11 25H2

- Sonstiges

- RAZER Blackshark V2 Pro Headset

- Internet

- ▼250 Mbit/s ▲40 Mbit/s

bekomme ich im Schnitt unter AIDA64 immer noch die besten Latenzen 62,x ns habe ich noch nie mit meiner config bei einem anderen Bios gesehen und ich habe sehr oft die Messung wiederholt. Allerding auch nie extra im abgesicherten Modus gestartet. Zudem soll Bios A51 oder besser die Agesa "G" ja buggy bzgl FSB sein, auch wenn es mich mit meinem 101,5 Mhz nicht wirklich tangiert, diese laufen auch mit Bios A51..Gibt es einen Grund für die das A30 Bios vom März?

webmi

Legende

- Mitglied seit

- 27.02.2013

- Beiträge

- 20.036

Wieviel Spannung vdd musstest du hierfür anlegen?

Sind die beiden 1en bei trfc2 und trfcsb eigentlich auslesefehler oder wie kommt man da so tief?

VDD = 1.75v (nach wie vor)

Die Werte auf 1 werden nicht genutzt mit Zen5 auf DDR5 mit SR

Ähnliche Themen

- Antworten

- 24

- Aufrufe

- 2K

- Antworten

- 80

- Aufrufe

- 10K

- Antworten

- 29

- Aufrufe

- 3K