News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

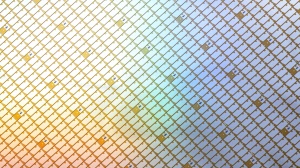

Wafer

-

Quartalszahlen: TSMC liefert mehr Wafer denn je

TSMC hat seine Vormachtstellung bei den Halbleiterherstellern unterstrichen und vermeldet für das erste Quartal 2026 weiterhin extrem hohe Umsätze und Gewinne. Mit 4,17 Millionen Wafern (300 mm Äquivalent) wurde mehr Chipfläche denn je belichtet. In den vergangenen drei Monaten erreichte TSMC einen Umsatz in Höhe von 35,9 Milliarden US-Dollar. Der Nettogewinn lag bei 18,1 Milliarden US-Dollar. TSMC verdient kräftig, es wird aber... [mehr]

TSMC hat seine Vormachtstellung bei den Halbleiterherstellern unterstrichen und vermeldet für das erste Quartal 2026 weiterhin extrem hohe Umsätze und Gewinne. Mit 4,17 Millionen Wafern (300 mm Äquivalent) wurde mehr Chipfläche denn je belichtet. In den vergangenen drei Monaten erreichte TSMC einen Umsatz in Höhe von 35,9 Milliarden US-Dollar. Der Nettogewinn lag bei 18,1 Milliarden US-Dollar. TSMC verdient kräftig, es wird aber... [mehr] -

Hot Chips 2025: Rapidus will sich durch schnelle Durchlaufzeiten auszeichnen

Der im August gegründete und inzwischen unter anderem vom IBM unterstützte japanische Auftragsfertiger will ab 2027 die ersten Chips in der eigens entwickelten 2-nm-Fertigung ausliefern. Das stark durch den japanischen Staat geförderte Unternehmen hat im September 2023 mit dem Bau der IIM-2 getauften Fab begonnen, im Dezember 2024 wurden die ersten Belichtungsmaschinen im noch leeren Reinraum installiert. Ab dem Frühjahr konnten die ersten... [mehr]

Der im August gegründete und inzwischen unter anderem vom IBM unterstützte japanische Auftragsfertiger will ab 2027 die ersten Chips in der eigens entwickelten 2-nm-Fertigung ausliefern. Das stark durch den japanischen Staat geförderte Unternehmen hat im September 2023 mit dem Bau der IIM-2 getauften Fab begonnen, im Dezember 2024 wurden die ersten Belichtungsmaschinen im noch leeren Reinraum installiert. Ab dem Frühjahr konnten die ersten... [mehr] -

Wafer- und Chipfertigung: China stellt 1 Million Wafer her und YMTC belichtet knapp die Hälfte

Aktuelle Zahlen aus China sowie des japanischen Waferherstellers SUMCO ergeben ein neues Bild über den Umfang der Eigenständigkeit Chinas in der Chipfertigung. Inzwischen sollen chinesische Unternehmen in der Lage sein, rund eine Million Wafer selbst zu fertigen. Damit macht man sich weiter von westlichen Herstellern wie SUMCO unabhängig, was natürlich schlecht für deren Geschäft ist. Zu den weiteren Herstellern von Wafern... [mehr]

Aktuelle Zahlen aus China sowie des japanischen Waferherstellers SUMCO ergeben ein neues Bild über den Umfang der Eigenständigkeit Chinas in der Chipfertigung. Inzwischen sollen chinesische Unternehmen in der Lage sein, rund eine Million Wafer selbst zu fertigen. Damit macht man sich weiter von westlichen Herstellern wie SUMCO unabhängig, was natürlich schlecht für deren Geschäft ist. Zu den weiteren Herstellern von Wafern... [mehr] -

300 mm Durchmesser und 20 µm dick: Infineon stellt extrem dünne Wafer her

Infineon hat die Herstellung und erste Nutzung von ultradünnen Wafern angekündigt, die auf eine Dicke von gerade einmal 20 µm kommen. Die Wafer haben den in der Halbleiterfertigung inzwischen üblichen Durchmesser von 300 mm. Mit einer Dicke von nur 20 µm stellen sie in der Fertigung und Handhabung in der Belichtung sowie der weiteren Verarbeitung eine besondere Herausforderung dar. Gemeinsam mit ersten Kunden will man diese jedoch gelöst haben... [mehr]

Infineon hat die Herstellung und erste Nutzung von ultradünnen Wafern angekündigt, die auf eine Dicke von gerade einmal 20 µm kommen. Die Wafer haben den in der Halbleiterfertigung inzwischen üblichen Durchmesser von 300 mm. Mit einer Dicke von nur 20 µm stellen sie in der Fertigung und Handhabung in der Belichtung sowie der weiteren Verarbeitung eine besondere Herausforderung dar. Gemeinsam mit ersten Kunden will man diese jedoch gelöst haben... [mehr] -

Galliumnitrid auf 300 mm: Infineon fertigt Leistungshalbleiter effizienter

Auch wenn sich in unserem Themenfeld vieles oder nahezu alles auf die Siliziumchips konzentriert, so kommen die meisten Menschen in ihrem alltäglichen Umfeld ohne Leistungshalbleiter nicht mehr weit – sei es im E-Auto, diversen Netzteilen, Solarwechselrichter und vielem mehr. Die Leistungshalbleiter werden in Siliziumkarbid (SiC) oder Galliumnitrid (GaN) gefertigt und entsprechend konzentrieren sich Firmen, die solche Bauteile... [mehr]

Auch wenn sich in unserem Themenfeld vieles oder nahezu alles auf die Siliziumchips konzentriert, so kommen die meisten Menschen in ihrem alltäglichen Umfeld ohne Leistungshalbleiter nicht mehr weit – sei es im E-Auto, diversen Netzteilen, Solarwechselrichter und vielem mehr. Die Leistungshalbleiter werden in Siliziumkarbid (SiC) oder Galliumnitrid (GaN) gefertigt und entsprechend konzentrieren sich Firmen, die solche Bauteile... [mehr] -

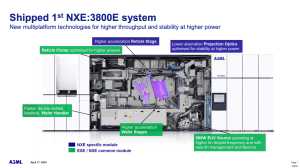

ASML: EUV nimmt gerade erst Fahrt auf und zweites High-NA-System geht an Kunden

ASML hat die Zahlen für das erste Quartal 2024 verkündet und liegt in etwa der Mitte der eigenen Prognose. Der Umsatz geht von 6,75 Milliarden Euro auf 5,3 Milliarden Euro zurück, der Gewinn schrumpft von 1,96 auf 1,22 Milliarden Euro. Für das kommende Quartal erwartete ASML ein kleines Plus, was sich so auch für das Gesamtjahr 2024 fortsetzen soll. Ab 2025 und danach soll es dann in eine stärkere Wachstumsphase übergehen, denn die... [mehr]

ASML hat die Zahlen für das erste Quartal 2024 verkündet und liegt in etwa der Mitte der eigenen Prognose. Der Umsatz geht von 6,75 Milliarden Euro auf 5,3 Milliarden Euro zurück, der Gewinn schrumpft von 1,96 auf 1,22 Milliarden Euro. Für das kommende Quartal erwartete ASML ein kleines Plus, was sich so auch für das Gesamtjahr 2024 fortsetzen soll. Ab 2025 und danach soll es dann in eine stärkere Wachstumsphase übergehen, denn die... [mehr] -

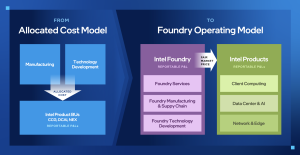

Interne Selbsteinschätzung: Wie Intel sich in der Prozesstechnologie aufgestellt sieht

Mitte Februar gab Intel seine Foundry-Pläne und die Ausgliederung dieses Geschäftsbereichs bekannt. Darüber hinaus will man die bestehende Roadmap für zukünftige Fertigungsgrößen um ein paar Erweiterungen ergänzen, um als Foundry für seine Kunden besser aufgestellt zu sein. Bis hin zu Intel 10A, eine Fertigung die ab 2028 in Betracht gezogen wird, hat Intel seine Pläne vorgelegt. Gestern nun hat Intel offengelegt, wie die Gliederung... [mehr]

Mitte Februar gab Intel seine Foundry-Pläne und die Ausgliederung dieses Geschäftsbereichs bekannt. Darüber hinaus will man die bestehende Roadmap für zukünftige Fertigungsgrößen um ein paar Erweiterungen ergänzen, um als Foundry für seine Kunden besser aufgestellt zu sein. Bis hin zu Intel 10A, eine Fertigung die ab 2028 in Betracht gezogen wird, hat Intel seine Pläne vorgelegt. Gestern nun hat Intel offengelegt, wie die Gliederung... [mehr] -

W2W 3D IC: UMC will ein Stück des Packaging-Kuchens

Der taiwanesische Halbleiterhersteller United Microelectronics Corporation (UMC) kündigt für das kommende Jahr ein neues Packaging-Verfahren an, mit dem man ein Stück des aktuellen Bedarfs nach Packaging-Kapazitäten abhaben möchte. Bei W2W 3D IC handelt es sich um ein Wafer-auf-Wafer-Verfahren, bei dem mehrere Chips übereinander gestapelt werden können. Partner sind Winbond, Faraday, ASE und Cadence. Zielmarkt für UMC dürften... [mehr]

Der taiwanesische Halbleiterhersteller United Microelectronics Corporation (UMC) kündigt für das kommende Jahr ein neues Packaging-Verfahren an, mit dem man ein Stück des aktuellen Bedarfs nach Packaging-Kapazitäten abhaben möchte. Bei W2W 3D IC handelt es sich um ein Wafer-auf-Wafer-Verfahren, bei dem mehrere Chips übereinander gestapelt werden können. Partner sind Winbond, Faraday, ASE und Cadence. Zielmarkt für UMC dürften... [mehr] -

Vom Wafer bis zum Package: Ein Besuch bei Intel Malaysia

Im Rahmen der Intel Tech Tour 2023 hatten wir Gelegenheit, die wichtigsten Einrichtungen des Chipgiganten in Malaysia zu besuchen. Viele werden sich sicherlich nicht des vollen Umfangs bewusst sein, wie umfangreich die Anstrengungen eines Prozessor-Herstellers sind, um aus einem Silizium-Wafer das finale Endprodukt zu entwickeln. Die Dimensionen dieser Anstrengungen einmal vor Ort zu erleben, ist aber noch einmal eine andere Geschichte. Ein... [mehr]

Im Rahmen der Intel Tech Tour 2023 hatten wir Gelegenheit, die wichtigsten Einrichtungen des Chipgiganten in Malaysia zu besuchen. Viele werden sich sicherlich nicht des vollen Umfangs bewusst sein, wie umfangreich die Anstrengungen eines Prozessor-Herstellers sind, um aus einem Silizium-Wafer das finale Endprodukt zu entwickeln. Die Dimensionen dieser Anstrengungen einmal vor Ort zu erleben, ist aber noch einmal eine andere Geschichte. Ein... [mehr] -

Lam Research: Wafer-Schutzschicht für bessere Ausbeute

Als führender Anbieter von verfahrenstechnischen Anlagen in der Halbleiterindustrie hat Lam Research ein neues Verfahren vorgestellt, welches für eine höhere Ausbeute im Prozess der Wafer-Verarbeitung sorgen soll. Da es in der Fertigung moderner Chips zu einem immer größeren Anteil an Verarbeitungsschritten und teilweise Wafer-on-Wafer-Technologien kommt, wird ein Schutz der Wafer zunehmend wichtig. Die Kante eines Wafers ist eine... [mehr]

Als führender Anbieter von verfahrenstechnischen Anlagen in der Halbleiterindustrie hat Lam Research ein neues Verfahren vorgestellt, welches für eine höhere Ausbeute im Prozess der Wafer-Verarbeitung sorgen soll. Da es in der Fertigung moderner Chips zu einem immer größeren Anteil an Verarbeitungsschritten und teilweise Wafer-on-Wafer-Technologien kommt, wird ein Schutz der Wafer zunehmend wichtig. Die Kante eines Wafers ist eine... [mehr] -

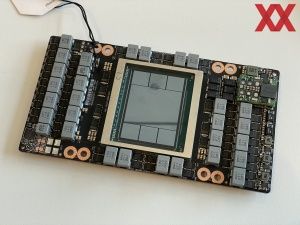

Advanced Backend Fab 6: TSMC kann mehr als 1 Million Wafer pro Jahr verarbeiten

Gestern hat TSMC die offizielle Eröffnung seiner Advanced Backend Fab 6 verkündet. Damit trifft TSMC ziemlich gut den aktuellen Bedarf nach Packaging-Kapazitäten, den vor allem NVIDIA aktuell vorantreibt. Mit den drei Ausbaustufen AP6A, AP6B und AP6C entsteht mehr als die doppelte Kapazität dessen, was aktuell in der Advanced Backend Fab 1 möglich war. Auf 143.000 m² beläuft sich die Fläche der AP6-Anlage im Zhunan Science Park,... [mehr]

Gestern hat TSMC die offizielle Eröffnung seiner Advanced Backend Fab 6 verkündet. Damit trifft TSMC ziemlich gut den aktuellen Bedarf nach Packaging-Kapazitäten, den vor allem NVIDIA aktuell vorantreibt. Mit den drei Ausbaustufen AP6A, AP6B und AP6C entsteht mehr als die doppelte Kapazität dessen, was aktuell in der Advanced Backend Fab 1 möglich war. Auf 143.000 m² beläuft sich die Fläche der AP6-Anlage im Zhunan Science Park,... [mehr] -

Japan und Südkorea: Samsung plant neues Chip-Entwicklungszentrum

Samsung plant ein neue Entwicklungseinrichtung in Japan zu errichten. Mit der Initiative soll die Zusammenarbeit zwischen der japanischen und südkoreanischen Chipindustrie weiter gefördert. Geplant ist der Bau eines separates Entwicklungszentrums in Yokohama, südwestlich von Tokio, wo sich bereits Anlangen des südkoreanischen Herstellers befinden. Die neue Einrichtung soll über 30 Milliarden Yen, umgerechnet etwa 222 Millionen US-Dollar,... [mehr]

Samsung plant ein neue Entwicklungseinrichtung in Japan zu errichten. Mit der Initiative soll die Zusammenarbeit zwischen der japanischen und südkoreanischen Chipindustrie weiter gefördert. Geplant ist der Bau eines separates Entwicklungszentrums in Yokohama, südwestlich von Tokio, wo sich bereits Anlangen des südkoreanischen Herstellers befinden. Die neue Einrichtung soll über 30 Milliarden Yen, umgerechnet etwa 222 Millionen US-Dollar,... [mehr] -

Wafer-Preise: Nach dreijährigem Anstieg deutet sich Entspannung an

Für die Halbleiterindustrie waren die vergangenen Jahren ein Auf und Ab. Nachdem sie während der Corona-Pandemie noch einen regelrechten Boom erlebte, befeuert durch hoch Nachfrage nach PC-Equipment und Kryptomining, brach der Absatz in Folge des Ukraine-Krieges regelrecht ein. Die Entwicklung wirkt sich auch auf die Basis der Halbleiterindustrie, die Herstellung der Silizium-Wafer, aus. Die Silizium-Wafer sind ein wesentlicher Rohstoff bei... [mehr]

Für die Halbleiterindustrie waren die vergangenen Jahren ein Auf und Ab. Nachdem sie während der Corona-Pandemie noch einen regelrechten Boom erlebte, befeuert durch hoch Nachfrage nach PC-Equipment und Kryptomining, brach der Absatz in Folge des Ukraine-Krieges regelrecht ein. Die Entwicklung wirkt sich auch auf die Basis der Halbleiterindustrie, die Herstellung der Silizium-Wafer, aus. Die Silizium-Wafer sind ein wesentlicher Rohstoff bei... [mehr] -

Semi-News: Intels Foundry-Chef geht und Wafer sowie Fabs werden teuer

Erst war es ein Gerücht, nun wurde es durch die Presseabteilung sowie den Chef von Intel bestätigt. Der aktuelle Chef der Foundry-Sparte Randhir Thakur wird das Unternehmen Anfang 2023 verlassen. Er war seit 2017 für Intel tätig. Einen direkten Nachfolger gibt es noch nicht, allerdings will Intel im kommenden Jahr die Übernahme des israelischen Unternehmens Tower Semiconductor abschließen. Aus dessen Führungsetage kommt womöglich... [mehr]

Erst war es ein Gerücht, nun wurde es durch die Presseabteilung sowie den Chef von Intel bestätigt. Der aktuelle Chef der Foundry-Sparte Randhir Thakur wird das Unternehmen Anfang 2023 verlassen. Er war seit 2017 für Intel tätig. Einen direkten Nachfolger gibt es noch nicht, allerdings will Intel im kommenden Jahr die Übernahme des israelischen Unternehmens Tower Semiconductor abschließen. Aus dessen Führungsetage kommt womöglich... [mehr] -

Intel zeigt Wafer mit Raptor-Lake-Chips

Die Fab28, die Fertigungsstätte für Intels Alder-Lake und Raptor-Lake-Prozessoren, war eine Station der Intel Tech Tour, auf der auch wir Teilnehmer waren. Dort haben wir auch einen kompletten Wafer zu Gesicht bekommen, der mit Raptor-Lake-Chips belichtet war. Aktuell befindet sich Intel in der Massenproduktion der Raptor-Lake-Chips. Auf dem Wafer, den wir zu Gesicht bekommen haben, war die 8+16-Konfiguration zu erkennen – acht... [mehr]

Die Fab28, die Fertigungsstätte für Intels Alder-Lake und Raptor-Lake-Prozessoren, war eine Station der Intel Tech Tour, auf der auch wir Teilnehmer waren. Dort haben wir auch einen kompletten Wafer zu Gesicht bekommen, der mit Raptor-Lake-Chips belichtet war. Aktuell befindet sich Intel in der Massenproduktion der Raptor-Lake-Chips. Auf dem Wafer, den wir zu Gesicht bekommen haben, war die 8+16-Konfiguration zu erkennen – acht... [mehr] -

GlobalWafers baut Werk für 1,2 Millionen Wafer pro Monat in Texas

Intel, Samsung, TSMC – alle großen Halbleiterhersteller bauen ihre Kapazitäten derzeit massiv aus. TSMC erweitert seine bestehenden Fabriken an den verschiedenen Standorten in Taiwan, Samsung in Südkorea und Intel hat eine Erweiterung in Irland sowie im US-Bundesstaat Oregon angekündigt. Daneben sollen in Deutschland (Magdeburg) und im Bundesstaat Ohio zwei Mega-Fabs entstehen. Doch alleine mit den Produktionsstätten in denen die Wafer... [mehr]

Intel, Samsung, TSMC – alle großen Halbleiterhersteller bauen ihre Kapazitäten derzeit massiv aus. TSMC erweitert seine bestehenden Fabriken an den verschiedenen Standorten in Taiwan, Samsung in Südkorea und Intel hat eine Erweiterung in Irland sowie im US-Bundesstaat Oregon angekündigt. Daneben sollen in Deutschland (Magdeburg) und im Bundesstaat Ohio zwei Mega-Fabs entstehen. Doch alleine mit den Produktionsstätten in denen die Wafer... [mehr] -

AMD und GlobalFoundries schließen neues Wafer-Abkommen

AMD und GlobalFoundries haben ihr Abkommen über die Lieferung belichteter Wafer erneuert und deutlich ausgeweitet. Bisher sicherte sich AMD durch ein Wafer Supply Agreement (WSA) bis 2024 ein Auftragsvolumen von 1,6 Milliarden US-Dollar. Das neue Abkommen läuft nun bis 2025 und über ein Volumen von 2,1 Milliarden US-Dollar. Im sogenannten "8-K Filing" ist die Rede von Wafern, die in 12 und 14 nm belichtet werden. Eine kleinere... [mehr]

AMD und GlobalFoundries haben ihr Abkommen über die Lieferung belichteter Wafer erneuert und deutlich ausgeweitet. Bisher sicherte sich AMD durch ein Wafer Supply Agreement (WSA) bis 2024 ein Auftragsvolumen von 1,6 Milliarden US-Dollar. Das neue Abkommen läuft nun bis 2025 und über ein Volumen von 2,1 Milliarden US-Dollar. Im sogenannten "8-K Filing" ist die Rede von Wafern, die in 12 und 14 nm belichtet werden. Eine kleinere... [mehr] -

AMDs Bindung an GlobalFoundries endet 2024

Ein Wafer Supply Agreement (WSA) zwischen AMD und GlobalFoundries sieht vor, dass AMD von 2019 bis 2021 belichtete und unbelichtete Wafer in einem gewissen Umfang abnimmt und zudem alle Chips in 12 nm und größer bei vormals AMD zugehörigen Auftragsfertiger verbleiben müssen. Im Rahmen eines sogenannten Exchange Commission Form 8-K Filing haben AMD und GlobalFoundries das WSA nun erneuert bzw. abgeändert. Demnach wird AMD... [mehr]

Ein Wafer Supply Agreement (WSA) zwischen AMD und GlobalFoundries sieht vor, dass AMD von 2019 bis 2021 belichtete und unbelichtete Wafer in einem gewissen Umfang abnimmt und zudem alle Chips in 12 nm und größer bei vormals AMD zugehörigen Auftragsfertiger verbleiben müssen. Im Rahmen eines sogenannten Exchange Commission Form 8-K Filing haben AMD und GlobalFoundries das WSA nun erneuert bzw. abgeändert. Demnach wird AMD... [mehr] -

Auf die Wafer Scale Engine folgt die Wafer Level SSD

Im vergangenen Jahr sorgte die Wafer Scale Engine (WSE) für einiges an Aufsehen. Die AI-Hardware besteht aus einem riesigen Chip, der natürlich in Bereiche aufgeteilt ist, aber dennoch auf eine Fläche von 46.225 mm² (215 x 215 mm) kommt – also aus einem 300-mm-Wafer besteht. Auf dem VLSI Symposium 2020 sprach higeo Oshima, Chief Engineer bei Kioxia über eine neuartige Entwicklung im Bereich der SSDs. Der entsprechende Bericht wurde auf... [mehr]

Im vergangenen Jahr sorgte die Wafer Scale Engine (WSE) für einiges an Aufsehen. Die AI-Hardware besteht aus einem riesigen Chip, der natürlich in Bereiche aufgeteilt ist, aber dennoch auf eine Fläche von 46.225 mm² (215 x 215 mm) kommt – also aus einem 300-mm-Wafer besteht. Auf dem VLSI Symposium 2020 sprach higeo Oshima, Chief Engineer bei Kioxia über eine neuartige Entwicklung im Bereich der SSDs. Der entsprechende Bericht wurde auf... [mehr] -

AMD wird 2020 bei TSMC Großabnehmer für 7-nm-Wafer

Noch im vergangenen Jahr berichteten wir über Apple als Großabnehmer für TSMCs Fertigungskapazitäten in 5 nm für den für 2020 erwarteten A14-SoC. Aktuell ist der iPhone- und iPad-Hersteller der größte Abnehmer für in 7 nm gefertigte Chips bei TSMC. Da Apple aber auf 5 nm wechseln wird, werden Kapazitäten für die Fertigung in 7 nm frei. Diese soll sich zu einem großen Anteil nun AMD gesichert haben. Insgesamt soll das Fertigungsvolumen für... [mehr]

Noch im vergangenen Jahr berichteten wir über Apple als Großabnehmer für TSMCs Fertigungskapazitäten in 5 nm für den für 2020 erwarteten A14-SoC. Aktuell ist der iPhone- und iPad-Hersteller der größte Abnehmer für in 7 nm gefertigte Chips bei TSMC. Da Apple aber auf 5 nm wechseln wird, werden Kapazitäten für die Fertigung in 7 nm frei. Diese soll sich zu einem großen Anteil nun AMD gesichert haben. Insgesamt soll das Fertigungsvolumen für... [mehr] -

Cerebras WSE: Die Hürden eines Chips in Wafer-Größe

Im Rahmen der Hotchips stellte ein Unternehmen namens Cerebras eine sogenannte Wafer Scale Engine (WSE) vor. Dabei handelt es sich um einen Chip, der aus mehreren Komponenten auf dem Wafer zusammengesetzt wird, aber als Gesamtkonstrukt auf dem Wafer gefertigt wird. Es handelt sich also nicht um ein Chiplet-Design im eigentlichen Sinne. WikiChip hat eine aktualisierte Analyse der WSE vorgenommen. Zur Supercomputing 19 soll es... [mehr]

Im Rahmen der Hotchips stellte ein Unternehmen namens Cerebras eine sogenannte Wafer Scale Engine (WSE) vor. Dabei handelt es sich um einen Chip, der aus mehreren Komponenten auf dem Wafer zusammengesetzt wird, aber als Gesamtkonstrukt auf dem Wafer gefertigt wird. Es handelt sich also nicht um ein Chiplet-Design im eigentlichen Sinne. WikiChip hat eine aktualisierte Analyse der WSE vorgenommen. Zur Supercomputing 19 soll es... [mehr] -

Weltgrößter Chip soll 400.000 Kerne auf 46.225 mm² Chipfläche bringen

Derzeit findet in den USA die Hotchips-Konferenz statt. Auf dieser stellen die Hersteller ihre Neuerungen im Bereich der Chipentwicklung vor – darunter auch AMD, Intel, NVIDIA und viele mehr. Deren Präsentationen werden aber erst in den kommenden Tagen folgen. Im Rahmen der Hotchips hat aber auch ein Startup namens Cerebras seine ambitionierten Pläne veröffentlicht. Die von Cerebras geplante Hardware in Form eines Chips setzt das... [mehr]

Derzeit findet in den USA die Hotchips-Konferenz statt. Auf dieser stellen die Hersteller ihre Neuerungen im Bereich der Chipentwicklung vor – darunter auch AMD, Intel, NVIDIA und viele mehr. Deren Präsentationen werden aber erst in den kommenden Tagen folgen. Im Rahmen der Hotchips hat aber auch ein Startup namens Cerebras seine ambitionierten Pläne veröffentlicht. Die von Cerebras geplante Hardware in Form eines Chips setzt das... [mehr]