Werbung

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei Kernkomponenten. CoWoS-L soll ab 2027 Packages ermöglichen, die mit 4.500 mm² an die Grenzen des Möglichen gehen werden.

Allerdings geht TSMC damit auch an die Grenzen dessen, was sich noch sinnvoll als Substrat bzw. Interposer auf einem Wafer fertigen lässt. Genau wie die Chips selbst, wird auch ein Substrat bzw. SI/RDL-Interposer auf einem Wafer hergestellt. Auf diesem mit einem Durchmesser von 300 mm lassen sich aber nur sehr wenige solcher großen Interposer fertigen. Bei 60 x 60 mm (3.600 mm²) reden wir von gerade einmal zwölf Interposer auf einem Wafer, von denen dann auch alle funktionieren müssen. Bei 4.500 mm² sind es sogar nur sieben Interposer auf einem Wafer. Somit werden die großen Interposer zu einer teuren Angelegenheit.

SoW-X (System on Wafer) stellt eine Alternative dar. Dabei wird ein kompletter Wafer zu einem Chip, dessen Komponenten zusammenarbeiten. Allerdings sind diese SoW-Systeme nur in wenigen Ausnahmefällen sinnvoll einsetzbar. Die Wafer Scale Engine von Cerebras ist das prominenteste Beispiel.

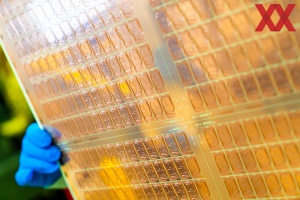

Laut Medienberichten aus Asien (via ComputerBase) arbeitet TSMC an einer Alternative zu den auf den Wafern hergestellten Interposern. Die Technik soll CoPoS heißen, was für "Chips on Panel on Substrat" steht. Anstatt den Interposer auf einem Wafer zu fertigen, geschieht dies auf einem rechteckigen Panel. Das Packaging wird demnach als Panel-level Packaging (PLP) bezeichnet.

Am Beispiel eines 4.500 mm² großen Interposers sollen die Panel-Herstellung bei einer Größe der Panels von 300 x 300 mm die Fertigung von bis zu 16 Interposer ermöglichen – bei einer Wafer-Fertigung sind es nur sieben. Später sollen die Panels mit einer Größe von 600 x 600 mm sogar eine noch bessere Ausbeute ermöglichen.

Auch in der Herstellung von Glas-Substraten setzt man auf die Panels. Intel sprach zuletzt im Jahre 2023 über Glas-Substrate als Trägermaterial für die zukünftigen Chips. Aber auch bei Samsung und TSMC wird schon seit Jahren daran geforscht. CoPoS bringt bei TSMC nun zumindest das Panel als Alternative zum Wafer in der Interposer-Herstellung auf den Tisch.

2026 soll TSMC den Aufbau einer Pilotlinie planen. 2027/28 soll die Technik dann in Richtung einer Produktreife gebracht werden. Bis zum Ende des Jahrzehnts werden wir also sicherlich noch öfter davon hören, bevor es dann zu einer konkreten Umsetzung kommt. Ähnlich sah zuletzt auch der Zeitplan bei Intel aus.