News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Interconnect

-

Mit Details zur Vera-CPU: Auch ARM nimmt am NVLink-Fusion-Ökosystem teil

Auf einer Präsentation auf der Supercomputing-Konferenz hat NVIDIA einen weiteren Partner für das NVLink-Fusion-Ökosystem angekündigt. Neben Intel, Fujitsu und Qualcomm wird auch ARM die notwendige Infrastruktur bereitstellen, damit Kunden einer ARM-Lizenz den Interconnect via NVLink Fusion nutzen können. Im Frühsommer kündigte NVIDIA an, dass NVLink externen Kunden zugänglich gemacht werden soll – entweder für Custom-CPUs oder als Bestandteil... [mehr]

Auf einer Präsentation auf der Supercomputing-Konferenz hat NVIDIA einen weiteren Partner für das NVLink-Fusion-Ökosystem angekündigt. Neben Intel, Fujitsu und Qualcomm wird auch ARM die notwendige Infrastruktur bereitstellen, damit Kunden einer ARM-Lizenz den Interconnect via NVLink Fusion nutzen können. Im Frühsommer kündigte NVIDIA an, dass NVLink externen Kunden zugänglich gemacht werden soll – entweder für Custom-CPUs oder als Bestandteil... [mehr] -

NVLink Fusion: NVIDIA öffnet NVLink-C2C für Custom-CPUs und GPUs

Neben dem durch die Rahmenbedingungen fragwürden Marktstart der GeForce RTX 5060 hat NVIDIA zur Computex auch eine Ankündigung aus dem Datacenter-Segment. NVIDIA verbindet seine eigenen CPUs und GPUs über den NVLink-Interconnect, der in der aktuell für die Blackwell-GPUs verwendeten 5. Generation auf 50 GB/s pro NVLink-Lane kommt und somit bei 18 insgesamt vorhandenen NVLink-Lanes in der Umsetzung bidirektional 1.800 GB/s erreicht. Bis zu 72... [mehr]

Neben dem durch die Rahmenbedingungen fragwürden Marktstart der GeForce RTX 5060 hat NVIDIA zur Computex auch eine Ankündigung aus dem Datacenter-Segment. NVIDIA verbindet seine eigenen CPUs und GPUs über den NVLink-Interconnect, der in der aktuell für die Blackwell-GPUs verwendeten 5. Generation auf 50 GB/s pro NVLink-Lane kommt und somit bei 18 insgesamt vorhandenen NVLink-Lanes in der Umsetzung bidirektional 1.800 GB/s erreicht. Bis zu 72... [mehr] -

Schon gelöst: GB200 soll Probleme mit dem Spine-Interconnect gehabt haben

Bereits häufiger war zusammen mit NVIDIAs GB200-Systemen von Problemen die Rede und nun kommt ein weiterer Bericht hinzu, dessen Legitimität jedoch stark in Frage zu stellen ist, als dies bei den anderen Meldungen der Fall war. Der in Taiwan ansässige Analyst Dan Nystedt berichtet via X, dass Microsoft 40 % seiner Bestellungen an GB200-KI-Servern storniert habe, da diese später als erwartet ausgeliefert würden. Die Auslieferung... [mehr]

Bereits häufiger war zusammen mit NVIDIAs GB200-Systemen von Problemen die Rede und nun kommt ein weiterer Bericht hinzu, dessen Legitimität jedoch stark in Frage zu stellen ist, als dies bei den anderen Meldungen der Fall war. Der in Taiwan ansässige Analyst Dan Nystedt berichtet via X, dass Microsoft 40 % seiner Bestellungen an GB200-KI-Servern storniert habe, da diese später als erwartet ausgeliefert würden. Die Auslieferung... [mehr] -

Black Semiconductor: Deutsches Startup arbeitet an optischen Interconnects aus Graphen

Ein Startup aus Aachen arbeitet an Halbleitertechniken, die in der Zukunft vielleicht einmal eine größere Rolle spielen werden. Konkret geht es um schnelle Interconnects, wie sie bereits heute zum Einsatz kommen, anstatt einer rein elektrischen Verbindung per SerDes oder einer optoelektrischen Lösung mit Glas als Übertragungsmedium setzt Black Semiconductor auf Graphen. Graphen gilt in vielen Bereichen als möglicher Wunder-Werkstoff... [mehr].

Ein Startup aus Aachen arbeitet an Halbleitertechniken, die in der Zukunft vielleicht einmal eine größere Rolle spielen werden. Konkret geht es um schnelle Interconnects, wie sie bereits heute zum Einsatz kommen, anstatt einer rein elektrischen Verbindung per SerDes oder einer optoelektrischen Lösung mit Glas als Übertragungsmedium setzt Black Semiconductor auf Graphen. Graphen gilt in vielen Bereichen als möglicher Wunder-Werkstoff... [mehr]. -

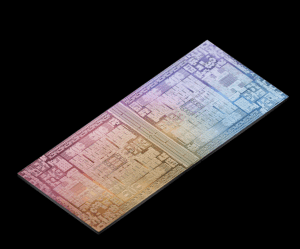

Apple M3 Ultra: Ohne UltraFusion-Interconnect und als monolithisches Design

Bisher hat Apple seine MacBooks mit M3, M3 Pro und M3 Max auf den Markt gebracht – vom M3 Ultra fehlt aber noch jede Spur und es gibt aktuell auch kaum Hinweise dazu, dass dieser in Kürze im Mac Studio oder Mac Pro erscheinen wird. Erst Anfang März wurden das 13" und 15" MacBook Air auf den M3 und M3 Pro umgestellt, während es den M3 Max nur im MacBook Pro gibt. Bisher ist Apple in seiner M-Serie immer so vorgegangen, dass die M-, Pro- und... [mehr]

Bisher hat Apple seine MacBooks mit M3, M3 Pro und M3 Max auf den Markt gebracht – vom M3 Ultra fehlt aber noch jede Spur und es gibt aktuell auch kaum Hinweise dazu, dass dieser in Kürze im Mac Studio oder Mac Pro erscheinen wird. Erst Anfang März wurden das 13" und 15" MacBook Air auf den M3 und M3 Pro umgestellt, während es den M3 Max nur im MacBook Pro gibt. Bisher ist Apple in seiner M-Serie immer so vorgegangen, dass die M-, Pro- und... [mehr] -

AMD Accelerator Fabric Link: Broadcom will direkte GPU-Anbindung umsetzen

Zusammen mit der Vorstellung der HPC- und KI-Beschleuniger Instinct MI300X und Instinct MI300X verkündete AMD, dass man für eine zukünftige Skalierung seiner Hardware auch auf eine schnelle Anbindung an das Netzwerk, bzw. die Interconnects angewiesen ist und hier den Accelerator Fabric Link (AFL) anbieten möchte, an den sich auch externe Hardware anknüpfen kann. Accelerator Fabric Link ist als Gegenstück zu NVIDIAs NVLink gedacht. Per NVLink... [mehr]

Zusammen mit der Vorstellung der HPC- und KI-Beschleuniger Instinct MI300X und Instinct MI300X verkündete AMD, dass man für eine zukünftige Skalierung seiner Hardware auch auf eine schnelle Anbindung an das Netzwerk, bzw. die Interconnects angewiesen ist und hier den Accelerator Fabric Link (AFL) anbieten möchte, an den sich auch externe Hardware anknüpfen kann. Accelerator Fabric Link ist als Gegenstück zu NVIDIAs NVLink gedacht. Per NVLink... [mehr] -

RISC-V-Konferenz: Details zur Chiplet-Architektur und dem P550-Nachfolger

Vom 6. bis zum 8. Dezember wird das RISC-V Summit stattfinden. SiFive kündigt für die Konferenz einige Neuigkeiten an. Auf der Supercomputing 2021 spielte das Thema RISC-V noch eine untergeordnete Rolle, dies soll sich jedoch in Zukunft ändern. Chiplets und der Nachfolger des P550 sollen der Fokus für SiFive sein. Bereits vor einigen Wochen gab SiFive erste Details zum Next-Gen P-Series-Kern preis. Dieser soll noch einmal um 50 % schneller als... [mehr]

Vom 6. bis zum 8. Dezember wird das RISC-V Summit stattfinden. SiFive kündigt für die Konferenz einige Neuigkeiten an. Auf der Supercomputing 2021 spielte das Thema RISC-V noch eine untergeordnete Rolle, dies soll sich jedoch in Zukunft ändern. Chiplets und der Nachfolger des P550 sollen der Fokus für SiFive sein. Bereits vor einigen Wochen gab SiFive erste Details zum Next-Gen P-Series-Kern preis. Dieser soll noch einmal um 50 % schneller als... [mehr] -

CXL setzt sich durch: Gen-Z geht in Compute Express Link auf

Im Frühjahr 2020 vereinbarten das Gen-Z- und CXL-Konsortium ein Memorandum of Understanding, welches eine Kollaboration zwischen den beiden Unternehmen vorsieht. Bei Interconnect-Technologien auf Basis von CXL und Gen-Z sollten beide Techniken zueinander kompatibel gemacht werden. Die Einsatzfelder beider Technologien werden ebenfalls auf eine Zusammenarbeit ausgelegt. Nun haben beide Konsortien bekanntgegeben, dass sie... [mehr]

Im Frühjahr 2020 vereinbarten das Gen-Z- und CXL-Konsortium ein Memorandum of Understanding, welches eine Kollaboration zwischen den beiden Unternehmen vorsieht. Bei Interconnect-Technologien auf Basis von CXL und Gen-Z sollten beide Techniken zueinander kompatibel gemacht werden. Die Einsatzfelder beider Technologien werden ebenfalls auf eine Zusammenarbeit ausgelegt. Nun haben beide Konsortien bekanntgegeben, dass sie... [mehr] -

Grace: NVIDIA kombiniert ARM-Prozessor, GPU und schnellen Interconnect

Auf der GPU Technology Conference stellt NVIDIA mit Grace einen eigenen HPC-ARM-Prozessor vor, welcher in zukünftigen Supercomputern zum Einsatz kommen soll. Benannt ist der Prozessor nach Grace Hopper. Hopper war eine Informatikerin und Computerpionierin, die sich vor allem mit ihrer Arbeit, Computerprogramme in einer verständlichen Sprache zu verfassen, einen Namen gemacht hat. Der Grace-Prozessor soll als Basis eine kommenden... [mehr]

Auf der GPU Technology Conference stellt NVIDIA mit Grace einen eigenen HPC-ARM-Prozessor vor, welcher in zukünftigen Supercomputern zum Einsatz kommen soll. Benannt ist der Prozessor nach Grace Hopper. Hopper war eine Informatikerin und Computerpionierin, die sich vor allem mit ihrer Arbeit, Computerprogramme in einer verständlichen Sprache zu verfassen, einen Namen gemacht hat. Der Grace-Prozessor soll als Basis eine kommenden... [mehr] -

OpenFive stellt Interconnect-PHY für zukünftige Chiplet-Designs vor

OpenFive, eine Tochter von SiFive, die wiederum Kern-IP und Designs auf Basis der freien RISC-V-Befehlssatzstruktur entwickelt, hat ein Die-to-Die-Interface für Chiplets vorgestellt, welches eine Alternative zu Intels EMIB oder Foveros, bzw. den verschiedenen 3DFabric-Technologien von TSMC sein soll. OpenFive bietet bereits verschiedene Die-to-Die-Interfaces (D2D) an, die mit einer Bandbreite von 1.024 Bit sowie bei einem Takt von 2... [mehr]

OpenFive, eine Tochter von SiFive, die wiederum Kern-IP und Designs auf Basis der freien RISC-V-Befehlssatzstruktur entwickelt, hat ein Die-to-Die-Interface für Chiplets vorgestellt, welches eine Alternative zu Intels EMIB oder Foveros, bzw. den verschiedenen 3DFabric-Technologien von TSMC sein soll. OpenFive bietet bereits verschiedene Die-to-Die-Interfaces (D2D) an, die mit einer Bandbreite von 1.024 Bit sowie bei einem Takt von 2... [mehr] -

CXL 2.0 wird Switching und Persistent Memory unterstützen

Der erst 2019 ins Leben gerufene, offene Interconnect-Standard Compute Express Link oder kurz CXL wurde nun um die ersten Daten zur Spezifikation 2.0 erweitert. Auch wenn CXL mit Intel, NVIDIA, AMD, ARM und vielem mehr bereits große Namen in seinem Konsortium zusammenführen kann, so gibt es bislang erst wenig bis keine Hardware, die CXL konkret umsetzt. Dies wird sich allerdings 2021 mit der Einführung der ersten PCI-Express-5.0-Hardware... [mehr]

Der erst 2019 ins Leben gerufene, offene Interconnect-Standard Compute Express Link oder kurz CXL wurde nun um die ersten Daten zur Spezifikation 2.0 erweitert. Auch wenn CXL mit Intel, NVIDIA, AMD, ARM und vielem mehr bereits große Namen in seinem Konsortium zusammenführen kann, so gibt es bislang erst wenig bis keine Hardware, die CXL konkret umsetzt. Dies wird sich allerdings 2021 mit der Einführung der ersten PCI-Express-5.0-Hardware... [mehr] -

Samsung entwickelt Bornitrid-Graphen als Interconnect-Trennschicht

Samsung vermeldet eine weitere Neuentwicklung aus dem Bereich der Halbleiterherstellung. Sogenanntes amorphes Bornitrid-Graphen oder auch weißes Graphen soll als Trennschichten in Halbleiterbauelementen zum Einsatz kommen. Das amorphe Bornitrid-Graphen ist eine gemeinsame Entwicklung des Samsung Advanced Institute of Technology (SAIT), des Ulsan National Institute of Science and Technology (UNIST) in Korea und der University of Cambridge. Das... [mehr]

Samsung vermeldet eine weitere Neuentwicklung aus dem Bereich der Halbleiterherstellung. Sogenanntes amorphes Bornitrid-Graphen oder auch weißes Graphen soll als Trennschichten in Halbleiterbauelementen zum Einsatz kommen. Das amorphe Bornitrid-Graphen ist eine gemeinsame Entwicklung des Samsung Advanced Institute of Technology (SAIT), des Ulsan National Institute of Science and Technology (UNIST) in Korea und der University of Cambridge. Das... [mehr] -

Interconnect-Technologie: CXL und Gen-Z arbeiten zukünftig zusammen

Das Gen-Z- und CXL-Konsortium hat ein Memorandum of Understanding (MOU) vereinbart, welches eine Kollaboration zwischen den beiden Unternehmen vorsieht. Bei Interconnect-Technologien sollen über eine Brücke zueinander kompatibel gemacht werden. Die Einsatzfelder beider Technologien werden ebenfalls auf eine Zusammenarbeit ausgelegt. CXL (Compute Express Link) ist ein ursprünglich von Intel ins Leben gerufener Standard für einen schnellen... [mehr]

Das Gen-Z- und CXL-Konsortium hat ein Memorandum of Understanding (MOU) vereinbart, welches eine Kollaboration zwischen den beiden Unternehmen vorsieht. Bei Interconnect-Technologien sollen über eine Brücke zueinander kompatibel gemacht werden. Die Einsatzfelder beider Technologien werden ebenfalls auf eine Zusammenarbeit ausgelegt. CXL (Compute Express Link) ist ein ursprünglich von Intel ins Leben gerufener Standard für einen schnellen... [mehr] -

Gemeinsamer Speicher: Infinity Fabric zwischen EPYC-CPUs und Radeon-Instinct-GPUs

Derzeit nutzt AMD den Infinity Fabric als Interconnect innerhalb des Chiplet-Designs (für die Kommunikation zwischen Compute- und I/O-Dies) und um mehrere GPUs miteinander zu verbinden. Zusammen mit der Zen-2-Architektur hat AMD den Infinity Fabric auf die Generation zwei gehievt und dabei unter anderem die Busbreite von 256 auf 512 Bit erhöht. Zum einen wird die höhere Bandbreite für die interne Kommunikation benötigt, aber auch für schnelle... [mehr]

Derzeit nutzt AMD den Infinity Fabric als Interconnect innerhalb des Chiplet-Designs (für die Kommunikation zwischen Compute- und I/O-Dies) und um mehrere GPUs miteinander zu verbinden. Zusammen mit der Zen-2-Architektur hat AMD den Infinity Fabric auf die Generation zwei gehievt und dabei unter anderem die Busbreite von 256 auf 512 Bit erhöht. Zum einen wird die höhere Bandbreite für die interne Kommunikation benötigt, aber auch für schnelle... [mehr] -

Für 3DS DRAM und HBM: SK Hynix lizensiert DBI Ultra Interconnect

Der zunehmende Bedarf an 2,5- und 3D-Packaging-Technologien geht an SK Hynix nicht vorbei. Dazu hat man sich nun bei der Xperi Corporation bedient und mit dem eher unbekannten Technologie-Unternehmen ein Lizenzabkommen geschlossen, welches die DBI Ultra getaufte Interconnect-Technik umfasst. Entwickelt wurde die Technik jedoch nicht von Xperi selbst, sondern von Invensas. DBI Ultra soll es ermöglichen, bis zu 16 Speicherlayer... [mehr]

Der zunehmende Bedarf an 2,5- und 3D-Packaging-Technologien geht an SK Hynix nicht vorbei. Dazu hat man sich nun bei der Xperi Corporation bedient und mit dem eher unbekannten Technologie-Unternehmen ein Lizenzabkommen geschlossen, welches die DBI Ultra getaufte Interconnect-Technik umfasst. Entwickelt wurde die Technik jedoch nicht von Xperi selbst, sondern von Invensas. DBI Ultra soll es ermöglichen, bis zu 16 Speicherlayer... [mehr] -

Silizium im Fokus: Intel zeigt einen EMIB-Chip

Im Hinblick auf die aktuelle Marktsituation bei den Desktop- und HEDT-Prozessoren hat Intel derzeit nicht viel bewundernswertes zu präsentieren (siehe Test zum Core i9-10980XE und den Ryzen-Threadripper-Prozessoren der 3. Generation), aber immerhin im Hinblick auf zukünftige Technologien scheint Intel sich wieder für einen härteren Kampf zu rüsten. EMIB (Embedded Multi Die Interconnect Bridge) ist eine dieser Technologien, die im Falle des... [mehr]

Im Hinblick auf die aktuelle Marktsituation bei den Desktop- und HEDT-Prozessoren hat Intel derzeit nicht viel bewundernswertes zu präsentieren (siehe Test zum Core i9-10980XE und den Ryzen-Threadripper-Prozessoren der 3. Generation), aber immerhin im Hinblick auf zukünftige Technologien scheint Intel sich wieder für einen härteren Kampf zu rüsten. EMIB (Embedded Multi Die Interconnect Bridge) ist eine dieser Technologien, die im Falle des... [mehr] -

NVIDIA startet Serverinitiative für ARM-CPUs - Magnum IO für mehr Bandbreite

NVIDIA kündigt zur Supercomputing 19 ein Referenzdesign für Server mit ARM-Prozessoren an – natürlich kombiniert mit den eigenen GPU-Beschleunigern. Zusammen mit ARM, Ampere, Cray, Fujitsu, HPE und Marvell wurde die Referenzplattform entwickelt, die dabei helfen soll, dass schnellstmöglich auch fertige Systeme auf den Markt kommen. Derzeit verwendet NVIDIA in den eigenen Servern für die Anbindung der GPU-Beschleuniger meist Prozessoren aus dem... [mehr]

NVIDIA kündigt zur Supercomputing 19 ein Referenzdesign für Server mit ARM-Prozessoren an – natürlich kombiniert mit den eigenen GPU-Beschleunigern. Zusammen mit ARM, Ampere, Cray, Fujitsu, HPE und Marvell wurde die Referenzplattform entwickelt, die dabei helfen soll, dass schnellstmöglich auch fertige Systeme auf den Markt kommen. Derzeit verwendet NVIDIA in den eigenen Servern für die Anbindung der GPU-Beschleuniger meist Prozessoren aus dem... [mehr] -

TSMC plant neue Packaging-Technologien und 1,4-nm-Fertigung

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten... [mehr]

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten... [mehr] -

TSMC zeigt riesiges Chiplet-Design mit ebenso gigantischem Interposer

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost. Dabei gibt Cheng erstaunliche Einblicke... [mehr]

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost. Dabei gibt Cheng erstaunliche Einblicke... [mehr] -

Auch NVIDIA nun Mitglied des CXL-Consortiums

Der von Intel initiierte und im März angekündigte neue Standard für einen schnellen Interconnect, Compute Express Link (CXL), hat einen weiteren prominenten Neuzugang zu verzeichnen. Nachdem AMD im Juli Mitglied des Konsortiums wurde, ist nun offenbar auch NVIDIA beigetreten. CXL wird auf PCI-Express als physikalische Trägertechnologie verwenden. AMD führte erst kürzlich PCI-Express 4.0 im Heimanwender- (Ryzen-3000-Serie) und... [mehr]

Der von Intel initiierte und im März angekündigte neue Standard für einen schnellen Interconnect, Compute Express Link (CXL), hat einen weiteren prominenten Neuzugang zu verzeichnen. Nachdem AMD im Juli Mitglied des Konsortiums wurde, ist nun offenbar auch NVIDIA beigetreten. CXL wird auf PCI-Express als physikalische Trägertechnologie verwenden. AMD führte erst kürzlich PCI-Express 4.0 im Heimanwender- (Ryzen-3000-Serie) und... [mehr] -

Intel Interconnect Day 2019: Details zum CXL-Interconnect

Nach einer noch recht offen gehaltenen Ankündigung des Compute Express Link oder kurz CXL hat Intel auf einem Interconnect Day 2019 erste genauere Details zur Technik und dem Einsatzbereich verraten. CXL wird von Intel als ein offener Standard bezeichnet, allerdings wird der Zugang zu den dazu notwendigen Details nicht offen gestaltet. Vielmehr stellt Intel CXL als Konkurrenzprodukt zu CCIX, OpenCAPI und Gen-Z auf. Zunächst einmal... [mehr]

Nach einer noch recht offen gehaltenen Ankündigung des Compute Express Link oder kurz CXL hat Intel auf einem Interconnect Day 2019 erste genauere Details zur Technik und dem Einsatzbereich verraten. CXL wird von Intel als ein offener Standard bezeichnet, allerdings wird der Zugang zu den dazu notwendigen Details nicht offen gestaltet. Vielmehr stellt Intel CXL als Konkurrenzprodukt zu CCIX, OpenCAPI und Gen-Z auf. Zunächst einmal... [mehr] -

Intel macht den CXL-Interconnect zu einem neuen Standard

Intel hat angekündigt, den intern entwickelten Interconnect namens Compute Express Link oder kurz CXL, zu einem Standard zu machen, den man gemeinsam mit anderen Unternehmen einsetzen und weiterentwickeln will. Zu den ersten Partnern im Konsortium gehören Alibaba, Cisco, Dell EMC, Facebook, Google, Hewlett Packard Enterprise, Huawei und Microsoft. Nach CCIX, OpenCAPI und Gen-Z ist CXL die nun vierte Interconnect-Entwicklung der letzten... [mehr]

Intel hat angekündigt, den intern entwickelten Interconnect namens Compute Express Link oder kurz CXL, zu einem Standard zu machen, den man gemeinsam mit anderen Unternehmen einsetzen und weiterentwickeln will. Zu den ersten Partnern im Konsortium gehören Alibaba, Cisco, Dell EMC, Facebook, Google, Hewlett Packard Enterprise, Huawei und Microsoft. Nach CCIX, OpenCAPI und Gen-Z ist CXL die nun vierte Interconnect-Entwicklung der letzten... [mehr] -

Füttern der Bestie: PNY PURE AIRI verbindet HPC mit Storage und Netzwerk

Seit einigen Jahren bietet NVIDIA Systeme für das High Performance Computing und Deep-Learning-Anwendungen an. Über seine Partner wie IBM, Dell, HPE und einige andere sind entsprechende Server ebenfalls für entsprechende Anwendungen verfügbar. PNY ist seit 2003 der exklusive Partner für den Verkauf der Hardware von NVIDIA im Bereich von Quadro- und Tesla-Karten und bietet seit einiger Zeit auch auf Kundenwunsch gefertigte HPC-Server an. Dieses... [mehr]

Seit einigen Jahren bietet NVIDIA Systeme für das High Performance Computing und Deep-Learning-Anwendungen an. Über seine Partner wie IBM, Dell, HPE und einige andere sind entsprechende Server ebenfalls für entsprechende Anwendungen verfügbar. PNY ist seit 2003 der exklusive Partner für den Verkauf der Hardware von NVIDIA im Bereich von Quadro- und Tesla-Karten und bietet seit einiger Zeit auch auf Kundenwunsch gefertigte HPC-Server an. Dieses... [mehr] -

NVIDIAs HGX-2 bietet 2 PFLOPS an Rechenleistung

Zur GPU Technologies Conference im vergangenen Jahr stellte NVIDIA mit dem HGX-1 ein Serversystem vor, welches im Grunde genommen eine wassergekühlte Variante des DGX-1 und für den Einsatz in der HPC-Cloud vorgesehen ist. In diesem Jahr hat NVIDIA die Varianten der Tesla V100 mit 32 GB, also verdoppelten HBM2, vorgestellt. Auch die Quadro V100 ist seit dem Frühjahr in dieser Ausbaustufe verfügbar. Heute nun stellt NVIDIA das HGX-2 vor... [mehr].

Zur GPU Technologies Conference im vergangenen Jahr stellte NVIDIA mit dem HGX-1 ein Serversystem vor, welches im Grunde genommen eine wassergekühlte Variante des DGX-1 und für den Einsatz in der HPC-Cloud vorgesehen ist. In diesem Jahr hat NVIDIA die Varianten der Tesla V100 mit 32 GB, also verdoppelten HBM2, vorgestellt. Auch die Quadro V100 ist seit dem Frühjahr in dieser Ausbaustufe verfügbar. Heute nun stellt NVIDIA das HGX-2 vor... [mehr].