Werbung

Neben der Vorstellung der kommenden Notebook-Prozessoren alias Panther Lake gab Intel auf der US-Tech-Tour auch einige Details zu den kommenden Xeon-Prozessoren mit E-Kernen bekannt. Erste konkrete Daten zum technischen Aufbau gab es bereits auf der Hot Chips 2025 im August. Nun wurde aber beispielsweise verkündet, dass Clearwater Forest als Xeon 6+ vermarketet werden wird, was auch durchaus Sinn macht, denn als Nachfolger der Xeon-6900E-Serie, der nie frei über die OEMs erhältlich war, setzt Clearwater Forest auf die gleiche Plattform.

Für Intel sind die Xeon-Prozessoren rein mit E-Kern-Bestückung inzwischen zu einem wichtigen Markt geworden. Sierra Forest und hier vor allem die "kleineren" Xeon-6700E-Varianten mit bis zu 144 Kernen haben vor allem im Segment der Telekommunikation und Infrastruktur ihren Platz gefunden.

Bereits letztes Jahr hatte Intel die 6700E-Modelle mit bis zu 144 Effizienz- und die 6900P-Reihe mit bis zu 128 Performance-Kernen vorgestellt. In diesem Jahr erfolgte die Einführung der 6700P/6500P-Serien sowie der 6900E-Modelle – letztgenannte gingen aber nur an einige Hyperscaler. In den vergangnen Jahren verzeichnete Intel rückläufige Absätze im Datacenter-Bereich, während AMD dem langjährigen Marktführer zunehmend Marktanteile abspenstig macht. Die Xeon-6-Serie sollte die Kehrtwende einläuten, aber noch ist nicht klar, ob dies auch gelungen ist.

Clearwater Forest ist der Nachfolger von Sierra Forest und setzt damit ausschließlich auf die kompakteren und sparsameren Efficiency-Kerne.

Zur Einordnung vorweg: Die Xeon-6-Prozessoren mit Performance-Kernen (Granite Rapids) verwenden die Redwood-Cove-Architektur und für die Prozessoren mit Efficiency-Kernen (Sierra Forest) die Crestmont-Architektur. Grundsätzlich ist es möglich, innerhalb einer Plattform beide Kerne zum Einsatz zu bringen. Die 6900-Serie setzt auf den LGA7529 mit zwölf Speicherkanälen und bis zu 96 PCIe/CXL-Lanes und die 6700-Reihe auf den LGA7529 mit acht Speicherkanälen und 88 PCIe/CXL-Lanes

288 Kerne mit schnellem Speicher und viel Cache

Auch die Xeon-6+-Prozessoren werden den LGA7529 mit zwölf Speicherkanälen und bis zu 96 PCIe/CXL-Lanes verwenden. Damit bleibt die Plattform kompatibel und die Serverhersteller können problemlos von Sierra Forest auf Clearwater Forest umstellen.

Auch Clearwater Forest wird genau wie Panther Lake in den Notebooks E-Kerne auf Basis der Darkmont-Architektur verwenden. Aus Sicht der Mikroarchitektur gibt es keinerlei Unterschiede in der Umsetzung der Darkmont-Kerne in Panther Lake und Clearwater Forest. Entsprechend verweisen wir an dieser Stelle auf die Details zu den E-Kernen aus unserem Artikel zu Panther Lake.

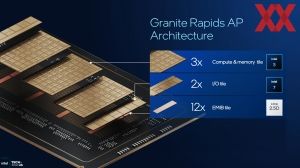

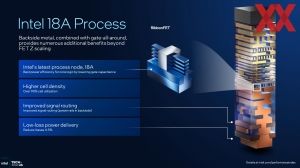

So richtig spannend wird es beim Aufbau von Clearwater Forest. In der größten Ausbaustufe setzt Intel auf zwölf Compute-Tiles, die auf drei Base-Tiles verteilt sind. Die Compute-Tiles entstehen im Intel-18A-Prozess, während die Base-Tiles ebenfalls bei Intel gefertigt werden – diesmal im Intel-3-(Intel-3T)-Verfahren.

Die E-Kerne organisiert Intel erneut in Clustern mit je vier Kernen, denen jeweils 4 MB L2-Cache zur Verfügung stehen. Die Cache-Bandbreite beträgt 200 GB/s pro Kern, und die Verbindung der Cluster zum Chip erfolgt über einen Interconnect Fabric mit 35 GB/s. Insgesamt sollen die Clearwater-Forest-Prozessoren bis zu 288 Kerne bieten, was bei zwölf Compute-Tiles 96 Kerne pro Tile und somit 24 CPU-Cluster pro Compute-Tile bedeutet.

Ergänzt werden die zwölf Compute-Tiles und drei Base-Tiles durch zwei I/O-Tiles, die das Package oben und unten abschließen. Auch sie stammen aus Intels eigener Fertigung und basieren auf dem Intel-7-Prozess. Die I/O-Tiles übernehmen das Routing des Fabric-Interconnects sowie die Integration von Controllern und PHYs für PCIe, UPI, CXL und Beschleunigereinheiten.

Die DDR5-Speichercontroller befinden sich bei Clearwater Forest nun nicht mehr in den Compute-, sondern in den Base-Tiles, neben einem großen LLC (Last Level Cache). Base- und I/O-Tiles sind über EMIB auf dem Interposer verbunden, während die Compute-Tiles mittels Foveros Direct 3D auf die Base-Tiles gestapelt werden.

Damit umfasst das Clearwater-Forest-Package insgesamt 17 aktive Chips – was stark an Ponte Vecchio erinnert, diesmal jedoch hoffentlich mit erfolgreicherem Ergebnis.

Von Crestmont auf Darkmont

Panther Lake und Clearwater Forest setzen beide auf E-Kerne auf Basis der Darkmont-Architektur. Allerdings kann Panther Lake auf einen Vorgänger verweisen, dessen E-Kerne schon auf Skymont basierten, während Sierra Forest als Vorgänger von Clearwater Forest noch auf die Crestmont-Kerne setzte. Insofern hat der Generationenvergleich hier unterschiedliche Grundvoraussetzungen.

Sowohl Cougar Cove wie auch Darkmont sind Iterationen der jeweiligen Vorgänger Lion Cove und Skymont. Insofern sind hauptsächlich Optimierungen im Bereich der Sprungvorhersage und andere Details für ein kleines IPC-Plus verantwortlich.

Die Darkmont-Kerne in Clearwater Forest müssen hingegen gegen die Skymont-Kerne verglichen werden - und hier sind die Änderungen schon deutlich umfangreicher. Mit Darkmont wechselt Clearwater Forest auf eine deutlich breitere Kern-Architektur, die auf einen hohen Durchsatz ausgelegt ist. Die Xeon-6+-Prozessoren werden dadurch einen deutlichen Sprung nach vorne machen in der Leistung, wenngleich Intel noch keine konkreten bzw. umfangreichen Leistungsvergleiche anzubieten hatte.

Der I/O-Tile wird wiederverwendet

Um die Kompatibilität zur Xeon-6-Plattform gewährleisten zu können, nutzt Intel nicht nur den gleichen Sockel LGA7529, sondern auch den gleichen I/O-Tile.

Jeweils zwei I/O-Tiles kommen zum Einsatz und steuern damit auch die bis zu acht Beschleuniger (Intel QuickAssist Technology, Intel Dynamic Load Balancer, Intel Data Streaming Accelerator, Intel In-Memory Analytics Accelerator), 48 PCIe-5.0-Lanes und wahlweise bis zu 32 CXL-2.0-Lanes und für die Kommunikation zwischen zwei Sockeln bis zu 96 UPI-2.0-Lanes je Tile bei.

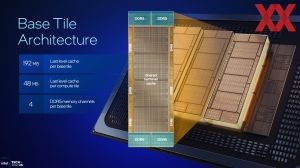

Der Base-Tile beherrbergt unter anderem bis zu 192 MB an LLC (Last Level Cache) sowie vier Speichercontroller. Bei Granite Rapids-AP und auch Sierra Forest-AP haben sich diese in den Compute-Tiles befinden, für Clearwater Forest nutzt Intel den Base-Tile auch für diese Aufgabe. Sechs EMIB-Schnittstellen, vier große und zwei kleinere, stellen die Verbindung zum jeweils nächsten Base-Tile bzw. am Rand zu den I/O-Tiles her.

Oben auf dem Base-Tile sitzen jeweils vier Compute-Tiles. Diese bestehen aus jeweils sechs Modulen und jedes Modul ist zugleich auch ein E-Kern-Cluster mit jeweils vier Kernen. Genau wie bei Panther Lake und auch schon anderen E-Kern-Konfigurationen teilen sich die vier Kerne einen 4 MB fassenden L2-Cache. Aus 6 x 4 ergeben sich 24 E-Kerne je Compute-Tile und bei 12 Compute-Tiles entsprechend bis zu 288 Kerne.

Für die Verbindung der Base-Tiles untereinander und zu den I/O-Tiles verwendet Intel die Embedded Multi-Die Interconnect Bridge (EMIB). Insgesamt 12 EMIBs kommen zum Einsatz. Die vertikale Integration der Compute-Tiles auf dem Base-Tile erfolgt mit Clearwater Forest erstmals per Foveros Direct 3D. Bei Foveros Direct 3D handelt es sich um ein Hybrid-Bonding auf Kupferbasis. Der Bump Pitch, also der Abstand zwischen den einzelnen Verbindungen liegt bei nur noch 9 µm und somit kann Intel die Vielzahl an Verbindungen zwischen dem Compute- und Base-Tile überhaupt erst herstellen.

Wichtig ist aber auch, dass die Kommunikation über diese physikalische Schnittstelle möglichst effizient erfolgt. Bei 50 nJ/Bit bzw. 0,05 pJ/Bit ist Intel hier inzwischen angekommen. Die Verbindung mittels EMIB ist mit einem Pump Pitch von 45 µm möglich. Bei 0,25 pJ/Bit sprechen wir hier aber auch von einer vergleichsweise energiehungrigen Übertragung.

Clearwater Forest ab 2026

Die Grundstruktur zu Clearwater Forest ist nun bekannt. Bis zu 288 Kerne, 576 MB LLC, eine TDP-Spanne von 300 bis 500 W, 12 Speicherkanäle mit DDR5-8000. All das auf Basis der aktuellen Birch-Stream-Plattform.

Was uns noch konkret fehlt, sind die CPU-Varianten, die Intel vorsehen wird. Innerhalb der Xeon-6700E-Serie reichte die Spanne von 64 bis 144 Kernen. Die 288 Kerne von Clearwater Forest stellen nur den Vollausbau dar.

Aber Intel hat auch noch etwas Zeit. Im ersten Halbjahr 2026, eher später in diesem Zeitraum, wird mit der Einführung der Xeon-6+-Prozessoren gerechnet.

Hardwareluxx hat die Informationen zu diesem Artikel von Intel durch Einladung des Redakteurs zur Intel Tech Tour US in Phoenix, im Bundesstaat Arizona, erhalten.