Werbung

Mit Panther Lake wird Intel im kommenden Jahr eine weitere Core-Generation für Notebooks auf den Markt bringen. Vermutlich werden diese als Core-Ultra-300-Serie auf den Markt kommen, zum aktuellen Zeitpunkt aber spricht Intel noch nicht über solch einzelnen Produktdetails, sondern hat im Rahmen der diesjährigen Intel Tech Tour über den Aufbau und die architektonischen Details von Panther Lake gesprochen. Auf eben diese wollen wir in diesem Artikel genauer eingehen.

Auch in diesem Jahr hat Intel für eine neue Produktserie eine sogenannte Intel Tech Tour (ITT) veranstaltet. Dazu wurde die Tech-Presse nach Phoenix, im US-Bundesstaat Arizona, eingeladen. Hintergrund dieser Ortswahl ist die Tatsache, dass Intel hier in seiner Fab 52 in Chandler Chips in Intel 18A, der aktuell fortschrittlichsten Fertigungstechnik, vom Band laufen lässt.

Aber die Fertigung ist nur ein Aspekt für Panther Lake. Eine neue Fertigung (sowohl intern wie auch extern), ein modernes Packaging und neue IP für CPU, GPU und I/O werden hier zu einem neuen Produkt zusammengeführt, das in seinen Kernkomponenten aber auf vielem Bekannten basiert. Im Grunde kann man Panther Lake kurz und knapp wie eine Zusammenführung von Lunar Lake (Basisartikel) und Arrow Lake (Basisartikel) beschreiben.

Die Anleihen aus Lunar und Arrow Lake für Panther Lake stammen aus den unterschiedlichsten Bereichen. So handelt es sich bei den Chips für Panther Lake um ein desintegriertes System aus mehreren Tiles. Anders als bei Arrow Lake (und auch den Vorgängern wie Meteor Lake) hat Intel die Konstruktion aber vereinfacht und setzt auf nur drei Tiles: Einen Compute Tile mit den CPU-Kernen und dem Speichercontroller, einen Platform Controller Tile mit den I/O-Funktionen wie PCI-Express sowie einen GPU Tile. Zudem gibt es noch zwei Filler Tiles, um die Fläche des Chips rechteckig gestalten zu können, was für die mechanischen und elektrischen Aspekte des Chipdesigns wichtig ist.

Für die Fertigung greift Intel auf eine Mischung aus internen und externen Fertigungsprozessen zurück:

- Base Tile: Intel 22FFL (P1227.2)

- Compute Tile: Intel 18A

- Platform Controller Tile: TSMC N6

- GPU Tile: Intel 3 oder TSMC N3E

Der Compute Tile mit den Performance- und Efficiency-Kernen wird bei Intel in Intel 18A gefertigt. Anders als bei Lunar und Arrow Lake kommt hier also nicht mehr eine externe Fertigung zum Tragen. Eine rückseitige Versorgung der Transistoren via PowerVia und die neuen Gate-All-Around-Transistoren (Intel nennt diese RibbonFET) sollen hier im Vergleich zur Fertigung in Intel 3 für ein um 15 % Leistung/W-Verhältnis und eine um 30 % höhere Transistordichte sorgen.

Für den Platform Controller Tile greift Intel dann doch auch wieder auf TSMC zurück und lässt diesen in N6 dort fertigen. Etwas komplizierter wird es für den GPU Tile. Je nach Ausführung von Panther Lake kommt hier entweder die kleinere GPU zum Einsatz die in Intel 3 gefertigt wird oder aber Intel greift auf einen etwas größeren Chip zurück, der dann wieder bei TSMC in N3E gefertigt wird.

Neue, überarbeitete P- und E-Kerne

Für Panther Lake setzt Intel auf neue Performance- und Efficiency-Kerne und auch die Low Power Island mit einem extrem sparsamen E-Kern-Cluster ist (im Hinblick auf Lunar Lake) zurück.

Es gilt weiterhin die Prämisse: Die Performance-Kerne sollen für eine möglichst hohe Single-Threaded-Leistung sorgen und die Spitzenlasten abfangen. Die Efficiency-Kerne kümmern sich um die Multi-Threaded-Anwendungen und den parallelen Betrieb der Workloads. Die Low-Power-Efficiency-Kerne hingegen verarbeiten die Hintergrundaufgaben.

Die Performance-Kerne setzen dabei auf die neue Cougar-Cove-Architektur. Allerdings handelt es sich bei Cougar Cove um eine zu Lion Cove sehr ähnliche Architektur, die in einigen Details optimierte wurde. Gleich vorweg: Ein Hyper Threading ist in der Implementierung von Cougar Cove für Panther Lake nicht vorgesehen. Die Performance-Kerne können also weiterhin nur einen Thread pro Kern verarbeiten.

Ebenfalls zum Vorgänger Lion Cove identisch ist die Anzahl der Execution Ports mit derer 18. Im Front End bleibt aber vieles identisch. Der Decoder verbleibt ebenso in einer 8-Wide-Konfiguration wie der µOP-Cache mit seiner Breite von zwölf Ausführungseinheiten. Die Aufteilung der OoO-Engine (Out-of-Order) in einen Integer- und Vektor-Teil hatte Intel ebenfalls bereits mit dem Vorgänger vorgenommen. Damit wurde man den Veränderungen in den Anforderungen durch die Workloads gerecht. Beide Bereiche haben einen eigenen Scheduler und Register Files.

Die Kapazität des TLB-Buffer (Translation Lookaside Buffer wurde um 50 % erhöht. Der TLB ist ein schneller Zwischenspeicher innerhalb der Speicherverwaltungseinheit (MMU) eines Prozessors, der kürzlich erfolgte Übersetzungen von virtuellen Speicheradressen zu physischen Speicheradressen speichert. Auch die Sprungvorhersage hat Intel weiter optimiert, was aber auch ein typischer Schritt in jeder neuen CPU-Architektur und auch wesentlicher Faktor in der Steigerung der Rechenleistung ist.

Jedem Performance-Kern stehen 3 MB an L2-Cache zur Verfügung, was ebenfalls identisch zu Lion Cove ist. Den L3-Cache, den sich alle P- und E-Kerne im Performance Cluster teilen hat Intel aber von 12 auf 18 MB vergrößert.

Memory Disambiguation ist eine essenzielle Technik in modernen Out-of-Order-Prozessoren, die es ermöglicht, Speicherzugriffe (Load- und Store-Operationen) außerhalb der ursprünglichen Programmreihenfolge auszuführen, ohne die Korrektheit des Programms zu gefährden. Diese Technik ist entscheidend für die Maximierung der Instruction-Level-Parallelität und die Leistungsoptimierung.

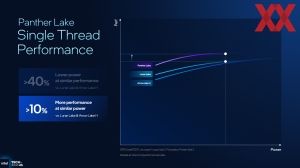

Zusammen mit der neuen Fertigung in Intel 18A will Intel aber eine deutliche Leistungssteigerung der neuen Performance-Kerne erreicht haben. Konkret soll die Single-Threaded-Leistung um 10 % gegenüber Lunar Lake und den dort verwendeten Lion-Cove-Kernen steigen.

Auch bei den Efficiency-Kernen nimmt sich Intel für Darkmont viele Anleihen bei der bisher verwendeten Skymont-Architektur. Das mit Skymont schon deutlich breiter gestaltete Front- und Backend sorgte dafür, dass die Efficiency-Kerne ein deutliches Leistungsplus erfahren haben und damit im Grunde in der ISO-Performance, also der normierten Leistung, mit Raptor Cove, der ehemaligen Performance-Kernen gleichziehen konnten.

Aber auch für Darkmont gibt es einige Optimierungen. Auch hier wurde die Sprungvorhersage verbessert und die Prefetcher können dynamischer auf die aktuellen Workload-Anforderungen reagieren.

In einer modernen Chip-Architektur werden komplexe Instruktionen über den Microcode in viele einzelne Operationen aufgeteilt, in Sequenzen organisiert und die dazugehörigen Instruktionen in einem ROM im Chip vorgehalten. Mit Darkmont führt Intel nun den sogenannten Nanocode ein, der einige dieser Instruktionen in PLAs (in Hardware) im Front-End integriert und einen schnelleren Zugriff darauf hat.

Die Technik der Memory Disambiguation hat Intel neben Cougar Cove auch in Darkmont übernommen und ermöglicht damit Speicherzugriffe außerhalb der ursprünglichen Programmreihenfolge.

Für ein Prozessor-Design und die Leistung der Kerne im Einzelnen sowie im Zusammenspiel aller Kerne spielt die Cache-Hierarchie eine wesentliche Rolle. Die Performance-Kerne haben einen exklusiven L1- und L2-Cache von 240 kB bzw. 3 MB. Die Efficiency-Kerne wiederum arbeiten in einem E-Kern-Cluster mit jeweils vier Kernen, haben ebenfalls eine jeweils eigenen L1-Cache mit 96 kB und einen gemeinsamen L2-Cache mit 4 MB, den sich die vier Kerne teilen.

Den bis zu 18 MB großen L3-Cache teilen sich die Performance- und Efficiency-Kerne des Performance-Clusters wiederum. Die Low-Power-Efficiency-Kerne wiederum haben ihren eigenen 4 MB an L2-Cache (und natürlich den privaten L1-Cache je Kern) sowie Zugriff auf den Memory Side Cache. Dieser Memory Side Cache hat eine Kapazität von 8 MB.

Die letzte Schicht der Cache-Hierarchie stellt der externe Speicher dar. Der Speichercontroller von Panther Lake bis zu 96 GB an LPDDR5X-9600 und bis zu 128 GB DDR5-7200. Das Speicherinterface dürfte weiterhin 128 Bit breit sein, welches sich aus zweimal 4x 16 Bit zusammensetzt. Aus 128 Bit x 9.600 MT/s / 8 Bit ergibt sich eine Speicherbandbreite von 153,6 GB/s. Bei Lunar Lake waren es noch 146 GB/s (128 Bit x 8.500 MT/s / 8 Bit) und auch viele anderen mobile Chips wie der Snapdragon X Elite kommen auf 135 GB/s. Beim M4 sind es 120 GB/s, der große M4 Max bei bringt es auf 546 GB/s.

Die Kommunikation zwischen den einzelnen Blöcken in den Tiles sowie zwischen den Tiles selbst findet via Scalable Fabric 2 und dem entsprechenden D2D-Interface statt.

Der Scalable Fabric 2 verbindet die P- und E-Kern-Cluster, sowie den Memory Side Cache, die NPU und GPU miteinander. Auf den Side Cache haben die Lower Power Island mit den LPE-Kernen sowie die NPU einen Zugriff. Theoretisch ist dies auch für die GPU der Fall, nur genutzt wird dieser Cache von der GPU nicht.

Über das Die-2-Die-Interface sowie den Scalable Fabric 2 werden die Daten auch zwischen dem Platform-Controller-Tile und dem Compute-Tile ausgetauscht bzw. die IP-Blöcke haben untereinander Zugriff auf den kohärenten Speicher.

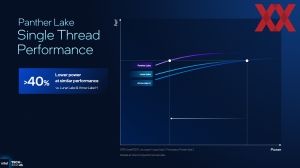

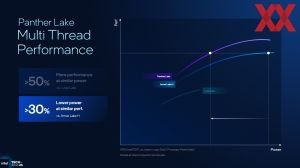

Um die Leistung der neuen Performance- und Efficiency-Kerne etwas einschätzen zu können, präsentierte Intel gleich auch einige Vergleiche zur Single- und Multi-Threaded-Leistung von Panther Lake.

Bereits angesprochen haben wir die +10 % in der Single-Threaded-Leistung der Performance-Kerne gegenüber Lunar Lake. Dabei spielt aber wohl vor allem die Fertigung in Intel 18A eine entscheidende Rolle. Mit Lunar Lake ließ Intel seinen Compute Tile bei TSMC in N3B fertigen. Der Unterschied zwischen N3B und Intel 18A scheint demnach nicht besonders groß zu sein, wenn man die geringen Änderungen in der Mikroarchitektur von Lion Cove und Cougar Cove mit einberechnet.

Wesentlich entscheidender scheint zu sein, dass die Single-Threaded-Leistung für Panther Lake bei einer um 40 % geringen Leistungsaufnahme als bei Lunar Lake und Arrow Lake-H erreicht wird.

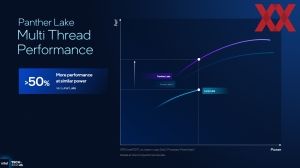

In der Multi-Threaded-Leistung spielt natürlich auch die Anzahl der Kerne eine Rolle. Intel sieht jedenfalls eine um 50 % höhere Multi-Threaded-Leistung gegenüber Lunar Lake, was bei einer 4P+8E+4LPE-Konfiguration im Vergleich zu 4P+4E-Kernen aber auch nicht weiter überraschend ist. Zudem auch hier der Blick auf die Effizienz: Eine um 30 % geringere Leistungsaufnahme bei gleicher MT-Leistung gegenüber Arrow Lake-H.

Die SoC-Power, also die Leistungsaufnahme des gesamten SoCs, will Intel im Vergleich zum schon guten Lunar-Lake-Design um 10 % reduziert haben. Gegenüber Arrow Lake sollen es sogar 40 % sein.

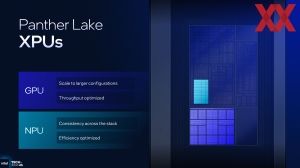

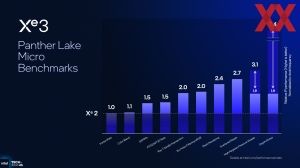

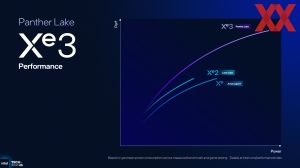

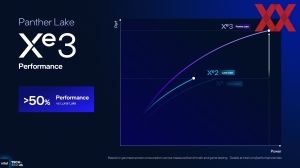

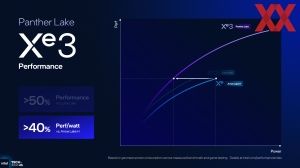

Xe3-GPU als verkappter Battlemage

Neben den neuen CPU-Kernen gibt es in Panther Lake auch eine neue GPU, die in zwei Konfigurationen angeboten werden wird. Den Codenamen Celestial vermied Intel auf dem Event, wohl auch, weil die Umsetzung der Xe-GPU in Panther Lake wohl nicht voll dem entsprechend wird, was als nächste Arc-Generation auf den Markt kommen wird. Intel spricht hier sogar von der Arc B-Series für Panther Lake, was sicherlich für einige Verwirrung beim Kunden sorgen wird.

Über den Xe-Kernen als Grundbaustein bildet der Render Slide die höhergelegene Organisationsschicht im Aufbau der GPUs von Intel. Ein Render Slide auf Basis der Xe2-Architektur bestand aus vier Xe2-Kernen mit wiederum jeweils acht Shadereinheiten sowie ebenfalls vier Raytracing-Einheiten und einem Backend aus vier Samplern, und jeweils einer Geometrie-, Rasterizer- und HiZ-Einheit.

Mit Xe3 skaliert der Render Slice auf sechs Xe3-Kerne und sechs Raytracing-Einheiten. Es bleibt bei einem Sample je Xe3-Kern, aber auch bei jeweils einer Geometrie-, Rasterizer- und HiZ-Einheit. Intel vereinfacht damit den Aufbau und macht diesen Effektiver, da eine gewisse Anzahl an Funktionseinheiten eingespart werden kann.

Der einzelne Xe3-Kern besteht aus acht 512 Bit breiten Vektoreinheiten und besitzt zudem acht XMX-Einheiten mit jeweils 2.048 Bit. Soweit ist dies identisch zu Battlemage bzw. zur Xe2-Architektur. Zwar spricht Intel von einem um 33 % größeren L1-Cache, dies trifft aber nur auf die Umsetzung von Battlemage in Lunar Lake zu, während die Xe2-Architektur für die diskreten Karten bereits 256 kB an L1-Cache vorsah.

Die Vektoreinheiten können allerdings 25 % mehr Threads gleichzeitig verarbeiten und die Registerzuweisung wurde variabler gestaltet. Zudem bieten die Vektoreinheiten auch die Unterstützung für das Datenformat FP8, was vor allem im Hinblick auf die KI-Leistung wichtig ist. Weiterhin vorhanden ist die Unterstützung für FP64 und die grundlegenden Recheneinheiten sind SIMD16 ALUs.

Die XMX-Einheiten der Xe3-Kerne können FP16, BF16 und INT8 mit der gleichen Rechenleistung je Taktzyklus wie die ihrer Vorgänger berechnen. Hinzu kommt nun auch die Unterstützung für INT4 und INT2. Insgesamt soll die KI-Rechenleistung der GPU bei 120 TOPS liegen.

| Panther Lake 4x Xe3 Konfiguration | Panther Lake 12x Xe3 Konfiguration | Lunar Lake 8x Xe2 Konfiguration | |

| Xe-Kerne | 4 (Xe3-Kerne) | 12 (Xe3-Kerne) | 8 (Xe2-Kerne) |

| XMX-Einheiten | 32 | 96 | 64 |

| Raytracing-Einheiten | 4 | 12 | 8 |

| Geometrie-Pipeline | 1 | 2 | 2 |

| Sampler | 4 | 12 | 8 |

| Pixel Backends | 2 | 4 | 4 |

| L2-Cache | 4 MB | 16 MB | 8 MB |

In der kleinen Ausbaustufe bietet die integrierte Xe3-GPU vier Xe3-Kerne und 4 MB an L2-Cache. Diese wird in Intel 3 bei Intel selbst hergestellt.

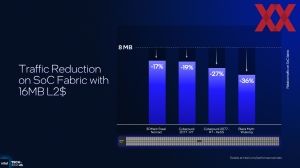

Für die größere Umsetzung mit 12 Xe3-Kernen wählt Intel den L2-Cache mit einer Kapazität von 16 MB und damit dem doppelten Ausbau gegenüber Lunar Lake. Mit dem größere Cache will Intel den Datentransfer zum Hauptspeicher und auch die Belastung des SoC Fabric deutlich reduziert haben. Die größere Xe3-Variante wird in N3E bei TSMC gefertigt. Aus welchen Gründen sich Intel einmal für die hauseigene Fertigung und einmal für eine externe Fertigung entschieden hat, ist nicht bekannt. Kosten, Kapazitäten und Leistungsvorgaben für den Chip könnten eine Rolle gespielt haben.

Mit all den Änderungen an der Xe3-Architektur will Intel die Leistung der integrierten Grafikeinheit im Vergleich zu Lunar Lake um 50 % oder mehr erhöht haben. Bei 12 zwölf Xe3-im Vergleich zu acht Xe2-Kernen ist dies auch das Mindeste, was zu erwarten gewesen ist. Wie viel höher als 50 % das Plus ausfallen wird, ist wohl die spannendere Frage.

Gegenüber Arrow Lake-H und der dort noch verwendeten Xe-Architektur soll Panther Lake ein um 40 % besseres Leistung/Watt-Verhältnis besitzen.

NPU 5 legt den Fokus auf die Effizienz

Mit einer Rechenleistung von 48 TOPS erfüllt die NPU 4 in Lunar Lake bisher als einzige die Mindestanforderungen für Microsofts Copilot+. Wie entscheidend dies nun für den Endkunden am Ende ist, steht sicherlich noch einmal auf einem anderen Blatt, für Intel dürfte es aber wichtig sein, diese Hürde mit mehr und mehr Prozessoren nehmen zu können.

AMDs Ryzen-AI-300-Serie sowie der Qualcomm Snapdragon X Elite nehmen diese Hürde mit 55 bzw. 45 TOPS ebenfalls. Der Snapdragon X2 Elite Extreme von Qualcomm soll im kommenden Jahr sogar mit 80 TOPS über die NPU aufwarten können.

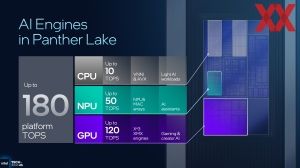

Die NPU 5 in Panther Lake bietet 50 TOPS nur eine geringfügig höhere Rechenleistung, dies ist laut Intel aber nicht der entscheidende Punkt. Für die NPU 5 waren die Auslegung auf die aktuellen KI-Workloads und eine höhere Effizienz des Ziel.

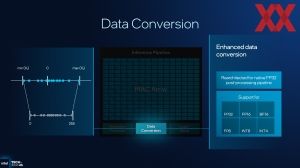

Erreicht wird dies durch die Zusammenlegung von jeweils zwei NCEs (Neural Compute Engines) mit jeweils 2.048 MAC-Arrays der NPU 4 in nun mehr eine NCE bei Panther Lake. Dadurch wird die Größe des MAC-Array verdoppelt, wenngleich es bei insgesamt 12.288 MACs bleibt. Mit der Zusammenlegung einher geht, dass Fixed-Funktion-Blöcke wie die SHAVE DSPs sowie weitere in der Inference Pipeline nicht mehr doppelt vorhanden sind. Ähnlich wie bei der Xe3-GPU geht es auch hier darum effizienter in der Verarbeitung zu werden.

Das MAC-Array der NPU 5 kann INT8/FP8 in einer 16x16x16 Matrix und damit 4.096 MAC-Berechnungen je Taktzyklus ausführen. Mit der NPU 4 waren es mit 2.048 (16x16x8) genau die Hälfte. Auch für FP8-Daten gilt: Das Mac-Array kommt bei 16x16x8 auf 2.028 MAC-Berechnungen je Taktzyklus, während es bei der NPU 4 derer 1.024 (16x16x4) waren. Da die Anzahl der MACs insgesamt aber identisch ist, sind dies auch die Angaben zu den TOPS.

Was Intel mit der NPU 5 für Panther Lake gelingt, ist, dass für die gleiche Rechenleistung 40 % an Chipfläche eingespart werden konnten. Zudem steigt mit der nativen Nutzung von FP8 als Datenformat, welches von der NPU 5 unterstützt wird, das Leistung/W-Verhältnis um mehr als 50 %. Die NPU in Panther Lake wird somit vor allem effizienter und steuert ihren Anteil am gesamtem Compute-Budget für solche Workloads bei.

| Gesamtleistung | NPU | CPU | GPU | |

| Intel Panther Lake | 180 TOPS | 50 TOPS | 10 TOPS | 120 TOPS |

| Intel Lunar Lake | 120 TOPS | 48 TOPS | 5 TOPS | 67 TOPS |

| Intel Meteor Lake | 32,2 TOPS | 10,6 TOPS | 2,82 TOPS | 18,8 TOPS |

| AMD Ryzen AI 300 | - | 50 TOPS | - | - |

| Qualcomm Snapdragon X Elite | - | 45 TOPS | - | - |

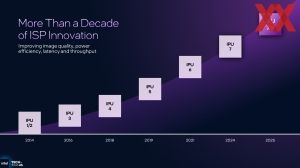

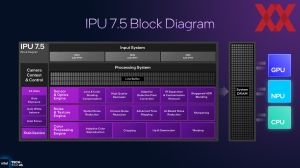

Eine IPU für bessere Kamerabilder

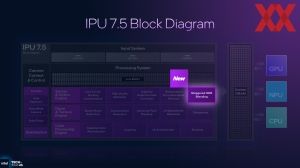

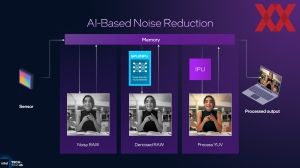

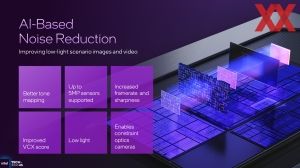

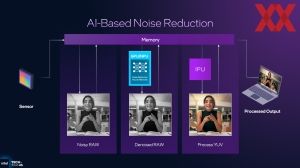

Zusammen mit Panther Lake wird eine neue IPU 7.5 einführen, welche sich vor allem darum kümmert, dass die Bilder der in vielen Notebooks integrierten Kamera verbessert werden. Insgesamte drei Sensoren können mit der neuen IPU angesprochen werden. In dem meisten Fällen wird es aber darum gehen, die Webcam des Notebooks zu verarbeiten. Unterstützt werden Sensoren mit einer Auflösung von bis zu vier Megapixel.

Neben der Bildqualität spielt natürlich auch der Durchsatz in Form der Bitrate und auch die Effizienz eine Rolle. Um die Bildqualität zu verbessern, setzt Intel in der IPU 7.5 unter anderem auf eine doppelte Belichtung des Bildes. Ein über- und ein unterbelichteter Frame werden in der IPU wieder zusammengesetzt und es entsteht ein HDR-Bild. Auch ein Entrauschen in mehreren Zonen des Bildes wird direkt per KI in der IPU ausgeführt, was auch für eine Tonwertkorrektur gilt.

Die IPU 7.5 verfügt über eigenen, internen Buffer. Sollte dieser nicht ausreichen, dann greift die IPU auf den Arbeitsspeicher zurück. Dies ist auch der Vorteil im Vergleich zu diskreten IPUs in Webcams, denn hier ist der Speicher durch den lokalen SRAM begrenzt. Zudem kann die IPU 7.5 auf die Rechenleistung der CPU-Kerne, GPU und NPU zurückgreifen.

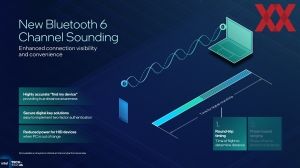

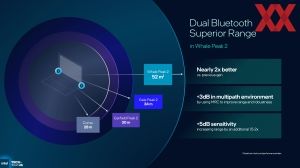

Wi-Fi 7 und Bluetooth 6.0 halten Einzug

Nach allerlei Blick in die Innereien von Panther Lake bietet Intel mit der nächsten Generation auch einige Neuerungen in der Kommunikation mit der Außenwelt.

Einerseits bietet Panther Lake als Plattform bereits die Unterstützung für gleich viermal Thunderbolt 4. Mit einem externen Controller ist Panther Lake auch in der Lage, mit Thunderbolt 5 ausgerüstet zu werden.

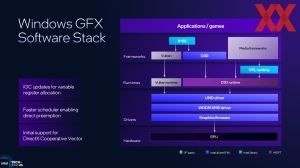

Im Plattform Controller Die befindet sich der MAC für Wi-Fi und Bluetooth. Auf einem Zusatzmodul (BE211 CRF / Intel Killer 1775) sitzen die physikalischen Interfaces. Über BRI, STEP und RGI sind die jeweiligen Interfaces miteinander verbunden.

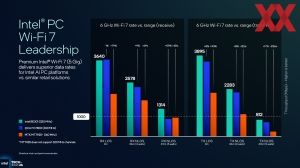

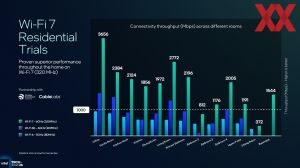

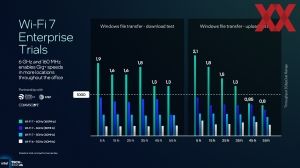

Unterstützt wird damit ein Wi-Fi 7 mit 320 MHz breiten Kanälen, mit denen die höchsten Durchsatzraten erreicht werden sollen. Wi-Fi 7 ist nicht gleich Wi-Fi 7 – so viel haben wir bereits gelernt. Aber selbst gegenüber dem QCAFC7800, der ebenfalls 320 MHz breite Kanäle unterstützt, soll Intels Lösung aber dennoch schneller sein. Auch sämtliche Wi-Fi-7-R2-Funktionen werden von Intels Umsetzung unterstützt.

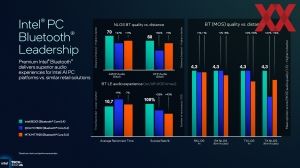

Hinsichtlich des Bluetooth neu eingeführt wird die proprietäre Intel-Lösung Bluetooth Auracast. Auch ein noch nicht in den Markt eingeführtes Bluetooth 6.0 wird bereits unterstützt.

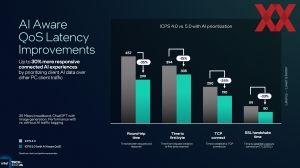

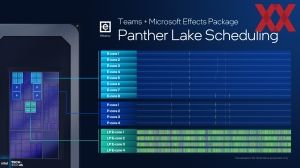

Thread Director und Intelligent Experience Optimizer

Mit dem ersten Hybrid-Design für den Desktop namens Alder Lake führte Intel den Thread Director ein. Der Intel Thread Director ist eine Hardware-Erweiterung im Prozessor, die das Betriebssystem bei der optimalen Zuordnung von Threads auf unterschiedliche Prozessorkerne unterstützt.

Der Thread Director analysiert in Echtzeit Leistungsmetriken wie Instruktionslatenz, Energieverbrauch und Auslastungsmuster einzelner Threads. Basierend auf dieser Analyse vergibt der Thread Director dynamisch Prioritäts- und Affinitäts-Hinweise, welche dem Scheduler des Betriebssystems signalisieren, ob ein Thread besser auf einem Hochleistungskern (P-Kern) oder einem Effizienzkern (E-Kern) ausgeführt werden sollte. Dadurch verbessert sich die Performance eines Workloads und zugleich die Energieeffizienz, indem rechenintensive Threads bevorzugt auf P-Kernen und leichtere Aufgaben auf E-Kernen laufen. Der Thread Director berücksichtigt zudem thermische Bedingungen und passt die Verteilung bei Bedarf an, um Überhitzung zu vermeiden.

An einigen Beispielen zeigte Intel die Nutzung der verschiedenen Kernen in unterschiedlichen Anwendungen auf. So sollen weniger herausfordernde Anwendungen wie Teams auf den LPE-Kernen laufen, was die Akkulaufzeit der Notebooks deutlich erhöht, während Produktivanwendungen mit kurzzeitig hohen Anforderungen kurz auf einen oder mehrere P-Kerne wechseln, die Hintergrundlast aber auf den LPE-Kernen verbleibt.

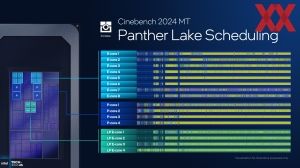

In Multi-Threaded-Anwendungen wie dem Cinebench (der eigentlich auch nur ein Benchmark ist, aber für Rendering-Anwendungen stehen könnte) verteilt der Thread Director die Last natürlich auf alle Kerne, damit der Workload schnellstmöglich abgearbeitet werden kann.

Spiele hingegen sollen primär auf den E-Kernen und im Bedarffall auf den P-Kernen verarbeitet werden. Hier geht es vorranging nicht um die Effizienz und einen möglichst geringen Verbrauch, sondern vielmehr darum, der GPU auch bestmöglich zuarbeiten zu können. Mit der hauptsächlichen Nutzung der E-Kerne ist natürlich aber auch ein möglichst geringer Stromverbrauch durch die CPU vorgesehen.

Im Demo-Bereich konnten wir uns die Thead-Zuteilung am Beipiel eines Office-Setups mit Teams, einem Browser mit Video sowie zweier Office-Anwendungen anschauen. Auf Panther Lake laufen diese auf den vier LPE-Kernen und lasten diese zu etwa 50 % aus. Auf Arrow Lake werden die LPE-Kerne gar nicht verwendet und stattdessen die Last auf den E- und P-Kernen verteilt, wobei hauptsächlich die E-Kerne zum Einsatz kommen. Auch bei Lunar Lake funktioniert die Zuteilung auf den LPE-Kernen recht gut.

Notebook-Besitzer kennen unter Windows den Regler in der Taskleiste, mit Hilfe dessen sie manuell das Leistungsprofil anpassen können. Die Entscheidung fällt zwischen maximaler Batterielaufzeit, Ausbalanciert oder Höchstleistung.

Mit dem Intelligent Experience Optimizer will Intel diese manuelle Auswahl ablösen. Stattdessen soll eine automatische Auswahl des richtigen Profils auf Basis der jeweiligen Last stattfinden. Einerseits erwartet Intel im Bedarfsfall eine um bis zu 19 % höhere Leistung in verschiedenen Anwendungen, da der Intelligent Experience Optimizer das Power-Budget entsprechend zuteilt und freigibt und auf der anderen Seite soll sich auch die Akkulaufzeit verbessern. Wie gut der Intelligent Experience Optimizer dann in der Praxis funktioniert, werden die Tests zeigen müssen.

Panther Lake in drei Chip-Konfigurationen

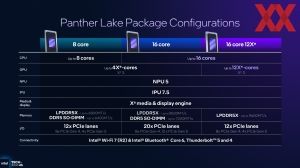

Nach all den Einzelkomponenten kommen wir nun zur konkreten Umsetzung von Panther Lake, auch wenn wir heute noch keinerlei Details wie Produktnamen oder Taktraten erfahren werden. Es wird zwei unterschiedliche Compute-Tile- und GPU-Tile-Konfigurationen geben, aus denen Intel dann drei unterschiedliche Chip-Konfigurationen zusammensetzt, die dann wiederum in konkrete Produkte umgesetzt werden.

Es wird eine 8-Kern-Konfiguration mit vier P- und vier LPE-Kernen geben. Für diesen Chip nimmt Intel eine Verifikation des Speichercontrollers mit LPDDR5X-6800 bzw. DDR5-6400 vor. Der GPU Tile wird hier in seiner kleinsten Ausbaustufe mit 4 Xe3-Kernen eingesetzt. Der Platform Controller Tile bietet insgesamt 12 PCI-Express-Lanes – 8x PCIe 4.0 und 4x PCIe 5.0. Hinzu kommen 4x Thunderbolt 4, 2x USB 3.2 und 8x USB 2.0.

Die zweite Konfiguration sieht den großen Compute Tile mit vier P-, acht E-und vier LPE-Kernen und demnach insgesamt 16 Kernen vor. Mit LPDDR5X-8533 und DDR5-7200 hebt Intel die Speichergeschwindigkeit etwas an. Der Platform Controller Tile kommt in dieser Konfiguration auf insgesamt 20 PCI-Express-Lanes – 8x PCIe 4.0 und 12x PCIe 5.0. Auch hier kommen 4x Thunderbolt 4, 2x USB 3.2 und 8x USB 2.0 hinzu. Der GPU Tile verbleibt bei vier Xe3-Kernen.

In der dritten Konfiguration setzt Intel wieder auf den großen Compute Tile mit insgesamt 16 Kernen, den gleichen Plattform Controller Tile wie in der ersten Konfiguration, hier aber auch die große GPU mit 12 Xe3-Kernen. Mit der großen GPU einher geht der schnellere Speicher, denn hier verifiziert Intel bis LPDDR5X-9600 und geht davon aus, dass die OEMs keinen DDR5 mehr einsetzen wollen.

Die erste Konfiguration mit 4P+4LPE-Kernen kann als Nachfolger von Lunar Lake verstanden werden. Theoretisch ist die Anbindung einer externen GPU möglich. Mit Lunar Lake haben wir dies aber nicht gesehen und so wird dies vermutlich auch hier nicht der Fall sein.

Der größere Plattform Controller Tile der zweiten Konfiguration dient vor allem der Möglichkeit hier eine externe GPU anzubinden. 16 Kerne zusammen mit einer eher schwach konfigurierten GPU dürften das offensichtlichste Anzeichen dafür sein. Bei zwölf PCIe-5.0-Lanes hat Intel bei acht Lanes für die GPU (was typischerweise der Anbindung einer externen GPU im Notebook entspricht) noch vier Lanes für eine schnelle SSD übrig.

Der Schritt zum kleineren Plattform Controller Tile in der Konfiguration mit der großen GPU begründet Intel damit, dass in dieser Konfiguration vermutlich keine Kopplung einer externen GPU vorgesehen ist und damit auch keinerlei zusätzlicher PCI-Express-Lanes notwendig sind.

Notebooks mit Panther Lake ab 2026

Lange wurde vermutet, dass Intel erste Notebooks mit Panther Lake noch Ende 2025 auf den Markt bringen wird. Die offizielle Aussage dazu lautete auf dem ITT wie folgt: Zum Jahreswechsel und damit auf der CES Anfang Januar wird es die ersten Notebooks zusehen geben. Im Verlaufe des ersten Halbjahres wird Intel die verschiedenen Kategorien wie Panther Lake-U und Panther Lake-H dann auf den Markt bringen.

Eine Einschätzung der Leistung ist auf Basis der aktuell vorliegenden Daten schwierig. Stellt man sich Panther Lake aber als Produkt aus Lunar und Arrow Lake vor und nimmt hier vor allem die Stärken der jeweiligen Modelle, dann dürfte Panther Lake für Notebook-Systeme ab 2026 eine sehr gute Lösung werden. Akkulaufzeit, CPU-Leistung, GPU-Leistung und alles drum herum ergeben ein konsistentes Gesamtbild ab.

Hardwareluxx hat die Informationen zu diesem Artikel von Intel durch Einladung des Redakteurs zur Intel Tech Tour US in Phoenix, im Bundesstaat Arizona, erhalten.