Werbung

Auf der diesjährigen Hot-Chips-Konferenz hat Intel einige weitere Details zur kommenden E-Kern-Xeon-Generation Clearwater Forest genannt. Clearwater Forest ist der Nachfolger von Sierra Forest und setzt damit ausschließlich auf die kompakteren und sparsameren Efficiency-Kerne. Zum Einsatz kommen die neuen Darkmont-Kerne, während Sierra Forest noch auf Crestmont setzte.

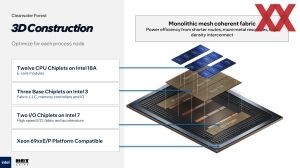

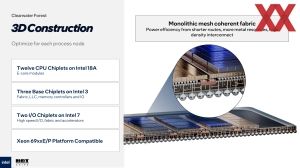

Vor allem soll Clearwater Forest für Intel eine Art Wendepunkt hinsichtlich der Fertigung werden. Erstmals kommt Intel 18A zum Einsatz. Für das Packaging setzt man auf Foveros Direct 3D und so sehen wir, zu was Intel Foundry im Stande ist und womöglich kann dies ein Lichtblick, bzw. ein Ansporn sein, dass auch große externe Kunden auf Intel 18A-P und die nachfolgenden Prozesse setzen.

Zum Namen der Kern-Architektur macht Intel auf der Hot Chips jedoch keinerlei Angaben. Stattdessen gibt es einige Details zur Architektur selbst. So soll das Front-End einen 64 kB großen Instruction Cache bekommen und die Decoder-Einheit kann neun Instruktionen pro Taktzyklus verarbeiten. Dies sollen 50 % mehr Instruktionen als bei Crestmont sein.

In der OoO-Engine (Out of Order) hat Intel die Anzahl der Allocation-Einheiten von sechs auf acht erhöht. Die Anzahl der Reire-Einheiten wird verdoppelt. Das OoO-Window wird um 60 % größer. Ein breites Front-End und eine auf parallele Ausführungen ausgelegte OoO-Engine können allerdings nur funktionieren, wenn auch die Ausführungseinheiten entsprechend breit ausgelegt sind.

Insgesamt 26 Ausführungseinheiten für Integer- und Vektor-Berechnungen stehen zur Verfügung. Damit werden die Darkmont-Kerne in die Lage versetzt, 50 % mehr Operationen durchzuführen. Doppelt so viele Integer- und Vektor-Einheiten gehen mit ebenfalls doppelt so vielen Store-Engines und 50 % mehr Load-Engines einher.

Bis zum Start von Clearwater Forest wird Intel die Details der Darkmont-Kerne sicherlich noch einmal genauer vorstellen. Bis dahin haben wir womöglich auch die Gelegenheit uns ausführlicher mit dem Material zu beschäftigen. Die E-Kerne von Clearwater Forest scheinen aber ein substantielles Update gegenüber den aktuellen Crestmont-Kernen darzustellen und haben damit Potential, die Leistung der Prozessoren deutlich zu erhöhen.

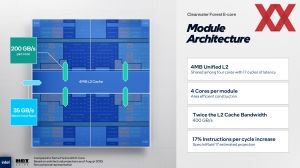

Gestapelte Modul-Architektur

So richtig interessant wird es beim Aufbau von Clearwater Forest. In der größten Ausbaustufe verwendet Intel zwölf Compute-Tiles, die wiederum auf drei Base-Tiles sitzen. Die Compute-Tiles werden in Intel 18A gefertigt, während die Base-Tiles ebenfalls bei Intel in Intel 3 (Intel 3-T) hergestellt werden.

Intel ordnet die E-Kerne wieder in Clustern mit jeweils vier Kernen an. Diesen zur Verfügung stehen 4 MB an L2-Cache. Die Bandbreite zum Cache wird mit 200 GB/s je Kern angegeben. Die Anbindung der Cluster auf dem Chip erfolgt mit 35 GB/s über einen Interconnect Fabric. Bis zu 288 Kerne sollen die Clearwater-Forest-Prozessoren zu bieten haben. Bei zwölf Compute-Tiles bedeutet dies, dass wir hier 96 Kerne je Compute-Tile sehen werden und auf jedem Compute-Tile befinden sich 24 CPU-Cluster.

Zu den zwölf Compute-Tiles und drei Base-Tiles gesellen sich zwei I/O-Tiles, welche das Package oben und unten abschließen. Diese werden ebenfalls bei Intel gefertigt und entstammen dem Intel-7-Prozess. Die I/O-Tiles beherbergen das Routing des Fabric-Interconnects sowie die Controller und PHYs für PCIe/UPI/CXL und die Beschleuniger-Einheiten.

Die DDR5-Speichercontroller von Clearwater Forest sitzen nicht mehr in den Compute-Tiles, sondern den Base-Tiles. Daneben zu finden, ist ein riesiger LLC (Last Level Cache). Die I/O-Tiles und Base-Tiles werden auf dem Interposer mittels EMIB verbunden. Für das Packaging der Compute-Tiles auf den Base-Tiles setzt Intel auf Foveros Direct 3D.

Das Package von Clearwater Forest besteht also aus insgesamt 17 aktiven Chips und so ein wenig fühlen wir uns an Ponte Vecchio erinnert – dieses Mal hoffentlich mit einem besseren Ausgang.

I/O-Funktionen bekannt, aber 1.152 MB an LLC

Die Clearwater-Forest-Prozessoren sind zu den aktuellen Xeon-6-Prozessoren der Xeon 69xxE/P-Serie kompatibel. Das heißt die neuen Prozessoren können in den bestehenden Servern eingesetzt werden. Daher bleibt es auch bei den zwölf Speicherkanälen und 96 PCIe-5.0/64 CXL-Lanes. DDR5-8000 als MRDIMM kann ebenfalls weiterhin verwendet werden, wenngleich Intel offenbar von 8.800 MT/s auf 8.000 MT/s zurückgeht, was die Validierung der Plattform sicherlich vereinfacht.

Außerdem nennt Intel bis zu 576 Kerne für eine 2P-Konfiguration. Dies entspricht den schon erwähnten maximal 288 Kernen je Prozessor. Interessanterweise erwähnt Intel aber auch 1.152 MB an LLC, so dass wir davon ausgehen können, dass sich in den drei Base-Tiles zusammengenommen 576 MB an Cache befinden – 192 MB je Base-Tile.

Ein derart großer Cache ist auf den ersten Blick ein Novum, sieht man von den Xeon-Max-Prozessoren ab, die auf Basis von Sapphire Rapids mit 64 GB an HBM2e bestückt wurden. Ein Kassenschlager wurden diese Prozessoren aber offenbar nicht, denn einen Nachfolger gab es nicht. Wir sprechen hier von einem Novum, denn selbst die Xeon-6-Prozessoren hatten bis zu 504 MB an L3-Cache. Der von Intel als LLC bezeichnete Cache kann als solchen bezeichnet werden, denn die Compute-Tiles verfügen nur über L2-Cache.

Wann genau die Clearwater-Prozessoren auf den Markt kommen werden, ist nicht bekannt. Wir rechnen in diesem Herbst noch mit einer Vorstellung. Offiziell am Markt starten wird Clearwater Forest aber erst im ersten Halbjahr 2026.

Im Text werden allerlei Codenamen genannt. Eine Übersicht aller Codenamen, Zeiträume und geplanten Fertigungsschritte für die zukünftigen Prozessoren von AMD und Intel bekommt ihr hier.