Werbung

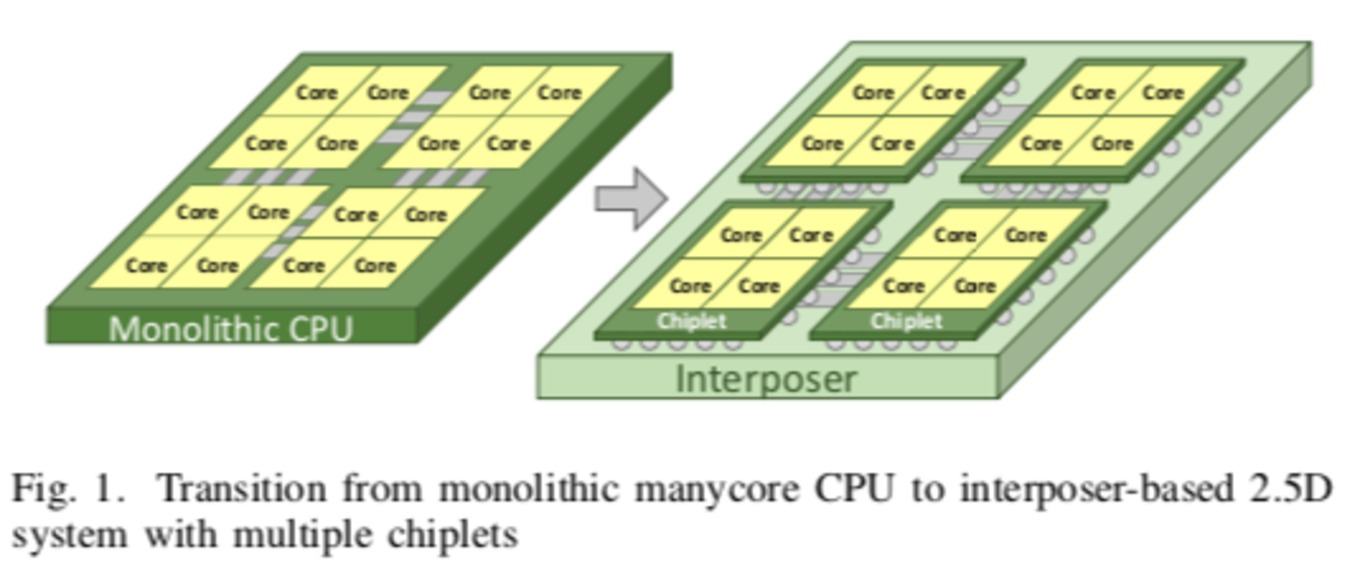

Große monolithische Chips sind aufgrund der komplizierten Fertigung zunehmend ein Problem für die Hersteller. AMD hat seine Zen-Architektur auf einzelne Zeppelin-Dies ausgelegt, die einfach mehrfach verwendet werden können - ein Die für die Ryzen-Prozessoren, zwei und bald vier aktive Dies für Ryzen Threadripper und vier Dies für die EPYC-Prozessoren.

Intel hat mit der Embedded Multi-die Interconnect Bridge (EMIB) eine Technik in der Fertigung von Chips entwickelt, bei der sich mehrere Dies unterschiedlicher Fertigung und Anbindung miteinander kombinieren lassen. Zum Einsatz kommt diese unter anderem bei den Stratix-FPGAs und auch den Core-Prozessoren mit Radeon-RX-Vega-M-Grafik.

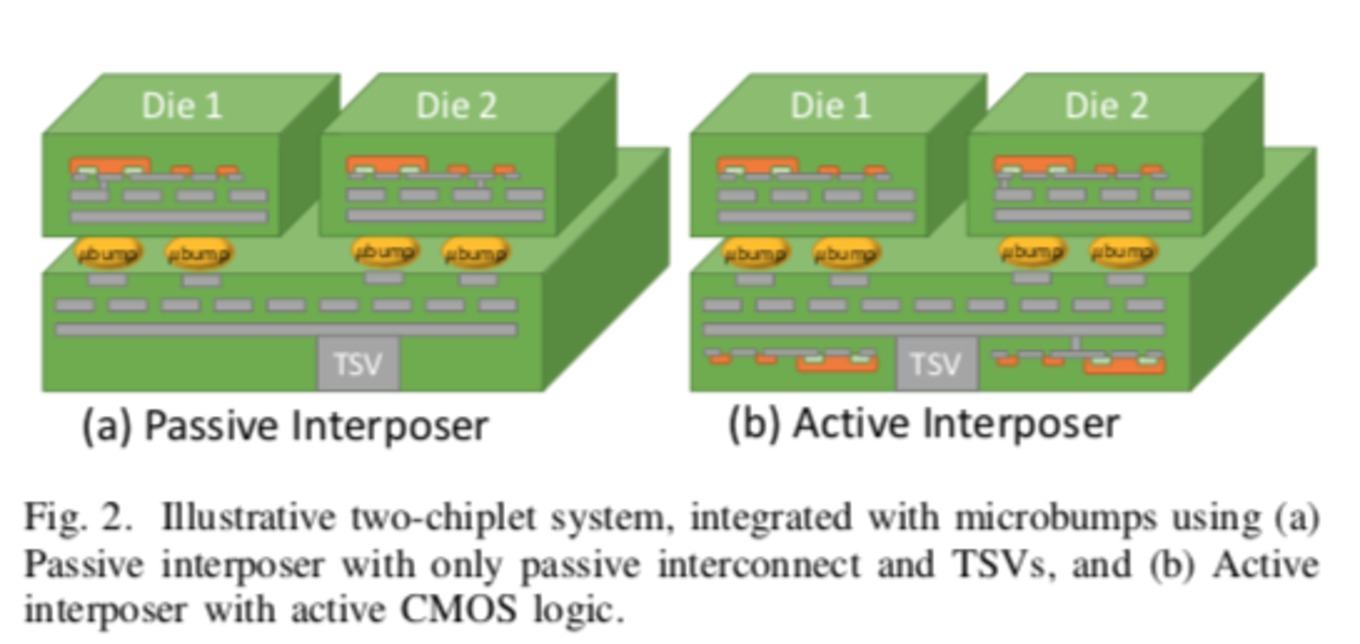

Mit der Fiji-GPU (AMD Radeon R9 Fury X) setzte AMD erstmals auf einen Interposer. Dabei handelt es sich um ein Halbleitermaterial, durch das die Verbindungen zwischen GPU und damals High Bandwidth der ersten Generation hergestellt wurden. Wie ein Interposer funktioniert, haben wir vor einiger Zeit ausführlich beschrieben. Ein Interposer ist ein passives Bauteil, dennoch recht komplex zu fertigen, da die Ausbeute für solch große Bauteile ein entscheidender Kostenfaktor ist und der Interposer für Fiji- und auch Vega-GPU recht groß ist – und dementsprechend teuer.

AMD arbeitet an aktivem Interposer

Doch offenbar arbeitet AMD an einer Technologie für einen aktiven Interposer. AMDs Ambitionen im Multi-Chip-Module (MCM) oder Multi-Chip-Design für Prozessoren und auch GPUs dürfte offensichtlich sein. Auch NVIDIA forscht offenbar an GPUs bestehend aus mehreren Dies. Für AMD wird eine solche Lösung im Rahmen der nächsten GPU-Generation Navi derzeit diskutiert und wir haben uns diesen Ansatz bereits genauer angeschaut.

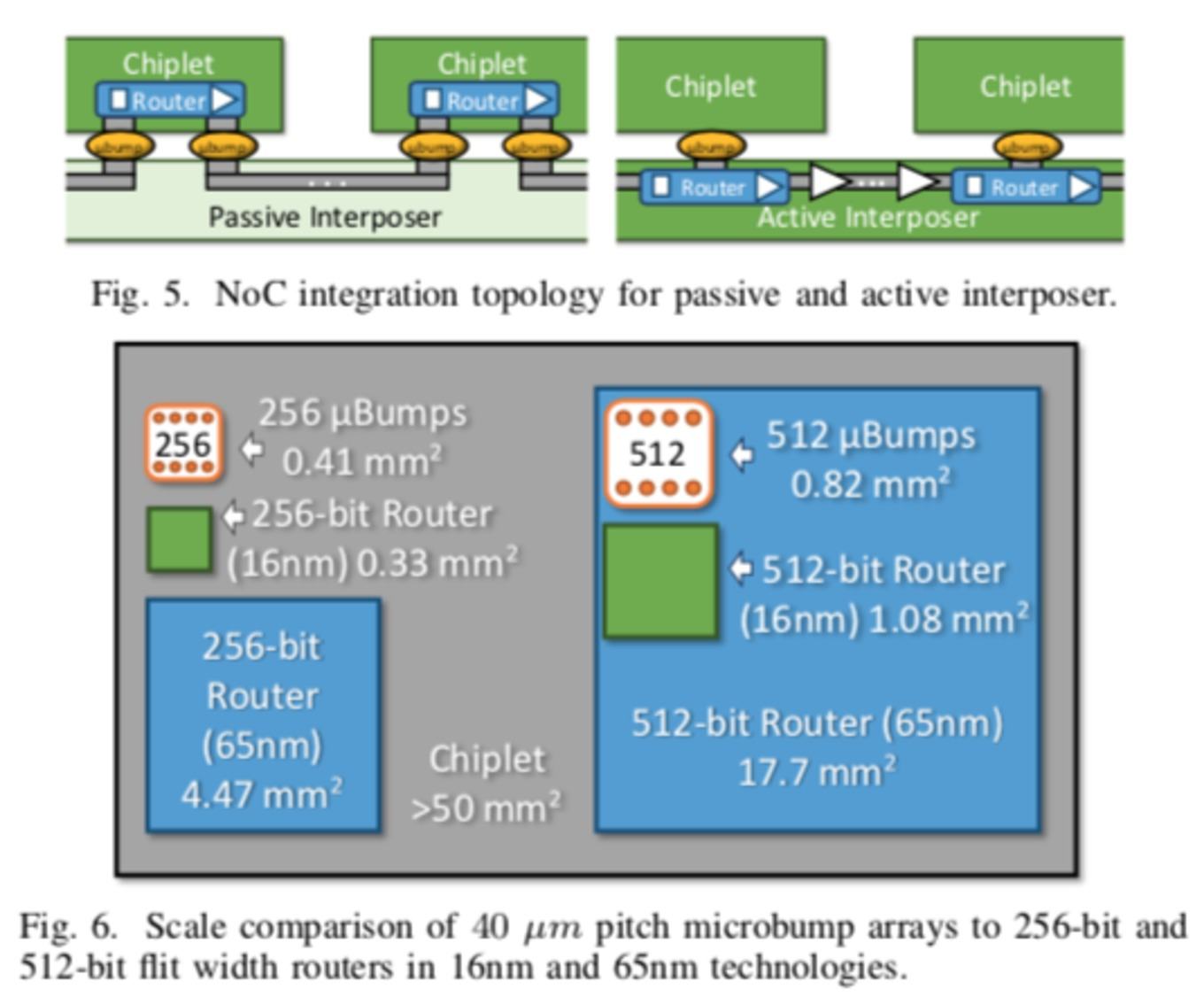

Das Papier mit dem Namen „Cost-Effective Design of Scalable High-Performance Systems Using Active and Passive Interposers" (PDF) beschäftigt sich mit den Vorteilen eines aktiven Interposers, der nicht mehr nur Stumpf Signale von A nach B leiten kann, sondern der auch aktive Elemente wie Network-on-Chip (NoC) enthalten kann. Ein solches NoC ermöglicht eine effizientere Signalweitergabe und verringert die Latenzen. Die EMIB-Technologie von Intel kann auch als aktiver Interposer bezeichnet werden, denn EMIB ermöglicht in Teilen das, was AMD für einen aktiven Interposer vorsieht. Doch ein aktiver Interposer hat auch Nachteile und das wären vor allem die Kosten, bzw. die Ausbeute bei der Fertigung.

Der Unterschied zwischen einem passive und aktiven Interposer ist recht einfach festzuhalten. In einem aktiven Interposer werden Punkt-zu-Punkt-Verbindungen zu jedem einzelnen Chiplet gemacht, die miteinander kommunizieren sollen. Soll eine potenzielle GPU mit zwei Dies mit vier HBM2-Speicherchips kommunizieren, müssen bei einem gemeinsamen Speicherzugriff für jede GPU viermal 1.024 Verbindungen für das Speicherinterface hergestellt werden.

Ein aktiver Interposer verwendet sogenannte Router. Für die GPU aus zwei Dies mit vier HBM2-Speicherchips bedeutet dies: Jeder der HBM2-Speicherchips und die beiden GPUs verbinden in den Interposer, wo dann eine Komponente des NoC die Datenverbindungen entsprechend routet. Repeater in den Verbindungen können die Signale aufbereiten, was bei langen Verbindungen in einem passiven Interposer durch Electrostatic Discharge (ESD) zu einem Problem werden kann. Die Bitrate sinkt mit zunehmender Länge der Verbindung – der aktive Interposer kann hier entgegenwirken.

Ein großes Problem des aktiven Interposer ist die Ausbeute in der Fertigung. Während bei einem passiven Interposer defekte Bereiche schon recht häufig vorkommen, diese aber umgangen werden können, ist die Fehlertoleranz für einen aktiven Interposer noch einmal geringer. Sind die aktiven Elemente durch einen Fertigungsfehler betroffen, können diese nicht einfach umgangen werden. Das Problem soll hier durch eine Redundanz umgangen werden. Man fertigt also größere Router im Interposer und versieht den Bus mit zusätzlichen Verbindungen, damit bei einem Ausfall einzelner Verbindungen in der Anbindung der Chips einfach die redundanten Verbindungen verwendet werden können.

Aktive Interposer können die Latenzen von Datenverbindungen signifikant reduzieren und die Bandbreite erhöhen. Allerdings ist dies mit höheren Kosten verbunden. Durch das Multi-Chip-Design der Prozessoren konnte AMD die Ausbeute unter Verwendung des Zeppelin-Dies deutlich erhöhen, da einfach je nach Funktionsgrad des Zeppelin-Dies dieser auf dem jeweiligen Prozessor eingesetzt wird.

Zukünftige Chip-Designs könnten aber durchaus eine aktiven Interposer vorsehen, wenn das Verhältnis zwischen Leistungsgewinn und der höheren Kosten denn stimmt und für sinnvoll erachtet wird.