Werbung

ARM, Qualcomm, Intel und Fujitsu haben bereits angekündigt, dass sie NVIDIAs NVLink Fusion für zukünftige CPU-Designs nutzen werden. Nun verkündet auch SiFive, dass man am entsprechenden Programm teilnehmen wird. Damit sind auch alle drei wichtigen CPU-Architekturen vertreten: x86, ARM und nun eben RISC-V.

Bei SiFive hat man keinerlei konkrete Ankündigung, welches CPU-Design für die Integration von NVLink vorgesehen ist. Aber derart konkret ist bisher noch kein Hersteller geworden. Allenfalls bei Fujitsu hat man sich für Monaka-X bereits etwas konkreter darauf festgelegt. Bei Intel wird es ein zukünftiger Xeon-Prozessor sein, bei ARM kommen zusammen mit dem Monaka-X gleich mehrere Designs in Betracht.

SiFive bietet bereits einige CPU-Designs für Rechenzentren an. Dazu gehört die P870-D-Serie. Bis zu 64 CPU-Kerne auf Basis einer 64-Bit breiten RISV-V-ISA können hier zusammenarbeiten. In einigen Randbereichen stellt das quelloffene RISC-V-Design eine Alternative dar, ob man aber jemals eine echte Konkurrenz zu x86 und ARM werden könnte, bleibt abzuwarten.

Noch einmal zurück zu NVLink Fusion. Eine zentrale Voraussetzung für den Einsatz von NVLink Fusion lautet: Entweder werden KI-Beschleuniger eines anderen Anbieters an eine NVIDIA-CPU angebunden oder eine kundenspezifische CPU wird mit KI-Beschleunigern von NVIDIA kombiniert.

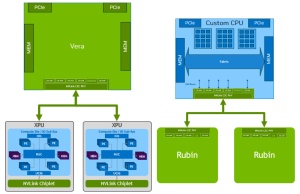

Die praktische Umsetzung von NVLink Fusion sieht dabei wie folgt aus: Sollen eigene KI-Beschleuniger mit einer NVIDIA-CPU gekoppelt werden, nutzt NVIDIA die Universal Chiplet Interconnect Express (UCIe) IP samt passendem Interface. Die Vera-CPU verfügt bereits über ein NVLink-C2C-Interface. Dieses wird mit einem NVLink-Chiplet verbunden, das wiederum gemeinsam mit dem KI-Beschleuniger auf einem Package integriert ist.

Kommt hingegen eine kundenspezifische CPU mit einem KI-Beschleuniger von NVIDIA zum Einsatz, wird im CPU-Design die NVLink-C2C-IP implementiert. Diese bildet das physikalische Interface zwischen CPU und KI-Beschleuniger. Ein separates NVLink-Chiplet wie im ersten Szenario ist hier nicht erforderlich.