Werbung

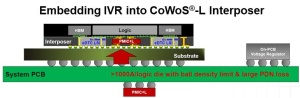

In einem LinkedIn-Beitrag verweist Igor Elkanovich vom taiwanesischen ASIC-Hersteller GUC (Global Unichip Corporation) auf die Möglichkeit, sogenannte IVRs (Integrated Voltage Regulator) in TSMCs CoWoS-L-Interposer zu integrieren und damit die Leistungsdichte deutlich zu steigern. Daneben verweisen die Kollegen von ComputerBase noch auf einen Vortrag von Intels Fellow Kaladhar Radhakrishnan auf dem ISSCC 2026 im Februar des kommenden Jahres. Dieser soll einen Vortrag halten, der mit "Integrated Voltage Regulator Solutions to Enable 5kW GPUs" überschrieben ist und in dem wohl erläutert werden soll, wie zukünftige GPUs mit bis zu 5 kW versorgt werden sollen.

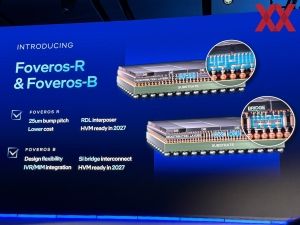

Ein Integrated Voltage Regulator ist eine auf dem Chip integrierte Schaltung, die die Stromversorgungsspannung lokal reguliert und stabilisiert, um Spannungsschwankungen auszugleichen und eine konstante Betriebsspannung für die Prozessorelemente bereitzustellen. Dies verbessert die Energieeffizienz, reduziert Spannungsabfälle (IR-Drop) und ermöglicht höhere Taktraten, da die Spannung präzise auf jeden Kernbereich abgestimmt werden kann. Intel bringt IVRs bereits zum Einsatz. Mit Foveros-B sollen IVRs ab 2027 direkt im Package angeboten werden können.

Vor allem die KI-Beschleuniger kommen schon heute auf eine Leistungsaufnahme im Bereich von 1.000 W und darüber. Schon im kommenden Jahr soll dies auf 2.000 W und mehr für ein Package gesteigert werden. Die Herausforderungen bestehen dabei aber nicht nur in der Kühlung, sondern auch in der Versorgung des Chips. Bei 1.000 W Leistungsaufnahme müssen bei einer Betriebsspannung von 1 V genau 1.000 A an Stromstärke durch den Interposer an die Chips geführt werden. Sprechen wir nun über 2.000 W, sind es bei 1 V entsprechend 2.000 A.

TSMCs Integration eines IVR im CoWoS-L-Interposer war auch auf dem Open Innovation Platform Ecosystem Forum in dieser Woche ein Thema. IVRs können auf MIM-Transistoren (Metal Insulator Metal) oder eDTC-Transistoren (Embedded Deep Trench Capacitor) basieren und sollen die stabile Versorgung zukünftiger Chips gewährleisten können. GUCs Ansatz der IVRs unterstützte sowohl den MIM- wie auch den DTC-Ansatz.

DTCs sind vertikal arrangierte Halbleiterbauelemente, die zur Kapazitätserweiterung eingesetzt werden. Ein Vorteil der DTCs gegenüber Kondensatoren, die sich auf dem Package (bzw. dessen Rückseite) befinden ist, dass sie frei und so nah wie möglich an der gewünschten Schaltung (dem eigentlichen Chip) platziert werden können. Zudem bieten DTCs eine höhere Kapazität pro Fläche als andere Lösungen, wie Metal-Insulator-Metal-Kondensatoren (MIM).

Eine weitere Ebene in der Versorgung der Chips sind die UHPMIM- (Ultra High Performance Metal Insulator Metal), SHDMIM- (Super High Performance Metal Insulator Metal) und SHDMIM-Kondensatoren (Super High Density Metal Insulator Metal), die im CoWoS-L-Package sowie dem Base- und Top-Die in einem SoIC-Stapel integriert werden können.

Allerdings ist die Platzierung der eDTCs nicht ganz einfach. Zudem gibt es definierte Regeln, die im Design des eDTC selbst eingehalten werden müssen: So gibt es Discharge Rules, Placement Rules, Max Stack Length Rules, TSV Spacing Rules und vieles mehr. Substrate sind inzwischen eine aktive Komponente im Package-Design.