Werbung

Neben der generellen Ausrichtung des Foundry-Geschäfts und den Details zu Intel 18A-P, Intel 18A-PT und ersten Informationen zu Intel 14A ist das (Advanced) Packaging das zweite Standbein für Intel. Auf der Direct-Connect-Konferenz gab es die Ankündigung zu einer neue EMIB- und zwei neuen Foveros-Varianten. Dass das Packaging für die Foundry-Sparte von enormer Bedeutung ist, ließ Intel erst vor wenigen Wochen erneut verlauten. Insofern sollen die Fertigung und das Advanced Packaging Hand in Hand arbeiten.

EMIB-T für HBM4

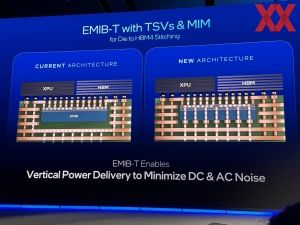

EMIB ist als eine Art Silizium-Brücke ein wichtiger Bestandteil der Chiplet-Strategie von Intel. Zum Einsatz kommt EMIB vor allem bei den Xeon-Prozessoren, wo mehrere Compute-Tiles und auch HBM-Speicher miteinander verbunden werden. EMIB-T ist eine spezielle Variante die um Through Silicon Vias (TSVs) ergänzt wird, was Vorteile in der Versorgung der Chips haben soll.

Konkret spricht Intel bei EMIB-T über die Anbindung von HBM4 und UCIe-Chiplets. Mit einer aktuellen EMIB-Brücke können die Signalintegrität und Spannungsdrops zu Problemen führen. EMIB-T enthält MIM-Kondensatoren und kann diese Spannungsdrops somit ausgleichen.

EMIB wird in den kommenden Jahren zunehmend wichtig bleiben – nicht nur in der EMIB-T-Variante. Aktuell kommt EMIB auf einen Bump Pitch von 45 µm und eine Dichte von 772 Bumps/mm². EMIB-T wird den Bump Pitch auf unter 45 µm reduzieren können, womit auch die Bump-Dichte ansteigen wird. In der notwendigen Leistungsaufnahme von 0,25 pJ/Bit wird sich bei EMIB aber zunächst wenig tun.

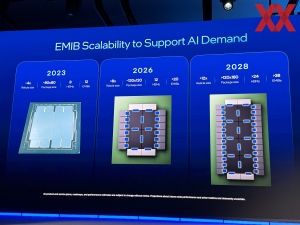

Ab 2026 sollen die Packages mit EMIB die achtfache Reticle-Größe erreichen können und das gesamte Package kann 120 x 120 mm groß werden. Zusammen mit der entsprechenden Anzahl an Compute-Chiplets können bis zu 12 HBM-Chips über mehr als 20 EMIBs miteinander verbunden werden.

Zwei Jahre später schon soll EMIB dann Packages mit der mehr als zwölffachen Reticle-Größe erreichen können. Das gesamte Package kann dann 120 x 180 mm groß sein und mehr als 24 HBM-Chips sowie theoretisch acht Compute-Chiplets enthalten. Mehr als 38 EMIBs können sich dann im Substrat befinden. Das was Intel hier aufzeichnet, ähnelt den Plänen von TSMC, wo CoWoS in den kommenden Jahren ebenfalls solch riesige Packages möglich machen soll.

Foveros-R und Foveros-B

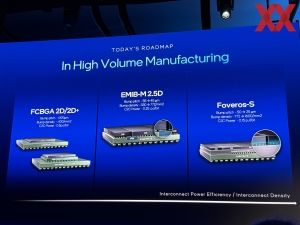

Hier kommen dann Foveros-R und Foveros-B ins Spiel- Foveros ist in seiner aktuellen Variante Foveros-S mit einem Bump Pitch von weniger als 25 µm, einer Dichte von 1.600 Bumps/mm² und einer Übertragungseffizienz von 0,15 pJ/Bit vor allem für Anwendungen interessant, wo Effizienz und Packdichte wichtig sind. Die Chiplet-Versionen der Core-Prozessoren ab Meteor Lake sind hier die prominentesten Beispiele.

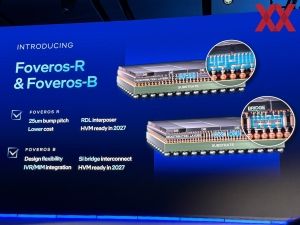

Foveros-R soll die Interconnect-Technologie bei geringeren Kosten möglich machen. Dazu verwendet Intel hier unter anderem einen RDL Interposer. Ein RDL Interposer ist ein Zwischenträger, der sogenannte Redistribution Layers (RDLs) nutzt, um die elektrische Verbindungen zwischen den Chips herzustellen. Der RDL Interposer ermöglicht eine hohe I/O-Dichte und kompakte Signalführung, besonders in fortschrittlichen Chiplet- oder 2.5D-Packaging-Technologien. Foveros-R soll ab 2027 in die Massenproduktion gehen.

Foveros-B hingegen verwendet eine Art Brücke – wie bei EMIB. In die Schichten können aber auch spannungsversorgende Komponenten oder MIMs zur Spannungsstabilisierung eingebettet werden. Bei Foveros-B handelt es sich um ein aufwändigeres Verfahren, welches aber auch fortschrittliche Packages ermöglichen soll. Auch Foveros-B soll ab 2027 in die Massenproduktion gehen.

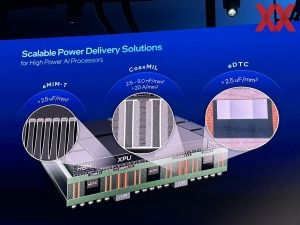

eMIM-T und CoaxMIL als integrierte Kondensatoren sowie eDTC (Deep Tranche Capacitor) werden in diesem Zusammenhang auch immer wichtiger bzw. weiterentwickelt. Ohne solche lokalen Puffer in der Spannungsversorgung könnten die großen und leistungshungrigen KI-Chips beispielsweise nicht die aktuell gebotene Leistung erreichen.

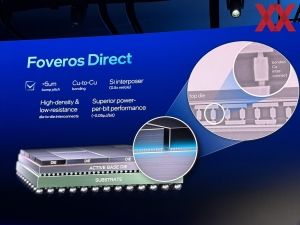

Bereits seit Jahren in der Entwicklung befindet sich Foveros Direkt als Hybrid-Bonding-Technologie mit direkten Kupfer-zu-Kupfer-Verbindungen. Die Kontakte werden verdichtet, die Übertragungseffizienz steigt auf 0,05 pJ/Bit.