Werbung

Bereits zur Computex in diesem Jahr kündigte NVIDIA (erneut) an, die eigene Interconnect-Technologie NVLink anderen Chipherstellern zur Verfügung zu stellen. Auf der Hot-Chips-Konferenz in diesem Jahr will NVIDIA einige technische Details verraten und hat in einem Vorab-Briefing bereits einen kleinen Einblick gegeben.

NVIDIA verbindet seine eigenen CPUs und GPUs über den NVLink-Interconnect, der in der aktuell für die Blackwell-GPUs verwendeten fünften Generation auf 50 GB/s pro NVLink-Lane kommt und somit bei 18 insgesamt vorhandenen NVLink-Lanes in der Umsetzung bidirektional 1.800 GB/s erreicht. In den GB200/GB300-NVL72-Systemen sind 72 GPUs untereinander und direkt mittels NVLink miteinander verbunden. Auf diese Art und Weise erreicht es NVIDIA, dass diese 72 GPUs wie ein großer Beschleuniger zusammenarbeiten, da die hohe Bandbreite und geringen Latenzen einen gegenseitigen Datenaustausch ohne Hindernisse ermöglichen.

Schon im März 2022 verkündete NVIDIA, dass NVLink-2C2-Interconnect auch von externen Chipherstellern verwendet werden kann. Bislang aber kam es nicht dazu und NVIDIA verwendet NVLink-2C2 ausschließlich selbst.

Eine der Voraussetzungen für den Einsatz von NVLink Fusion: Es können entweder andere KI-Beschleuniger an eine NVIDIA-CPU angebunden werden oder aber eine Custom-CPU wird an KI-Beschleuniger von NVIDIA angebunden. Erst heute haben das japanische RIKEN und NVIDIA gemeinsam verkündet, dass für den Supercomputer FugakuNEXT die Monaka-X-Prozessoren mit NVIDIA-GPUs verwendet werden. Hier kommt NVLink Fusion dann zum Einsatz.

NVIDIA behält hier also eine gewisse Kontrolle und öffnet NVLink nicht in dem Maße, dass beispielsweise AMD dies zwischen seinen Prozessoren und Beschleunigern nutzen könnte. Eine der beiden zentralen Komponenten muss immer von NVIDIA kommen.

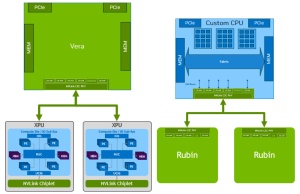

Konkret umgesetzt wird NVLink Fusion wie folgt: Sollen Custom-KI-Beschleuniger mit einer NVIDIA-CPU verbunden werden, setzt NVIDIA auf die Universal Chiplet Interconnect Express (UCIe) IP und ein dazugehöriges Interface. Die Vera-CPU hat bereits ein Interface für NVLink-C2C. Dieses wird mit einem NVLink-Chiplet verbunden, welches wieder mit dem KI-Beschleuniger auf einem Package sitzt.

Für den Fall des Einsatzes einer Custom-CPU mit einem KI-Beschleuniger von NVIDIA, wird im CPU-Design die NVLink-C2C-IP verwendet. Diese stellt das physikalische Interface zwischen CPU und KI-Beschleuniger. Ein NVLink-Chiplet wie im ersten Fall ist nicht notwendig.

Da NVIDIA als Beispiel die Vera-CPU und die Rubin-GPU nimmt, ist davon auszugehen, dass wir frühestens mit dieser Generation im kommenden Jahr auch erste konkrete Umsetzungen von NVLink Fusion sehen werden.

Aus Spine wird eine Midplane

Aktuell setzt NVIDIA für die NVLink-Verbindungen der GB200/GB300-NVL72-Systeme auf einen komplexen Spine (übersetzt Rückgrat) im Rack, der die 72 GPUs allesamt direkt miteinander verbindet. 2.556 Einzelverbindungen aus koaxialen Kupferdrähten sind hier vorhanden.

Mit Rubin Ultra NVL576 wird NVIDIA auf NVLink der siebten Generation wechseln. Hier ändert sich die Zählweise der Racksysteme. Die Kyper getauften Racks werden 576 Rubin-Ultra-GPUs in 144 Packages fassen. Die Bandbreite der einzelnen NVLink-Lanes wird steigen, aber es werden auch doppelt so viele Einzelverbindungen notwendig sein.

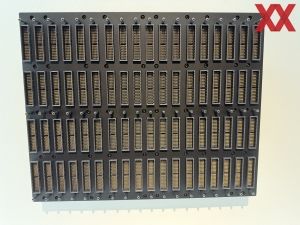

Aus diesem Grund wird NVIDIA mit Rubin Ultra und dem Kyper-Rack vom aktuell (und auch für Blackwell Ultra und Rubin) verwendeten Spine-Design auf eine Midplane wechseln. Auch diese wird Kupferverbindungen verwenden und über 72 Anschlüsse verfügen. Jeder dieser Anschlüsse hat 152 Pins, so dass die gesamte Midplane auf 10.944 Pins kommt. Das PCB dieser Midplane besteht aus 72 Lagen, um alle Pins und Anschlüsse innerhalb dieser Lagen miteinander zu verbinden.

Auf der Computex konnten wir uns bereits einen Eindruck der Komplexität machen.