Werbung

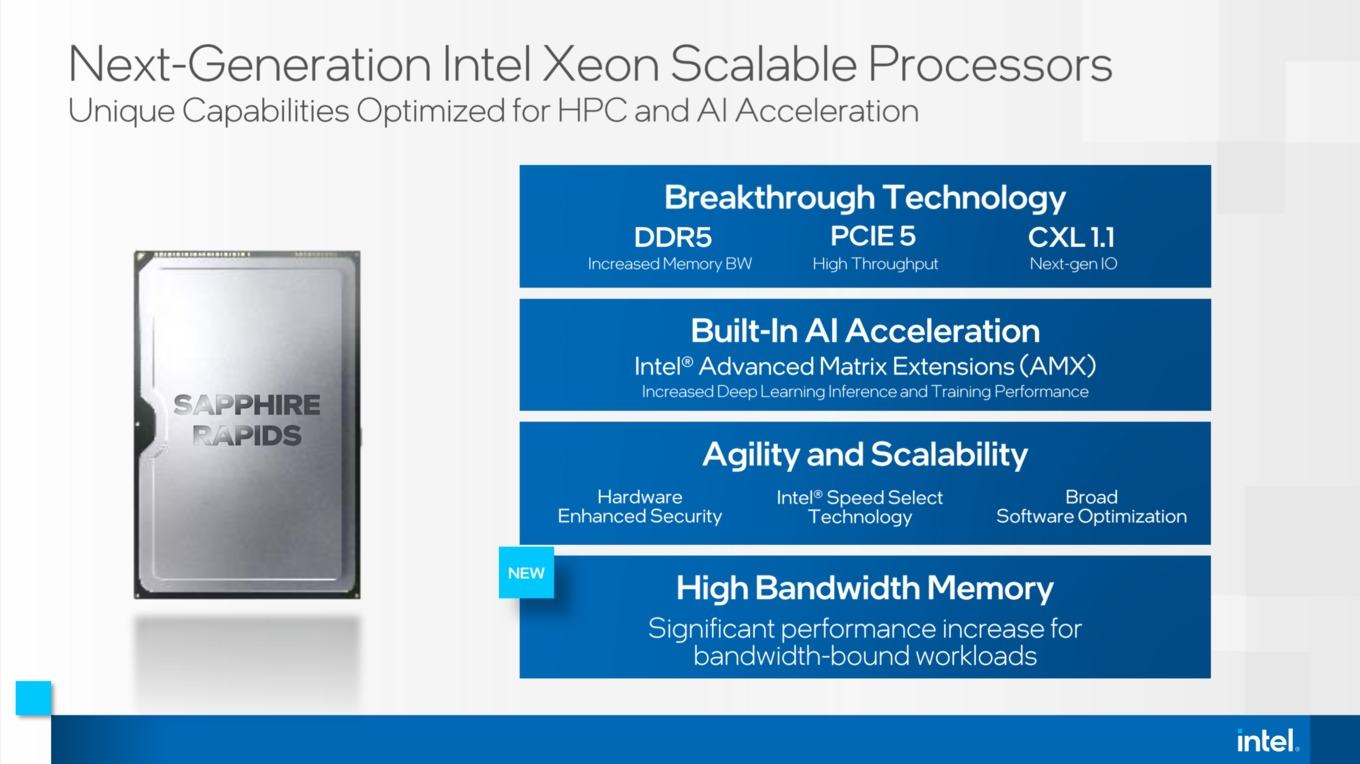

Auf der ISC High Performance gibt Intel weitere Details zu den zukünftigen HPC-Hardware-Lösungen bekannt. So bestätigt Intel unter anderem, dass die vierte Generation der Xeon-Prozessoren ebenfalls mit High Bandwidth Memory bestückt werden wird. Genauer gesagt wird es Modelle geben, die HBM verwenden werden und solche, bei denen dies nicht der Fall sein wird. Intel dürfte damit auf den Trend zu immer größeren Caches reagieren, den AMD angestoßen hat. In den letzten beiden EPYC-Generationen bietet man hier bereits bis zu 256 MB L3-Cache, mit dem 3D V-Cache kommen bei den EPYC-Prozessoren im aktuellen Design theoretisch weitere 2.048 MB an schnellem Cache hinzu.

Allerdings spricht Intel noch nicht über die technischen Details. So ist weder bekannt, wie viel HBM verbaut sein wird, noch ob es sich um HBM2 oder HBM2E handelt. Ganz allgemein spricht Intel nur von einer höheren Bandbreite und der damit verbundenen höheren Leistung für Anwendungen, die von den Speicheranbindung und der Menge eines schnellen Speichers abhängig sind. Kapazität und Datenraten hängen natürlich davon ab, wie viele HBM2(E)-Chips Intel mit Sapphire Rapids wird aufbieten können. So kommt ein einzelner HBM2E auf bis zu 16 GB bei einer Speicherbandbreite von bis zu 460 GB/s. Eine NVIDIA A100-GPU bringt es mit fünf HBM2E-Chips auf 80 GB und 2.039 GB/s.

Theoretisch ist ein solcher Xeon-Prozessor mit HBM in der Lage ohne weiteren Arbeitsspeicher zu arbeiten. Aber Intel wird erst zu einem späteren Zeitpunkt über die Details von Sapphire Rapids sprechen.

Einen Blick auf einen Prozessor konnten wir schon werfen und daher wissen wir auch, dass Intel hier vier Tiles mit jeweils maximal 15 Kernen einsetzt. Golden-Cove-Kerne, die Unterstützung für DDR5 und PCI-Express 5.0, die Einführung der Maxtrix-Befehlssatzerweiterungen (AMX) und vieles mehr steht für Sapphire Rapids auf der Liste. Ende 2021 sollen die Prozessoren bereits vorgestellt werden.

Ponte Vecchio kommt in mehreren Formfaktoren

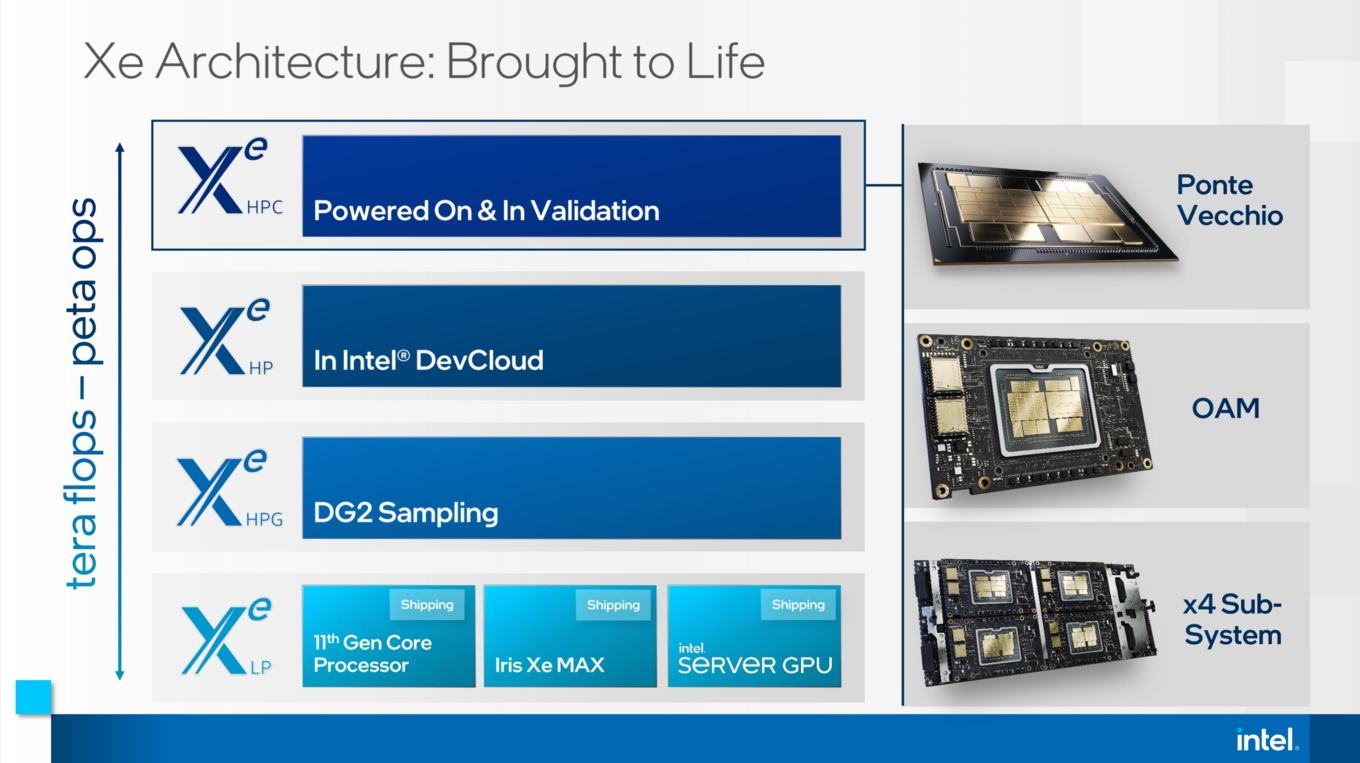

Ein paar kleinere Neuigkeiten gibt es auch im Bereich der GPU-Beschleuniger. Hier ist bereits bekannt, dass sich Ponte Vecchio auf Basis der Xe-HPC-Architektur aktuell in der Validierungsphase befindet. Bereits Ende 2021 sollen die ersten GPU-Beschleuniger für den Supercomputer-Einsatz ausgeliefert werden. 47 aktive Tiles und alles was Intel derzeit an Packaging-Technologien aufzubieten hat, stecken in Ponte Vecchio.

Darüber hinaus zeigt Intel Ponte Vecchio erstmals in einem Open Accelerator Module (OAM). Für den Aurora-Supercomputer liefert Intel die Ponte Vecchio GPU-Beschleuniger, als auch die oben erwähnten Xeon-Prozessoren Sapphire Rapids. Je vier Ponte-Vecchio-Chips sind an einen Xeon-Prozessor als Host angebunden. Eine ähnliche Konfiguration zeigt Intel als x4 Subsystem.

Auch zu weiteren Xe-Produkten hat sich Intel abermals geäußert. Die Xe-HP GPU-Beschleuniger können über Intels DevCloud bereits getestet werden, warten aber noch auf den offiziellen Startschuss und der Gaming-Ableger Xe-HPG soll inzwischen in Form von Samples für Partner zur Verfügung stehen. Auch für diese beiden Produktgruppen steht der Startschuss in diesem Jahr im Raum.

Update: Verfügbarkeit ab Anfang 2022

In einem Blogpost hat Lisa Spelman zumindest noch einen groben Zeitrahmen für die Verfügbarkeit der nächsten Xeon-Generation genannt:

"Based on this, we now expect Sapphire Rapids to be in production in the first quarter of 2022, with ramp beginning in the second quarter of 2022."

Demnach wird die Produktion im ersten Quartal 2022 anlaufen und im weiten Quartal vorangetrieben. Zur HotChips Mitte August will Intel weitere Details verraten. Ursprünglich waren die Sappire-Rapids-Prozessoren für 2021 geplant.

Laut Spelman können durch die Advanced Matrix Extensions (AMX) bestimmte Anwendungen bis zu doppelt so schnell berechnet werden. Davon profitieren soll vor allem das Training und Inferencing von AI-Daten. Eine Technik namens Data Streaming Accelerator (DSA) wird Intels QuickData Technology ablösen und ist Bestandteil der I/O Acceleration Technology. DSA soll durch einen effizienteren Transfer der Daten im Interconnect für eine bessere Ausnutzung der zur Verfügung stehenden Ressourcen sorgen. Diese stehen dann der eigentlichen Anwendung zur Verfügung.