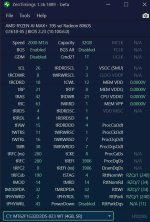

Aber VORSICHT mit dem neuen BIOS hier wird tRFC2 und tRFCsb verwendet wenn ihr die Werte zu niedrig einstellt wird euer PC nicht booten,

Ich spreche aus erfahrung

ROG CROSSHAIR X870E EXTREME TEST BIOS 9921 based on 1901

ROG CROSSHAIR X870E EXTREME TEST BIOS 9921 based on 1901

1. Update AGESA version to 1.2.8.0

2. Changed the default Nitro to 1/3/1

3. Some ODT rules changes for 16x2 6000cl26 1.4v and 1.45v kit

4. Already apply Group B parameters for 16x2 6000cl26 1.4v and 1.45v kit

Download

*Starting from this BIOS, TRFC2 and TRFCSB are work now, so if you set the values low, cant to boot