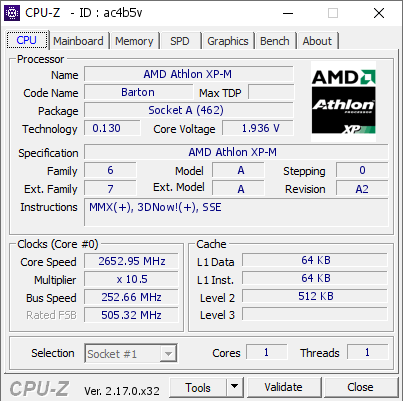

Aber auch interessant: Das Board setzt beim POST nicht direkt die eingestellt höhere Vcore, sondern geht erstmal für 1-2 Sekunden auf 1.625V. Danach gehts dann auf die 1.8V. Bei 1.88V komm ich übrigens nichtmal ansatzweise ins O/S, egal welcher Takt. Bestätigt meine vorherigen Beobachtungen, dass VRM hier definitiv (zumindest auf meinem Board) eine Schwachstelle ist.

Hmmm... Laut Datenblatt des VRM IC (L6917BD) kann man die VID Inputs direkt mit GND verbinden, ohne weiteren Vorwiderstand. Also angenommen man würde die Verbindung von CPU und dem SuperIO Chip (ASB100) zum L6917BD trennen und stattdessen dort einen Jumper oder DIP Switch installieren, könnte man völlig unabhängig vom Bios die Vcore frei von 1.100V bis 1.850V einstellen. Und ich vermute, dass der L6917BD die Vcore (weil er denkt die Cpu hätte diese Custom VID ab Werk) direkt anlegt, wenn er gestartet ist. Die Programmierung der Vcore durch den ASB100 entfällt ja komplett. Das einzige was schiefgehen könnte ist, dass der ASB100 erwartet die VID der Cpu auslesen zu können. Sprich reines trennen würde ich nicht machen, sondern die Verbindung von CPU VID zu ASB100 bestehen lassen und nur den L6917B entkoppeln. Ich vermute außerdem, dass man die Vcore dann im Bios auf Auto stehen lassen sollte.

Zweiter Gedanke: der L6917B geht bei ~2.05V in die OVP. Ab Werk ist der so gebastelt, dass die Range von 1.100 bis 1.850V geht. Man kann den aber anders verdrahten und theoretisch auch z.B. als 5V Wandler nutzen. Angenommen man frisiert den entsprechenden Spannungsteiler, dann könnte man die Vcore Range entsprechend angeben. Meinetwegen um 25% auf 1.375 bis 2.315V. Weil man den Arbeitsbereich verschiebt, sollte sich die OVP mit verschieben.

Um diese Wall of Text mal zu verbildlichen... Hier sieht man die Verschaltung des VID4 Pins auf dem A7N8X v2.0, inklusive der Widerstandsarray-Bennenung und -Werte gemäß Boardview. Man sieht, dass oben rechts ein Pullup (vermutlich für "keine Cpu installiert" und damit niemals ein Pin floating ist) und oben links die Cpu. Dann den 7407 Treiber (evtl. zur Verstärkung des Signals?) und unten links wieder einen Pullup, der in Richtung L6917B und ASB100 liegt. Angenommen man wirft die pink ausgestrichenen Widerstände raus und baut einen Bypass vom Pullup zum ASB100, dann sollte das dem ASB100 weiterhin ermöglichen die Vcore auszulesen. Gleichzeitig entfernt man RN2 und RN183 und trennt somit den L6917B vom Rest. Dort kommt dann ein Jumper oder DIP Switch dran und schwupp sollte die Vcore voll einstellbar sein. Der L6917B hat einen internen Pullup, sprich wir brauchen die VID Pins nur offen lassen (floating) oder auf GND ziehen.

Achtung: Die Idee ist ungetestet und nur laut gedacht!

Bei 1.88V komm ich übrigens nichtmal ansatzweise ins O/S, egal welcher Takt. Bestätigt meine vorherigen Beobachtungen, dass VRM hier definitiv (zumindest auf meinem Board) eine Schwachstelle ist.

Hast du ein Oszi da um ggf. mal die Restwelligkeit zu messen? Da ist doch was im Argen, weshalb das Board den Boot verweigert. Testen kannst du ja auch unter Luftkühlung mit einer Dulli Cpu... ein Zalman 7000CU sollte einen Barton bei 1.95V und moderatem Takt (2ghz oder so) eigentlich wegstecken.

Aber heute sind diese Mainboards über 20 Jahre alt und haben immer noch die gleichen Kondensatoren. Ich halte es für unmöglich, dass sie lange 2,2vcore Lasten aushalten können

This is why most users on this forum will recap the boards with new polymer capacitors. Usually the old caps are dead, expecially when Rubycon MBZ or MCZ or Nichicon HM are soldered onto the boards...