Dich limitieren beim BCLK nur die Vsoc und deine Timings. Wenn rcd eine Grenze erreicht hilft mehr cldo vddp auch nixTrp, trc und tRAS habe ich schon Mal getestet mit weniger und das Ergebnis war reproduzierbar schlechter als mit meinen 36, 52 und 88 in games, welches ja den Formeln entspräche.

@Induktor

Das mit der Einstellung schau ich nur Mal an. Die VDDP auf 1,1 V hilft mir aber beim BCLK, den ich heute Versuche auf 101 oder 102 zu bekommen. ^^

Dazu gehe ich auf 6000 runter, um nicht wieder in die Situation zu kommen, dass der Takt limitiert. Gestern gingen nämlich 6262@cl26 nicht im ersten schnellen Versuch.

tWRRD sollten nach meiner Recherche bei DR bei 2 bleiben laut diversen Beiträgen.

Beitrag automatisch zusammengeführt:

Auch bei mir scheinen die 1,59 V dir mindest Spannung zu sein für cl26. ^^

1,55 V und auch 1,57 V bringt nen Fehler in 1usmus, Test 1 und 0 waren es.

1,59 V und schon ein cycle erfolgreich durch.

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

[Sammelthread] Ryzen DDR5 RAM OC Thread

- Ersteller Reous

- Erstellt am

ollivetti

Semiprofi

- Mitglied seit

- 27.06.2025

- Beiträge

- 157

- Ort

- Stuttgart

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800x3D

- Mainboard

- ASUS ROG STRIX B850 F-Gaming Wifi

- Kühler

- Arctic Liquid Freezer III 360

- Speicher

- 64GB G.SKill Trident Z5 Neo 6000J2836G32G@6200

- Grafikprozessor

- Radeon Sapphire RX 9070 XT Nitro+

- Display

- DELL AW3423DWF

- SSD

- 4TB Kingston Fury Renegade & 4TB Lexar NM790

- Soundkarte

- S.M.S.L M400 & S.M.S.L SP400

- Gehäuse

- Lian Li Lancool III

- Netzteil

- Corsair Hx1000i 2023

- Keyboard

- Steelseries Apex Pro

- Mouse

- Razer Basilisk V3 Pro 35K

- Betriebssystem

- Windows 11

OK, danke dir. 👍Dich limitieren beim BCLK nur die Vsoc und deine Timings. Wenn rcd eine Grenze erreicht hilft mehr cldo vddp auch nix

Dann bleibt es bei 101, da 102 schon gar nicht bootet. ^^

Echt meh, Pech mit meiner CPU zu haben, aber gut, was solls. Das beste draus machen. ^^

ThunderXX80

Semiprofi

- Mitglied seit

- 10.05.2025

- Beiträge

- 95

Ohne externen Clock Generator am Board würde ich den BCLK nicht anheben. 102MHz laufen oft schon nicht zuverlässig.

Das ist kein Problem der CPU, sondern der Systemarchitektur geschuldet.

Das ist kein Problem der CPU, sondern der Systemarchitektur geschuldet.

Major2312

Enthusiast

- Mitglied seit

- 22.03.2008

- Beiträge

- 111

- Ort

- Mittelsachsen

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 9950X3D/SP120 @ TG delidded+TG Conductonaut Extreme @ CO tuned

- Mainboard

- ASUS ROG Crosshair X870E Hero @ Bios 2102

- Kühler

- TG Mycro Direct-Die PRO V1 @ AC NexXxoS XT45 SuperNova 1260 @ 9 x Thermaltake EX14 Pro

- Speicher

- 2x32GB G.Skill F5-6400J3239G32GX2 @ 6000MHz CL28-16-36-32-44-76@VDD 1,41V @ Jonsbo(Scythe) NF-1

- Grafikprozessor

- Sapphire Nitro+ Radeon RX 9070 XT @ UV -70mV @ Alphacool Core/TG KryoSheet/TG Putty Pro

- Display

- LG UltraGear OLED 32GS95UX-B

- SSD

- Samsung 990 Pro M.2 1TB, WD SN850X 8TB, Crucial T700 M.2 4TB, Samsung 860 Evo 2TB/870 Evo 2TB

- Soundkarte

- Onboard Realtek ALC4080

- Gehäuse

- Lian Li O11 Dynamic EVO RGB (6 x Lian Li Uni Fan SL-INF140 Reverse)

- Netzteil

- be quiet! Dark Power 13 1000W ATX 3.0

- Keyboard

- ASUS ROG Strix Flare II Animate

- Mouse

- Razer Basilisk V3 Pro auf SteelSeries QcK Hard

- Betriebssystem

- Windows 11 Pro x64

- Sonstiges

- 5.2.6 Setup: Denon AVC-X3800H + Marantz MM7025 + DALI Oberon Vokal + 4 Dali Oberon On-Wall + 4 Dali Alteco C-1 + Dali Fazon Sat + BEC IC50 + Klipsch RP-1000SW + SVS PB-2000Pro + Dirac Live ART

- Internet

- ▼110 MBit ▲40 MBit

Gibt es Möglichkeiten/Erfahrungswerte die VSOC Voltage gezielt zu stressen auf Stabilität?

ollivetti

Semiprofi

- Mitglied seit

- 27.06.2025

- Beiträge

- 157

- Ort

- Stuttgart

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800x3D

- Mainboard

- ASUS ROG STRIX B850 F-Gaming Wifi

- Kühler

- Arctic Liquid Freezer III 360

- Speicher

- 64GB G.SKill Trident Z5 Neo 6000J2836G32G@6200

- Grafikprozessor

- Radeon Sapphire RX 9070 XT Nitro+

- Display

- DELL AW3423DWF

- SSD

- 4TB Kingston Fury Renegade & 4TB Lexar NM790

- Soundkarte

- S.M.S.L M400 & S.M.S.L SP400

- Gehäuse

- Lian Li Lancool III

- Netzteil

- Corsair Hx1000i 2023

- Keyboard

- Steelseries Apex Pro

- Mouse

- Razer Basilisk V3 Pro 35K

- Betriebssystem

- Windows 11

Gibt es Möglichkeiten/Erfahrungswerte die VSOC Voltage gezielt zu stressen auf Stabilität?

Ich nutze dafür immer Y-Cruncher mit der folgenden Tastenkombination: 2, 11, 12, 13, 4, 600, 5, 6200.

Und mit der 0 dann starten.

Er läuft dann ca. Ne Stunde und gibt entweder nen Fehler aus oder das system friert ein. ^^

AdiSimpson

Enthusiast

OCCT mit combined CPU/RAM/GPU-Adaptive Setting.Gibt es Möglichkeiten/Erfahrungswerte die VSOC Voltage gezielt zu stressen auf Stabilität?

ollivetti

Semiprofi

- Mitglied seit

- 27.06.2025

- Beiträge

- 157

- Ort

- Stuttgart

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800x3D

- Mainboard

- ASUS ROG STRIX B850 F-Gaming Wifi

- Kühler

- Arctic Liquid Freezer III 360

- Speicher

- 64GB G.SKill Trident Z5 Neo 6000J2836G32G@6200

- Grafikprozessor

- Radeon Sapphire RX 9070 XT Nitro+

- Display

- DELL AW3423DWF

- SSD

- 4TB Kingston Fury Renegade & 4TB Lexar NM790

- Soundkarte

- S.M.S.L M400 & S.M.S.L SP400

- Gehäuse

- Lian Li Lancool III

- Netzteil

- Corsair Hx1000i 2023

- Keyboard

- Steelseries Apex Pro

- Mouse

- Razer Basilisk V3 Pro 35K

- Betriebssystem

- Windows 11

Well then.BCLK auf 101 war nicht erfolgreich. War nicht stabil zu bekommen der RAM.

Mein Resümee für heute ist, dass

6000CL26 auch seine 1,51 V ggf. Etwas mehr benötigt und der RAM wird da auch knapp 55° C warm.

Da kann ich gleich bei 6200 mit 1,6V oder 1,59 V bleiben. Der Mehrverbrauch istda kaum vorhanden und die Temperatur ist auch bei uns die 55° C.

Manchmal echt spannend zu sehen wie unterschiedlich die einzelnen Komponenten sind. ^^

Mein Resümee für heute ist, dass

6000CL26 auch seine 1,51 V ggf. Etwas mehr benötigt und der RAM wird da auch knapp 55° C warm.

Da kann ich gleich bei 6200 mit 1,6V oder 1,59 V bleiben. Der Mehrverbrauch istda kaum vorhanden und die Temperatur ist auch bei uns die 55° C.

Manchmal echt spannend zu sehen wie unterschiedlich die einzelnen Komponenten sind. ^^

Ardadamarda

Enthusiast

- Mitglied seit

- 22.06.2006

- Beiträge

- 380

- Ort

- Kanton Zürich

- Desktop System

- Gaming PC

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800X3D

- Mainboard

- Asus ROG STRIX B650E-E GAMING WIFI

- Kühler

- Noctua NH-D15S

- Speicher

- TeamGroup T-Force XTREEM 2x16GB, DDR5-6000, CL28-36-36-48-360, 1.4V

- Grafikprozessor

- Gigabyte RTX 5080 GAMING OC 16G

- Display

- Alienware AW3423DWF, 34" QD-OLED, 3440x1440 @ 120hz 10bit

- SSD

- 2x Samsung 990Pro 2TB, NVMe SSD, PCIe 4.0, M.2

- Soundkarte

- Realtek ALC4080 / ASUS SupremeFX

- Gehäuse

- Lian Li O11 Air Mini (Front/Bottom: je 2xNF-A14 PWM, Rear/Top: je 1xNF-A12x25 PWM)

- Netzteil

- Corsair SF Series Platinum SF750

- Keyboard

- Logitech Prodigy G213

- Mouse

- Logitech G502 Hero

- Betriebssystem

- Windows 11 Pro x64

- Webbrowser

- Google Chrome

- Internet

- ▼10 Gbit/s ▲10 Gbit/s

Ich habe die Teamgroup jetzt zum laufen gebracht, allerdings musste ich vorher mit meinem alten RAM im Bios manuell DDR5-4800 einstellen.

Dann den neuen RAM eingebaut und so konnte es booten.

Aber das ist doch nicht nachhaltig oder?

Beim nächsten Bios Update/CMOS clear stehe ich ja wieder am Anfang.

Kann ja nicht immer alten RAM einbauen um dann manuell auf DDR5-4800 einstellen damit der neue RAM dann bootet.

Der RAM hat ein 7200 und 6000 XMP/EXPO Profil.

Allerdings ist das 7200 Profil an Position 0 und das 6000 Profil erst an Position 1.

Hat jemand ähnliche Erfahrungen? Gibt es da einen Trick?

Dann den neuen RAM eingebaut und so konnte es booten.

Aber das ist doch nicht nachhaltig oder?

Beim nächsten Bios Update/CMOS clear stehe ich ja wieder am Anfang.

Kann ja nicht immer alten RAM einbauen um dann manuell auf DDR5-4800 einstellen damit der neue RAM dann bootet.

Der RAM hat ein 7200 und 6000 XMP/EXPO Profil.

Allerdings ist das 7200 Profil an Position 0 und das 6000 Profil erst an Position 1.

Hat jemand ähnliche Erfahrungen? Gibt es da einen Trick?

Zuletzt bearbeitet:

Brain's City

Profi

- Mitglied seit

- 21.04.2022

- Beiträge

- 170

ThunderXX80

Semiprofi

- Mitglied seit

- 10.05.2025

- Beiträge

- 95

Zu deinem Problem kann ich leider nicht viel beitragen, aber mein Teamgroup 2x16GB 7200-CL34 Kit wird problemlos auf mehreren Boards erkannt. Den RAM vor dem Wechsel der Module im BIOS zurückzusetzen schadet aber eh selten

- Mitglied seit

- 19.08.2003

- Beiträge

- 3.449

- Desktop System

- Lieselotte

- Details zu meinem Desktop

- Prozessor

- 16-Core AMD Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike (MS-7E48) BIOS 1: A30/ 2:A51

- Kühler

- CPU Cooler Alphacool Core 1 ; Supernova 1260mm ; EKWB Coolstream Xe 360; NexXxoS ST20 HPE; VPP Apex

- Speicher

- G Skill F5-8000J4048G24G

- Grafikprozessor

- INNO3D GeForce RTX 5090 X3 OC

- Display

- LG UltraGear 34GP950G-B

- SSD

- WD BLACK SN8100 2TB; WD_BLACK SN850X 2TB ; CT2000BX500SSD1

- HDD

- WD Black SATA 8TB

- Gehäuse

- PHANTEKS Enthoo 719

- Netzteil

- FSP Hydro PTM Pro 1350W

- Keyboard

- RAZER BLACKWIDOW V4 LOW-PROFILE HYPERSPEED

- Mouse

- Logitech G604; G502X ; Razer Naga V2

- Betriebssystem

- WIN 11 25H2

- Sonstiges

- RAZER Blackshark V2 Pro Headset

- Internet

- ▼250 Mbit/s ▲40 Mbit/s

tcl 36 habe ich mit dem MSI noch nicht hinbekommen, ist aber nicht wirklich langsamer als unter dem Taichi.

Ardadamarda

Enthusiast

- Mitglied seit

- 22.06.2006

- Beiträge

- 380

- Ort

- Kanton Zürich

- Desktop System

- Gaming PC

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800X3D

- Mainboard

- Asus ROG STRIX B650E-E GAMING WIFI

- Kühler

- Noctua NH-D15S

- Speicher

- TeamGroup T-Force XTREEM 2x16GB, DDR5-6000, CL28-36-36-48-360, 1.4V

- Grafikprozessor

- Gigabyte RTX 5080 GAMING OC 16G

- Display

- Alienware AW3423DWF, 34" QD-OLED, 3440x1440 @ 120hz 10bit

- SSD

- 2x Samsung 990Pro 2TB, NVMe SSD, PCIe 4.0, M.2

- Soundkarte

- Realtek ALC4080 / ASUS SupremeFX

- Gehäuse

- Lian Li O11 Air Mini (Front/Bottom: je 2xNF-A14 PWM, Rear/Top: je 1xNF-A12x25 PWM)

- Netzteil

- Corsair SF Series Platinum SF750

- Keyboard

- Logitech Prodigy G213

- Mouse

- Logitech G502 Hero

- Betriebssystem

- Windows 11 Pro x64

- Webbrowser

- Google Chrome

- Internet

- ▼10 Gbit/s ▲10 Gbit/s

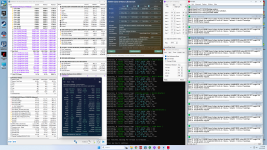

Erste Gehversuche (Profil: H 16A 6000 scharf zen4 SR):

Könnte ich mit VDDIO und VDDQ noch weiter runter?

GDM musste ich wieder anschalten, gab sofort Fehler.

Könnte ich mit VDDIO und VDDQ noch weiter runter?

GDM musste ich wieder anschalten, gab sofort Fehler.

ollivetti

Semiprofi

- Mitglied seit

- 27.06.2025

- Beiträge

- 157

- Ort

- Stuttgart

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800x3D

- Mainboard

- ASUS ROG STRIX B850 F-Gaming Wifi

- Kühler

- Arctic Liquid Freezer III 360

- Speicher

- 64GB G.SKill Trident Z5 Neo 6000J2836G32G@6200

- Grafikprozessor

- Radeon Sapphire RX 9070 XT Nitro+

- Display

- DELL AW3423DWF

- SSD

- 4TB Kingston Fury Renegade & 4TB Lexar NM790

- Soundkarte

- S.M.S.L M400 & S.M.S.L SP400

- Gehäuse

- Lian Li Lancool III

- Netzteil

- Corsair Hx1000i 2023

- Keyboard

- Steelseries Apex Pro

- Mouse

- Razer Basilisk V3 Pro 35K

- Betriebssystem

- Windows 11

Interessant, dass

Teste Mal, ob das nicht Performanceeinbussen gibt.

Sonst sieht es gut aus. Kannst versuchen auf 6200 zu gehen oder cl26. Oder halt Spannungen weiter senken.

Wenn mehr an den timings gehen soll oder MTS, dann stell VDDIO auf Auto.

tRAS 28? Bissl arg niedrig.Erste Gehversuche (Profil: H 16A 6000 scharf zen4 SR):

Könnte ich mit VDDIO und VDDQ noch weiter runter?

GDM musste ich wieder anschalten, gab sofort Fehler.

Anhang anzeigen 1126518

Teste Mal, ob das nicht Performanceeinbussen gibt.

Sonst sieht es gut aus. Kannst versuchen auf 6200 zu gehen oder cl26. Oder halt Spannungen weiter senken.

Wenn mehr an den timings gehen soll oder MTS, dann stell VDDIO auf Auto.

Ardadamarda

Enthusiast

- Mitglied seit

- 22.06.2006

- Beiträge

- 380

- Ort

- Kanton Zürich

- Desktop System

- Gaming PC

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800X3D

- Mainboard

- Asus ROG STRIX B650E-E GAMING WIFI

- Kühler

- Noctua NH-D15S

- Speicher

- TeamGroup T-Force XTREEM 2x16GB, DDR5-6000, CL28-36-36-48-360, 1.4V

- Grafikprozessor

- Gigabyte RTX 5080 GAMING OC 16G

- Display

- Alienware AW3423DWF, 34" QD-OLED, 3440x1440 @ 120hz 10bit

- SSD

- 2x Samsung 990Pro 2TB, NVMe SSD, PCIe 4.0, M.2

- Soundkarte

- Realtek ALC4080 / ASUS SupremeFX

- Gehäuse

- Lian Li O11 Air Mini (Front/Bottom: je 2xNF-A14 PWM, Rear/Top: je 1xNF-A12x25 PWM)

- Netzteil

- Corsair SF Series Platinum SF750

- Keyboard

- Logitech Prodigy G213

- Mouse

- Logitech G502 Hero

- Betriebssystem

- Windows 11 Pro x64

- Webbrowser

- Google Chrome

- Internet

- ▼10 Gbit/s ▲10 Gbit/s

tRAS wartet auf tRTP, daher wäre die Formel tRAS (min) = tRCD + tRTP.

Es hat sich bei M-Die ein Wert von 28 durchgesetzt, was weder richtig ist, noch die beste Leistung bringt. Ist einfach der niedrigste Wert, den man normalerweise einstellen kann.

Habe das hier beim stöbern gefunden und werde das mal ausprobieren, ist aus dem Intel DDR5 OC Thread.

- Mitglied seit

- 19.08.2003

- Beiträge

- 3.449

- Desktop System

- Lieselotte

- Details zu meinem Desktop

- Prozessor

- 16-Core AMD Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike (MS-7E48) BIOS 1: A30/ 2:A51

- Kühler

- CPU Cooler Alphacool Core 1 ; Supernova 1260mm ; EKWB Coolstream Xe 360; NexXxoS ST20 HPE; VPP Apex

- Speicher

- G Skill F5-8000J4048G24G

- Grafikprozessor

- INNO3D GeForce RTX 5090 X3 OC

- Display

- LG UltraGear 34GP950G-B

- SSD

- WD BLACK SN8100 2TB; WD_BLACK SN850X 2TB ; CT2000BX500SSD1

- HDD

- WD Black SATA 8TB

- Gehäuse

- PHANTEKS Enthoo 719

- Netzteil

- FSP Hydro PTM Pro 1350W

- Keyboard

- RAZER BLACKWIDOW V4 LOW-PROFILE HYPERSPEED

- Mouse

- Logitech G604; G502X ; Razer Naga V2

- Betriebssystem

- WIN 11 25H2

- Sonstiges

- RAZER Blackshark V2 Pro Headset

- Internet

- ▼250 Mbit/s ▲40 Mbit/s

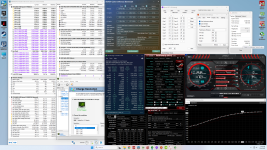

...der latency killer funktioniert auf dem MSI etwas besser, hier mit LK auf enabled, ohne wär´s ~69 auf dem MSI. Das Taichi lag so um die 67.

Das MSI verzeiht einem bei Weitem weniger als das Taichi. Man muss um einiges mehr den CMOS reset bemühen bei manuellen Einstellungen. Dafür sind die MSI Presets besser. Sowohl für PBO als auch für die unterschiedlichen Ram Settings. Vielleicht mag sich das mit den neueren Biose verbessert haben, das werde ich später mal auf dem 2. Bios Chip ausprobieren.

Das MSI verzeiht einem bei Weitem weniger als das Taichi. Man muss um einiges mehr den CMOS reset bemühen bei manuellen Einstellungen. Dafür sind die MSI Presets besser. Sowohl für PBO als auch für die unterschiedlichen Ram Settings. Vielleicht mag sich das mit den neueren Biose verbessert haben, das werde ich später mal auf dem 2. Bios Chip ausprobieren.

ThunderXX80

Semiprofi

- Mitglied seit

- 10.05.2025

- Beiträge

- 95

@Neon Knights : wieso nicht twr auf 48? Das hat bei mir noch bei jedem Kit geklappt. Sogar mit Micron Chips.

Mich bestätigt immer mehr mein Gedanke, dass ich ein richtig mieses 48GB Kit erhalten habe, wenn ich eure Settings sehe. Mein 48GB Kit geht unmöglich niedriger als 200ns trfc.

Und auch sonst sind meine stabilen Setttings deutlich schlechter, als das was ich hier sehe. (aber twr48 geht bei mir immer )

)

Mich bestätigt immer mehr mein Gedanke, dass ich ein richtig mieses 48GB Kit erhalten habe, wenn ich eure Settings sehe. Mein 48GB Kit geht unmöglich niedriger als 200ns trfc.

Und auch sonst sind meine stabilen Setttings deutlich schlechter, als das was ich hier sehe. (aber twr48 geht bei mir immer

- Mitglied seit

- 19.08.2003

- Beiträge

- 3.449

- Desktop System

- Lieselotte

- Details zu meinem Desktop

- Prozessor

- 16-Core AMD Ryzen 9 9950X3D

- Mainboard

- MSI MEG X870E Godlike (MS-7E48) BIOS 1: A30/ 2:A51

- Kühler

- CPU Cooler Alphacool Core 1 ; Supernova 1260mm ; EKWB Coolstream Xe 360; NexXxoS ST20 HPE; VPP Apex

- Speicher

- G Skill F5-8000J4048G24G

- Grafikprozessor

- INNO3D GeForce RTX 5090 X3 OC

- Display

- LG UltraGear 34GP950G-B

- SSD

- WD BLACK SN8100 2TB; WD_BLACK SN850X 2TB ; CT2000BX500SSD1

- HDD

- WD Black SATA 8TB

- Gehäuse

- PHANTEKS Enthoo 719

- Netzteil

- FSP Hydro PTM Pro 1350W

- Keyboard

- RAZER BLACKWIDOW V4 LOW-PROFILE HYPERSPEED

- Mouse

- Logitech G604; G502X ; Razer Naga V2

- Betriebssystem

- WIN 11 25H2

- Sonstiges

- RAZER Blackshark V2 Pro Headset

- Internet

- ▼250 Mbit/s ▲40 Mbit/s

...weil 54 ein Erfahrungswert vom Taichi war. 48 lief dort auch eher unzuverlässig. Vor ein paar Tagen hatte ich da noch 60 - das war von einem der MSI Presets. Die 54 muss ich aber dahingehend auch noch validieren.@Neon Knights : wieso nicht twr auf 48? Das hat bei mir noch bei jedem Kit geklappt. Sogar mit Micron Chips.

Mich bestätigt immer mehr mein Gedanke, dass ich ein richtig mieses 48GB Kit erhalten habe, wenn ich eure Settings sehe. Mein 48GB Kit geht unmöglich niedriger als 200ns trfc.

Und auch sonst sind meine stabilen Setttings deutlich schlechter, als das was ich hier sehe. (aber twr48 geht bei mir immer)

übrigens was ich auch unschön finde. Packe ich auf dem MSI proc odt PU / PD manuell auf 48 Ohm(siehe Taichi) an, booted das Ferkel nicht mehr- also wieder CMOS Reset. Was ich noch ausprobieren will ist PU 48 ohm und PD auf Auto lassen- mal sehen. Der mag es absolut nicht wenn man da manuell rumfummelt. Was das MSI auch nicht anbietet ist eine Nitro Einstellung (kann´s nicht finden) , zumindest nicht mit diesem älteren Bios.

Zuletzt bearbeitet:

ThunderXX80

Semiprofi

- Mitglied seit

- 10.05.2025

- Beiträge

- 95

Ich hab mit automatisch gesetzten Widerständen die besten Ergebnisse gemacht. Gefühlt reagiert da jedes Board anders. Wahrscheinlich weil die Leiterbahnen anders laufen.

Aber es ist echt erstaunlich wie unterschiedlich die Erfahrungen auch sonst sind, weil twr48 bei mir noch bei jedem Kit 100% stabil war. Egal ob DDR5-8100 oder. 6000 und komplett egal welche Chips auf den Modulen waren.

Aber es ist echt erstaunlich wie unterschiedlich die Erfahrungen auch sonst sind, weil twr48 bei mir noch bei jedem Kit 100% stabil war. Egal ob DDR5-8100 oder. 6000 und komplett egal welche Chips auf den Modulen waren.

ollivetti

Semiprofi

- Mitglied seit

- 27.06.2025

- Beiträge

- 157

- Ort

- Stuttgart

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800x3D

- Mainboard

- ASUS ROG STRIX B850 F-Gaming Wifi

- Kühler

- Arctic Liquid Freezer III 360

- Speicher

- 64GB G.SKill Trident Z5 Neo 6000J2836G32G@6200

- Grafikprozessor

- Radeon Sapphire RX 9070 XT Nitro+

- Display

- DELL AW3423DWF

- SSD

- 4TB Kingston Fury Renegade & 4TB Lexar NM790

- Soundkarte

- S.M.S.L M400 & S.M.S.L SP400

- Gehäuse

- Lian Li Lancool III

- Netzteil

- Corsair Hx1000i 2023

- Keyboard

- Steelseries Apex Pro

- Mouse

- Razer Basilisk V3 Pro 35K

- Betriebssystem

- Windows 11

Ja, bei mir bisher auch mit den Widerständen, aber ich bin bei weitem noch nciht durch mit allen Möglichkeiten.Ich hab mit automatisch gesetzten Widerständen die besten Ergebnisse gemacht. Gefühlt reagiert da jedes Board anders. Wahrscheinlich weil die Leiterbahnen anders laufen.

Aber es ist echt erstaunlich wie unterschiedlich die Erfahrungen auch sonst sind, weil twr48 bei mir noch bei jedem Kit 100% stabil war. Egal ob DDR5-8100 oder. 6000 und komplett egal welche Chips auf den Modulen waren.

Mal eine andere Frage in die Runde:

Wie sind eure Erfahrungen bzw. gibt es schon welche, die länger eine hohe Spannung >1,6V betreiben und wie sich die DIMMs dabei verhalten nach mehreren Wochen in diesem Betrieb? Gibt es ggf. Ausfallerscheinungen oder ANzeichen einer schnelleren Alterung der Speicher?

NightFly2

Urgestein

- Mitglied seit

- 11.09.2011

- Beiträge

- 2.728

- Details zu meinem Desktop

- Prozessor

- i9 9900k@5Ghz

- Mainboard

- Asus Apex XI

- Kühler

- Custom wasserkühlung

- Speicher

- F4-3600C16D-32GTRS @4000 CL16

- Grafikprozessor

- ASUS GeForce RTX 3090 ROG STRIX OC GAMING

- Display

- LG OLED48CX8

- SSD

- Samsung 970 EVO 1 TB NVMe M.2

- Gehäuse

- Phanteks Enthoo primo

- Netzteil

- Seasonic Snow Silent 1050W

- Betriebssystem

- Win 10 Pro

ich hab ab dem 19 März 1.62 am laufen mit Luftkühler auf die DIMMs und 0 Probleme , aber ich spiele auch nur oder lasse RAM Tests laufen. und sollten die Kaputt gehen so RAM kostet nicht die Welt also die 150 Euro sind mir egalJa, bei mir bisher auch mit den Widerständen, aber ich bin bei weitem noch nciht durch mit allen Möglichkeiten.

Mal eine andere Frage in die Runde:

Wie sind eure Erfahrungen bzw. gibt es schon welche, die länger eine hohe Spannung >1,6V betreiben und wie sich die DIMMs dabei verhalten nach mehreren Wochen in diesem Betrieb? Gibt es ggf. Ausfallerscheinungen oder ANzeichen einer schnelleren Alterung der Speicher?

RedF

Enthusiast

- Mitglied seit

- 07.03.2020

- Beiträge

- 5.699

- Ort

- am Main

- Desktop System

- Rechner

- Laptop

- Laptop

- Details zu meinem Desktop

- Prozessor

- Ryzen 7800X3D

- Mainboard

- ASrock X670E Taichi

- Kühler

- Core 1 360+1080 Radiator

- Speicher

- 32GB 6200MHz

- Grafikprozessor

- 7900XTX

- Display

- Samsung C32HG70

- SSD

- 2x960GB Corsair MP510 1x512GB Samsung PM961 1x2TB FireCuda

- HDD

- Seagate 4TB

- Opt. Laufwerk

- -

- Soundkarte

- GC7

- Gehäuse

- be quiet! 601 Silentbase / aufgesägt

- Netzteil

- Seasonic Prime 1000

- Keyboard

- logitech G815

- Mouse

- Xtrfy MZ1

- Betriebssystem

- W11

- Webbrowser

- Firefox

- Sonstiges

- 3D-Drucker: Qidi Plus 4, Ender 3V2 (war er mal)

Bei der Spannung machen sie wahrscheinlich schon nach 15 Jahren die Grätsche und nicht nach 25.ich hab ab dem 19 März 1.62 am laufen mit Luftkühler auf die DIMMs und 0 Probleme , aber ich spiele auch nur oder lasse RAM Tests laufen. und sollten die Kaputt gehen so RAM kostet nicht die Welt also die 150 Euro sind mir egal

- Mitglied seit

- 20.01.2017

- Beiträge

- 4.818

- Ort

- am Rhein

- Desktop System

- Gaming | Büro

- Laptop

- MacBook Air M2

- Details zu meinem Desktop

- Prozessor

- 9800X3D | 7950X

- Mainboard

- X870E Nova | B850 Steel Legend

- Kühler

- Freezer 36 | Core 1 + SuperNova

- Speicher

- 6400-26 | 6200-28

- Grafikprozessor

- 6900 LC | 9070 XT

- Display

- LG 55 Zoll 4K | 3440x1440 + 2560x1440

- Gehäuse

- Fractal North | BQ Silent Base 802

- Netzteil

- BQ 1000W | Corsair 1000W

Bei 1,6X V erschrickt hier noch niemand.

Ist keine drei Tage her, dass glaub ich Vince von 2V gesprochen hat....?

Ist keine drei Tage her, dass glaub ich Vince von 2V gesprochen hat....?

ollivetti

Semiprofi

- Mitglied seit

- 27.06.2025

- Beiträge

- 157

- Ort

- Stuttgart

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800x3D

- Mainboard

- ASUS ROG STRIX B850 F-Gaming Wifi

- Kühler

- Arctic Liquid Freezer III 360

- Speicher

- 64GB G.SKill Trident Z5 Neo 6000J2836G32G@6200

- Grafikprozessor

- Radeon Sapphire RX 9070 XT Nitro+

- Display

- DELL AW3423DWF

- SSD

- 4TB Kingston Fury Renegade & 4TB Lexar NM790

- Soundkarte

- S.M.S.L M400 & S.M.S.L SP400

- Gehäuse

- Lian Li Lancool III

- Netzteil

- Corsair Hx1000i 2023

- Keyboard

- Steelseries Apex Pro

- Mouse

- Razer Basilisk V3 Pro 35K

- Betriebssystem

- Windows 11

Bin gerade am schauen. Habe Anomalien beim zocken festgestellt und bin Grad am gegen testen, ob es an den cl26 liegt.

Mal schauen. Und das mitten am austarieren der CPU mit TDP, EDC, PPT und EDC.

Oh Mann. 😂

Mal schauen. Und das mitten am austarieren der CPU mit TDP, EDC, PPT und EDC.

Oh Mann. 😂

Tatilica

Experte

- Mitglied seit

- 10.06.2020

- Beiträge

- 194

- Ort

- Romania

- Desktop System

- Tatili

- Details zu meinem Desktop

- Prozessor

- Ryzen 9900x3D

- Mainboard

- X870 TOMAHAWK Wifi

- Kühler

- ID Cooling FX240 PRO Black

- Speicher

- Gskill Neo 8000Mhz CL38

- Grafikprozessor

- Asus ProArt OC RTX 4070Super

- Display

- Asus Rog Swift 1440p/165hz

- SSD

- Corsair MP700 PRO 1TB PCI-e 5.0 x4.0

- Gehäuse

- Montech Sky Two GX

- Netzteil

- Corsair 2024 RM1000x ATX 3.1

- Betriebssystem

- Windows 11

Yeah, Killer is working great on MSI, I doubt better PBO & RAM settings presets are improved with newer Bios, just rolled back 1.2.0.3a PatchA, same Profile failed testing 1.2.0.3f runs, no matter what, be aware, don't...the latency killer works a bit better on the MSI, here with LK enabled; without it, it would be around 69 on the MSI. The Taichi was around 67.

The MSI is far less forgiving than the Taichi. You have to work harder to reset the CMOS with manual settings. However, the MSI presets are better, both for PBO and for the various RAM settings. Perhaps this has improved with the newer BIOS; I'll test it later on the second BIOS chip.

Anhang anzeigen 1126578

8055 BCLK100.7 PBO Auto Boost +25 CO--perCore

Agesa 1.2.0.3f same Profile Boost+25 +100 both failed

Agesa 1.2.0.3aPatchA reflashed back to stability origin

![MSI_Overclocking_[2025-06-23-19-49-04].png MSI_Overclocking_[2025-06-23-19-49-04].png](https://www.hardwareluxx.de/community/data/attachments/990/990825-98eefd9f33c9d0b1ae1ae377d407b103.jpg)

Zuletzt bearbeitet:

medifix

Experte

- Mitglied seit

- 23.10.2016

- Beiträge

- 296

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 8400F

- Mainboard

- ASRock B850M Pro-A

- Kühler

- Enermax ETS-T50 @1x140

- Speicher

- DDR5 32GB

- Grafikprozessor

- AMD Radeon RX 9070 @2x140

- Display

- 2560x1440 (WQHD) 60 Hz

- SSD

- 500GB NVMe, 1TB SATA

- Gehäuse

- JONSBO C6 Max

- Netzteil

- Sharkoon Rebel P20 ATX 750W

fclk auf 2500 mit sehr moderater vsoc mit einem 8400f.

habe ich bisher nicht so oft gesehen, nur deshalb mal gezeigt.

hci memtest stabil. das setting ist nicht tm5 getestet.

bei den tm5 90 min testversuchen hatte ich dreimal erfolg, jedoch mit anderen 6200er settings. alle weiteren versuche endeten mit einem späten error alle nach >50 min und bei >50°C. ich interpretiere das als temp-grenze bei ansonsten stabilen settings. wie auch immer, ich lass das vorerst so laufen...

edit:

...für aida cache+mem musste ich die vsoc von 1.160v wieder auf 1.190v erhöhen. alles darunter wurde mit einer errormeldung quittiert.

1 x 10 min 47°C pass

1 x 20 min 44.2°C pass

(mit unterschiedlicher lüfterconfig)

occt cpu+ram nach 05:33 error bei 51.5°C

occt memory 10 min pass bei 50.2°C

bleibt also bei vsoc 1.190v, auch gut.

als nächstes werde ich versuchen die temperatur weiter abzusenken...

habe ich bisher nicht so oft gesehen, nur deshalb mal gezeigt.

hci memtest stabil. das setting ist nicht tm5 getestet.

bei den tm5 90 min testversuchen hatte ich dreimal erfolg, jedoch mit anderen 6200er settings. alle weiteren versuche endeten mit einem späten error alle nach >50 min und bei >50°C. ich interpretiere das als temp-grenze bei ansonsten stabilen settings. wie auch immer, ich lass das vorerst so laufen...

edit:

...für aida cache+mem musste ich die vsoc von 1.160v wieder auf 1.190v erhöhen. alles darunter wurde mit einer errormeldung quittiert.

1 x 10 min 47°C pass

1 x 20 min 44.2°C pass

(mit unterschiedlicher lüfterconfig)

occt cpu+ram nach 05:33 error bei 51.5°C

occt memory 10 min pass bei 50.2°C

bleibt also bei vsoc 1.190v, auch gut.

als nächstes werde ich versuchen die temperatur weiter abzusenken...

Zuletzt bearbeitet:

Ardadamarda

Enthusiast

- Mitglied seit

- 22.06.2006

- Beiträge

- 380

- Ort

- Kanton Zürich

- Desktop System

- Gaming PC

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 9800X3D

- Mainboard

- Asus ROG STRIX B650E-E GAMING WIFI

- Kühler

- Noctua NH-D15S

- Speicher

- TeamGroup T-Force XTREEM 2x16GB, DDR5-6000, CL28-36-36-48-360, 1.4V

- Grafikprozessor

- Gigabyte RTX 5080 GAMING OC 16G

- Display

- Alienware AW3423DWF, 34" QD-OLED, 3440x1440 @ 120hz 10bit

- SSD

- 2x Samsung 990Pro 2TB, NVMe SSD, PCIe 4.0, M.2

- Soundkarte

- Realtek ALC4080 / ASUS SupremeFX

- Gehäuse

- Lian Li O11 Air Mini (Front/Bottom: je 2xNF-A14 PWM, Rear/Top: je 1xNF-A12x25 PWM)

- Netzteil

- Corsair SF Series Platinum SF750

- Keyboard

- Logitech Prodigy G213

- Mouse

- Logitech G502 Hero

- Betriebssystem

- Windows 11 Pro x64

- Webbrowser

- Google Chrome

- Internet

- ▼10 Gbit/s ▲10 Gbit/s

5600B wie auch BN ist nur ein Speedbin von JEDEC. Sagt im Prinzip nichts mehr aus, da alle Speicherhersteller einen eigenen Weg gehen. 5600B Kits funktionieren aber meist bis CL28 gut mit recht wenig Spannung. Es kommt hier hauptsächlich auf die "Minimum Active to Active/Refresh Time (tRCmin)" an.

Hallo Vince,

Kannst du das bitte nochmal kurz erläutern?

Auf welchen Wert genau kommt es an? Denn "Minimum Active to Active/Refresh Time (tRCmin)" kann ich im Rammon nicht finden.

Hier mal ein Dump von meinem Kit:

RAMMon v3.4 Build: 1000 built with SysInfo v3.3 Build: 1000

PassMark (R) Software - www.passmark.com

Memory settings

Transfer rate 6000 MT/s Memory timings 28-36-36-48 Channel mode 2

| Transfer rate | 6000 MT/s |

| Memory timings | 28-36-36-48 |

| Channel mode | 2 |

Memory capacity / benchmarks

L1 cache 80 KB (637.5 GB/s) L2 cache 1024 KB (195.5 GB/s) L3 cache 98304 KB (147.7 GB/s) Physical RAM 31.7 GB (39529 MB/s) Latency 43.750 ns

| L1 cache | 80 KB (637.5 GB/s) |

| L2 cache | 1024 KB (195.5 GB/s) |

| L3 cache | 98304 KB (147.7 GB/s) |

| Physical RAM | 31.7 GB (39529 MB/s) |

| Latency | 43.750 ns |

Memory SPD information

| Item | Slot #1 | Slot #2 | Slot #3 | Slot #4 |

|---|---|---|---|---|

| Ram Type | DDR5 | DDR5 | Not Populated | Not Populated |

| Maximum Clock Speed (MHz) | 3610 (XMP) | 3610 (XMP) | ||

| Maximum Transfer Speed (MT/s) | DDR5-7220 | DDR5-7220 | ||

| Maximum Bandwidth (MB/s) | PC5-28800 | PC5-28800 | ||

| Memory Capacity (MB) | 16384 | 16384 | ||

| DIMM Temperature | 34.000 | 32.000 | ||

| Jedec Manufacture Name | Team Group Inc. | Team Group Inc. | ||

| Search Amazon.com | Search! | Search! | ||

| SPD Revision | 1.0 | 1.0 | ||

| Registered | No | No | ||

| ECC | No | No | ||

| On-Die ECC | Yes | Yes | ||

| DIMM Slot # | 1 | 2 | ||

| Manufactured | Week 49 of Year 2024 | Week 49 of Year 2024 | ||

| Module Part # | UD5-7200 | UD5-7200 | ||

| Module Revision | 0x0 | 0x0 | ||

| Module Serial # | 01045FD1 (04ef00244901045fd1) | 01045FD4 (04ef00244901045fd4) | ||

| Module Manufacturing Location | 0 | 0 | ||

| # of Row Addressing Bits | 16 | 16 | ||

| # of Column Addressing Bits | 10 | 10 | ||

| # of Banks | 32 | 32 | ||

| # of Ranks | 1 | 1 | ||

| Device Width in Bits | 8 | 8 | ||

| Bus Width in Bits | 32 | 32 | ||

| Module Voltage | 1.1V | 1.1V | ||

| CAS Latencies Supported | 22 28 30 32 36 40 42 46 50 | 22 28 30 32 36 40 42 46 50 | ||

| Timings @ Max Frequency (JEDEC) | 46-46-46-90 | 46-46-46-90 | ||

| Maximum frequency (MHz) | 2800 | 2800 | ||

| Maximum Transfer Speed (MT/s) | DDR5-5600 | DDR5-5600 | ||

| Maximum Bandwidth (MB/s) | PC5-22400 | PC5-22400 | ||

| Minimum Clock Cycle Time, tCK (ns) | 0.357 | 0.357 | ||

| Minimum CAS Latency Time, tAA (ns) | 16.428 | 16.428 | ||

| Minimum RAS to CAS Delay, tRCD (ns) | 16.428 | 16.428 | ||

| Minimum Row Precharge Time, tRP (ns) | 16.428 | 16.428 | ||

| Minimum Active to Precharge Time, tRAS (ns) | 32.000 | 32.000 | ||

| Minimum Row Active to Row Active Delay, tRRD (ns) | 0.000 | 0.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Time, tRC (ns) | 48.428 | 48.428 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Command Period, tRFC (ns) | 295.000 | 295.000 | ||

| DDR5 Specific SPD Attributes | ||||

| Maximum Clock Cycle Time, tCKmax (ns) | 1.010 | 1.010 | ||

| Write Recovery time (ns) | 30.000 | 30.000 | ||

| Minimum Auto-Refresh to Active/Auto Refresh Command Period, tRFC2 (ns) | 160.000 | 160.000 | ||

| Minimum Auto-Refresh to Active/Auto Refresh Command Period, tRFC4 (ns) | 130.000 | 130.000 | ||

| Minimum Refresh Recovery Delay Time, tRFC1 (ns) | 0.000 | 0.000 | ||

| Minimum Refresh Recovery Delay Time, tRFC2 (ns) | 0.000 | 0.000 | ||

| Minimum Refresh Recovery Delay Time, tRFCsb (ns) | 0.000 | 0.000 | ||

| Module Type | UDIMM | UDIMM | ||

| Module information SPD revision | 1.0 | 1.0 | ||

| SPD present | Yes | Yes | ||

| SPD device type | SPD5118 | SPD5118 | ||

| SPD Manufacturer | Montage Technology Group (Bank: 7, ID: 0x32) | Montage Technology Group (Bank: 7, ID: 0x32) | ||

| PMIC 0 present | Yes | Yes | ||

| PMIC 0 device type | PMIC5100 | PMIC5100 | ||

| PMIC 0 Manufacturer | Richtek Power (Bank: 11, ID: 0x8C) | Richtek Power (Bank: 11, ID: 0x8C) | ||

| PMIC 1 present | No | No | ||

| PMIC 1 device type | ||||

| PMIC 1 Manufacturer | ||||

| PMIC 2 present | No | No | ||

| PMIC 2 device type | ||||

| PMIC 2 Manufacturer | ||||

| Thermal Sensor 0 present | No | No | ||

| Thermal Sensor 1 present | No | No | ||

| Thermal Sensor device type | ||||

| Thermal Sensor Manufacturer | ||||

| Module Height (mm) | 32 | 32 | ||

| Module Thickness Front (mm) | 2 | 2 | ||

| Module Thickness Back (mm) | 1 | 1 | ||

| Module Reference Card | Raw Card A Rev. 0 | Raw Card A Rev. 0 | ||

| # DRAM Rows | 1 | 1 | ||

| Heat spreader installed | No | No | ||

| Operating Temperature Range | XT (0 to + 95 °C) | XT (0 to + 95 °C) | ||

| Rank Mix | Symmetrical | Symmetrical | ||

| Number of Package Ranks per Channel | 1 | 1 | ||

| Number of Channels per DIMM | 2 | 2 | ||

| Primary bus width per Channel | 32 bits | 32 bits | ||

| Bus width extension per Channel | 0 bits | 0 bits | ||

| DRAM Manufacture ID | 173 | 173 | ||

| DRAM Manufacture Bank | 1 | 1 | ||

| DRAM Manufacture Name | SK Hynix | SK Hynix | ||

| DRAM Stepping | 4.1 | 4.1 | ||

| SDRAM Package Type | Monolithic SDRAM | Monolithic SDRAM | ||

| SDRAM Density Per Die | 16Gb | 16Gb | ||

| SDRAM Bank Groups | 8 | 8 | ||

| SDRAM Banks Per Bank Group | 4 | 4 | ||

| Second SDRAM Package Type | ||||

| Second SDRAM Density Per Die | ||||

| Second SDRAM Column Address Bits | ||||

| Second SDRAM Row Address Bits | ||||

| Second SDRAM Device Width | ||||

| Second SDRAM Bank Groups | ||||

| Second SDRAM Banks Per Bank Group | ||||

| First SDRAM RFM RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) | ||

| First SDRAM RFM RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) | ||

| First SDRAM RFM Required | no | no | ||

| First SDRAM RFM RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 | ||

| Second SDRAM RFM RAAMMT | ||||

| Second SDRAM RFM RAAIMT | ||||

| Second SDRAM RFM Required | ||||

| Second SDRAM RFM RAA Counter Decrement per REF command | ||||

| First SDRAM ARFM Level A RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) | ||

| First SDRAM ARFM Level A RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) | ||

| First SDRAM ARFM Level A supported | no | no | ||

| First SDRAM ARFM Level A RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 | ||

| Second SDRAM ARFM Level A RAAMMT | ||||

| Second SDRAM ARFM Level A RAAIMT | ||||

| Second SDRAM ARFM Level A supported | ||||

| Second SDRAM ARFM Level A RAA Counter Decrement per REF command | ||||

| First SDRAM ARFM Level B RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) | ||

| First SDRAM ARFM Level B RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) | ||

| First SDRAM ARFM Level B supported | no | no | ||

| First SDRAM ARFM Level B RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 | ||

| Second SDRAM ARFM Level B RAAMMT | ||||

| Second SDRAM ARFM Level B RAAIMT | ||||

| Second SDRAM ARFM Level B supported | ||||

| Second SDRAM ARFM Level B RAA Counter Decrement per REF command | ||||

| First SDRAM ARFM Level C RAAMMT | 0X (FGR: 0X) | 0X (FGR: 0X) | ||

| First SDRAM ARFM Level C RAAIMT | 0 (FGR: 0) | 0 (FGR: 0) | ||

| First SDRAM ARFM Level C supported | no | no | ||

| First SDRAM ARFM Level C RAA Counter Decrement per REF command | RAAIMT / 2 | RAAIMT / 2 | ||

| Second SDRAM ARFM Level C RAAMMT | ||||

| Second SDRAM ARFM Level C RAAIMT | ||||

| Second SDRAM ARFM Level C supported | ||||

| Second SDRAM ARFM Level C RAA Counter Decrement per REF command | ||||

| sPPR Granularity | bank group | bank group | ||

| sPPR Undo/Lock | supported | supported | ||

| Burst length 32 | not supported | not supported | ||

| MBIST/mPPR | not supported | not supported | ||

| mPPR/hPPR Abort | not supported | not supported | ||

| PASR | not supported | not supported | ||

| DCA Types Supported | Device supports DCA for 4-phase internal clock(s) | Device supports DCA for 4-phase internal clock(s) | ||

| x4 RMW/ECS Writeback Suppression | not supported | not supported | ||

| x4 RMW/ECS Writeback Suppression MR selector | MR9 | MR9 | ||

| Bounded Fault | not supported | not supported | ||

| SDRAM Nominal Voltage, VDDQ | 1.1V | 1.1V | ||

| SDRAM Nominal Voltage, VPP | 1.8V | 1.8V | ||

| Cyclical Redundancy Code (CRC) for Base Configuration | 9d1a | 9d1a | ||

| XMP Attributes | ||||

| XMP version | 3.0 | 3.0 | ||

| PMIC Vendor ID | 8A8C | 8A8C | ||

| Number of PMICs on DIMM | 1 | 1 | ||

| PMIC capabilities | ||||

| PMIC has capabilities for OC functions | Yes | Yes | ||

| Current PMIC OC is enabled | Yes | Yes | ||

| PMIC voltage default step size | 5mV | 5mV | ||

| OC global reset functions | No | No | ||

| Validation and Certification Capabilities | ||||

| DIMM is self-certified by DIMM vendor | No | No | ||

| PMIC Component is validated by Intel AVL level | No | No | ||

| XMP revision | 1.2 | 1.2 | ||

| XMP Profile 1 | ||||

| Profile name | TG-7200-34-42-84 | TG-7200-34-42-84 | ||

| XMP Certified | No | No | ||

| Recommended number of DIMMs per channel | 1 | 1 | ||

| Module VPP voltage | 1.80V | 1.80V | ||

| Module VDD voltage | 1.40V | 1.40V | ||

| Module VDDQ voltage | 1.40V | 1.40V | ||

| Memory Controller voltage | 1.10V | 1.10V | ||

| Clock speed (MHz) | 3610 | 3610 | ||

| Transfer Speed (MT/s) | DDR5-7220 | DDR5-7220 | ||

| Bandwidth (MB/s) | PC5-28800 | PC5-28800 | ||

| Minimum clock cycle time, tCK (ns) | 0.277 | 0.277 | ||

| Supported CAS latencies | 34 | 34 | ||

| Minimum CAS latency time, tAA (ns) | 9.418 | 9.418 | ||

| Minimum RAS to CAS delay time, tRCD (ns) | 11.634 | 11.634 | ||

| Minimum row precharge time, tRP (ns) | 11.634 | 11.634 | ||

| Minimum active to precharge time, tRAS (ns) | 23.268 | 23.268 | ||

| Supported timing at highest clock speed | 34-42-42-84 | 34-42-42-84 | ||

| Minimum Active to Auto-Refresh Delay, tRC (ns) | 34.902 | 34.902 | ||

| Minimum Write Recovery Time, tWR (ns) | 30.000 | 30.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) | 295.000 | 295.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) | 160.000 | 160.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) | 130.000 | 130.000 | ||

| Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Read Command Delay Time, Same Bank Group, tCCD_L_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Read Command Delay Time, Different Bank Group, tCCD_S_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Read to Precharge Command Delay Time, tRTP (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Four Activate Window, tFAW (ns) | 0.000 | 0.000 | ||

| Advanced Memory Overclocking Features | ||||

| Real-Time Memory Frequency Overclocking | Not supported | Not supported | ||

| Intel Dynamic Memory Boost | Not supported | Not supported | ||

| System CMD Rate Mode | 2N | 2N | ||

| Vendor Personality Byte | 0x00 | 0x00 | ||

| XMP Profile 2 | ||||

| Profile name | TG-6000-38-38-78 | TG-6000-38-38-78 | ||

| XMP Certified | No | No | ||

| Recommended number of DIMMs per channel | 1 | 1 | ||

| Module VPP voltage | 1.80V | 1.80V | ||

| Module VDD voltage | 1.25V | 1.25V | ||

| Module VDDQ voltage | 1.25V | 1.25V | ||

| Memory Controller voltage | 1.10V | 1.10V | ||

| Clock speed (MHz) | 3000 | 3000 | ||

| Transfer Speed (MT/s) | DDR5-6000 | DDR5-6000 | ||

| Bandwidth (MB/s) | PC5-24000 | PC5-24000 | ||

| Minimum clock cycle time, tCK (ns) | 0.333 | 0.333 | ||

| Supported CAS latencies | 38 | 38 | ||

| Minimum CAS latency time, tAA (ns) | 12.654 | 12.654 | ||

| Minimum RAS to CAS delay time, tRCD (ns) | 12.654 | 12.654 | ||

| Minimum row precharge time, tRP (ns) | 12.654 | 12.654 | ||

| Minimum active to precharge time, tRAS (ns) | 25.974 | 25.974 | ||

| Supported timing at highest clock speed | 38-38-38-78 | 38-38-38-78 | ||

| Minimum Active to Auto-Refresh Delay, tRC (ns) | 38.628 | 38.628 | ||

| Minimum Write Recovery Time, tWR (ns) | 30.000 | 30.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) | 295.000 | 295.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) | 160.000 | 160.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) | 130.000 | 130.000 | ||

| Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Read Command Delay Time, Same Bank Group, tCCD_L_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Write to Read Command Delay Time, Different Bank Group, tCCD_S_WTR (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Read to Precharge Command Delay Time, tRTP (ns) | 0.000 (0 nCK) | 0.000 (0 nCK) | ||

| Minimum Four Activate Window, tFAW (ns) | 0.000 | 0.000 | ||

| Advanced Memory Overclocking Features | ||||

| Real-Time Memory Frequency Overclocking | Not supported | Not supported | ||

| Intel Dynamic Memory Boost | Not supported | Not supported | ||

| System CMD Rate Mode | 2N | 2N | ||

| Vendor Personality Byte | 0x00 | 0x00 | ||

| EXPO Attributes | ||||

| EXPO version | 1.0 | 1.0 | ||

| PMIC feature support | ||||

| PMIC 10 mV step size support | No | No | ||

| EXPO Profile 1 | ||||

| DIMMs per channel supported | 1 | 1 | ||

| EXPO Optional Block Support | ||||

| Block 1 enabled | Yes | Yes | ||

| SDRAM VDD | 1.40V | 1.40V | ||

| SDRAM VDDQ | 1.40V | 1.40V | ||

| SDRAM VPP | 1.80V | 1.80V | ||

| Clock speed (MHz) | 3610 | 3610 | ||

| Transfer Speed (MT/s) | DDR5-7220 | DDR5-7220 | ||

| Bandwidth (MB/s) | PC5-28800 | PC5-28800 | ||

| Minimum clock cycle time, tCK (ns) | 0.277 | 0.277 | ||

| Minimum CAS latency time, tAA (ns) | 9.418 | 9.418 | ||

| Minimum RAS to CAS delay time, tRCD (ns) | 11.634 | 11.634 | ||

| Minimum row precharge time, tRP (ns) | 11.634 | 11.634 | ||

| Minimum active to precharge time, tRAS (ns) | 23.268 | 23.268 | ||

| Supported timing at highest clock speed | 34-42-42-84 | 34-42-42-84 | ||

| Minimum Active to Auto-Refresh Delay, tRC (ns) | 34.902 | 34.902 | ||

| Minimum Write Recovery Time, tWR (ns) | 30.000 | 30.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) | 295.000 | 295.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) | 160.000 | 160.000 | ||

| Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) | 130.000 | 130.000 | ||

| Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) | 5.000 | 5.000 | ||

| Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) | 5.000 | 5.000 | ||

| Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) | 20.000 | 20.000 | ||

| Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) | 10.000 | 10.000 | ||

| Minimum Four Activate Window, tFAW (ns) | 8.888 | 8.888 | ||

| Minimum Write to Read Command Delay Time, Same Bank Group, tWTR_L (ns) | 10.000 | 10.000 | ||

| Minimum Write to Read Command Delay Time, Different Bank Group, tWTR_S (ns) | 2.500 | 2.500 | ||

| Minimum Read to Precharge Command Delay Time, tRTP (ns) | 7.500 | 7.500 |

Es ist egal was im SPD gespeichert ist. Egal ob 4800BN, 5600B, 8800B.Hallo Vince,

Kannst du das bitte nochmal kurz erläutern?

Auf welchen Wert genau kommt es an? Denn "Minimum Active to Active/Refresh Time (tRCmin)" kann ich im Rammon nicht finden.

Hier mal ein Dump von meinem Kit:

RAMMon v3.4 Build: 1000 built with SysInfo v3.3 Build: 1000

PassMark (R) Software - www.passmark.com

Memory settings

Transfer rate 6000 MT/s Memory timings 28-36-36-48 Channel mode 2 Memory capacity / benchmarks

L1 cache 80 KB (637.5 GB/s) L2 cache 1024 KB (195.5 GB/s) L3 cache 98304 KB (147.7 GB/s) Physical RAM 31.7 GB (39529 MB/s) Latency 43.750 ns Memory SPD information

Item Slot #1 Slot #2 Slot #3 Slot #4 Ram Type DDR5 DDR5 Not Populated Not Populated Maximum Clock Speed (MHz) 3610 (XMP) 3610 (XMP) Maximum Transfer Speed (MT/s) DDR5-7220 DDR5-7220 Maximum Bandwidth (MB/s) PC5-28800 PC5-28800 Memory Capacity (MB) 16384 16384 DIMM Temperature 34.000 32.000 Jedec Manufacture Name Team Group Inc. Team Group Inc. Search Amazon.com Search! Search! SPD Revision 1.0 1.0 Registered No No ECC No No On-Die ECC Yes Yes DIMM Slot # 1 2 Manufactured Week 49 of Year 2024 Week 49 of Year 2024 Module Part # UD5-7200 UD5-7200 Module Revision 0x0 0x0 Module Serial # 01045FD1 (04ef00244901045fd1) 01045FD4 (04ef00244901045fd4) Module Manufacturing Location 0 0 # of Row Addressing Bits 16 16 # of Column Addressing Bits 10 10 # of Banks 32 32 # of Ranks 1 1 Device Width in Bits 8 8 Bus Width in Bits 32 32 Module Voltage 1.1V 1.1V CAS Latencies Supported 22 28 30 32 36 40 42 46 50 22 28 30 32 36 40 42 46 50 Timings @ Max Frequency (JEDEC) 46-46-46-90 46-46-46-90 Maximum frequency (MHz) 2800 2800 Maximum Transfer Speed (MT/s) DDR5-5600 DDR5-5600 Maximum Bandwidth (MB/s) PC5-22400 PC5-22400 Minimum Clock Cycle Time, tCK (ns) 0.357 0.357 Minimum CAS Latency Time, tAA (ns) 16.428 16.428 Minimum RAS to CAS Delay, tRCD (ns) 16.428 16.428 Minimum Row Precharge Time, tRP (ns) 16.428 16.428 Minimum Active to Precharge Time, tRAS (ns) 32.000 32.000 Minimum Row Active to Row Active Delay, tRRD (ns) 0.000 0.000 Minimum Auto-Refresh to Active/Auto-Refresh Time, tRC (ns) 48.428 48.428 Minimum Auto-Refresh to Active/Auto-Refresh Command Period, tRFC (ns) 295.000 295.000 DDR5 Specific SPD Attributes Maximum Clock Cycle Time, tCKmax (ns) 1.010 1.010 Write Recovery time (ns) 30.000 30.000 Minimum Auto-Refresh to Active/Auto Refresh Command Period, tRFC2 (ns) 160.000 160.000 Minimum Auto-Refresh to Active/Auto Refresh Command Period, tRFC4 (ns) 130.000 130.000 Minimum Refresh Recovery Delay Time, tRFC1 (ns) 0.000 0.000 Minimum Refresh Recovery Delay Time, tRFC2 (ns) 0.000 0.000 Minimum Refresh Recovery Delay Time, tRFCsb (ns) 0.000 0.000 Module Type UDIMM UDIMM Module information SPD revision 1.0 1.0 SPD present Yes Yes SPD device type SPD5118 SPD5118 SPD Manufacturer Montage Technology Group (Bank: 7, ID: 0x32) Montage Technology Group (Bank: 7, ID: 0x32) PMIC 0 present Yes Yes PMIC 0 device type PMIC5100 PMIC5100 PMIC 0 Manufacturer Richtek Power (Bank: 11, ID: 0x8C) Richtek Power (Bank: 11, ID: 0x8C) PMIC 1 present No No PMIC 1 device type PMIC 1 Manufacturer PMIC 2 present No No PMIC 2 device type PMIC 2 Manufacturer Thermal Sensor 0 present No No Thermal Sensor 1 present No No Thermal Sensor device type Thermal Sensor Manufacturer Module Height (mm) 32 32 Module Thickness Front (mm) 2 2 Module Thickness Back (mm) 1 1 Module Reference Card Raw Card A Rev. 0 Raw Card A Rev. 0 # DRAM Rows 1 1 Heat spreader installed No No Operating Temperature Range XT (0 to + 95 °C) XT (0 to + 95 °C) Rank Mix Symmetrical Symmetrical Number of Package Ranks per Channel 1 1 Number of Channels per DIMM 2 2 Primary bus width per Channel 32 bits 32 bits Bus width extension per Channel 0 bits 0 bits DRAM Manufacture ID 173 173 DRAM Manufacture Bank 1 1 DRAM Manufacture Name SK Hynix SK Hynix DRAM Stepping 4.1 4.1 SDRAM Package Type Monolithic SDRAM Monolithic SDRAM SDRAM Density Per Die 16Gb 16Gb SDRAM Bank Groups 8 8 SDRAM Banks Per Bank Group 4 4 Second SDRAM Package Type Second SDRAM Density Per Die Second SDRAM Column Address Bits Second SDRAM Row Address Bits Second SDRAM Device Width Second SDRAM Bank Groups Second SDRAM Banks Per Bank Group First SDRAM RFM RAAMMT 0X (FGR: 0X) 0X (FGR: 0X) First SDRAM RFM RAAIMT 0 (FGR: 0) 0 (FGR: 0) First SDRAM RFM Required no no First SDRAM RFM RAA Counter Decrement per REF command RAAIMT / 2 RAAIMT / 2 Second SDRAM RFM RAAMMT Second SDRAM RFM RAAIMT Second SDRAM RFM Required Second SDRAM RFM RAA Counter Decrement per REF command First SDRAM ARFM Level A RAAMMT 0X (FGR: 0X) 0X (FGR: 0X) First SDRAM ARFM Level A RAAIMT 0 (FGR: 0) 0 (FGR: 0) First SDRAM ARFM Level A supported no no First SDRAM ARFM Level A RAA Counter Decrement per REF command RAAIMT / 2 RAAIMT / 2 Second SDRAM ARFM Level A RAAMMT Second SDRAM ARFM Level A RAAIMT Second SDRAM ARFM Level A supported Second SDRAM ARFM Level A RAA Counter Decrement per REF command First SDRAM ARFM Level B RAAMMT 0X (FGR: 0X) 0X (FGR: 0X) First SDRAM ARFM Level B RAAIMT 0 (FGR: 0) 0 (FGR: 0) First SDRAM ARFM Level B supported no no First SDRAM ARFM Level B RAA Counter Decrement per REF command RAAIMT / 2 RAAIMT / 2 Second SDRAM ARFM Level B RAAMMT Second SDRAM ARFM Level B RAAIMT Second SDRAM ARFM Level B supported Second SDRAM ARFM Level B RAA Counter Decrement per REF command First SDRAM ARFM Level C RAAMMT 0X (FGR: 0X) 0X (FGR: 0X) First SDRAM ARFM Level C RAAIMT 0 (FGR: 0) 0 (FGR: 0) First SDRAM ARFM Level C supported no no First SDRAM ARFM Level C RAA Counter Decrement per REF command RAAIMT / 2 RAAIMT / 2 Second SDRAM ARFM Level C RAAMMT Second SDRAM ARFM Level C RAAIMT Second SDRAM ARFM Level C supported Second SDRAM ARFM Level C RAA Counter Decrement per REF command sPPR Granularity bank group bank group sPPR Undo/Lock supported supported Burst length 32 not supported not supported MBIST/mPPR not supported not supported mPPR/hPPR Abort not supported not supported PASR not supported not supported DCA Types Supported Device supports DCA for 4-phase internal clock(s) Device supports DCA for 4-phase internal clock(s) x4 RMW/ECS Writeback Suppression not supported not supported x4 RMW/ECS Writeback Suppression MR selector MR9 MR9 Bounded Fault not supported not supported SDRAM Nominal Voltage, VDDQ 1.1V 1.1V SDRAM Nominal Voltage, VPP 1.8V 1.8V Cyclical Redundancy Code (CRC) for Base Configuration 9d1a 9d1a XMP Attributes XMP version 3.0 3.0 PMIC Vendor ID 8A8C 8A8C Number of PMICs on DIMM 1 1 PMIC capabilities PMIC has capabilities for OC functions Yes Yes Current PMIC OC is enabled Yes Yes PMIC voltage default step size 5mV 5mV OC global reset functions No No Validation and Certification Capabilities DIMM is self-certified by DIMM vendor No No PMIC Component is validated by Intel AVL level No No XMP revision 1.2 1.2 XMP Profile 1 Profile name TG-7200-34-42-84 TG-7200-34-42-84 XMP Certified No No Recommended number of DIMMs per channel 1 1 Module VPP voltage 1.80V 1.80V Module VDD voltage 1.40V 1.40V Module VDDQ voltage 1.40V 1.40V Memory Controller voltage 1.10V 1.10V Clock speed (MHz) 3610 3610 Transfer Speed (MT/s) DDR5-7220 DDR5-7220 Bandwidth (MB/s) PC5-28800 PC5-28800 Minimum clock cycle time, tCK (ns) 0.277 0.277 Supported CAS latencies 34 34 Minimum CAS latency time, tAA (ns) 9.418 9.418 Minimum RAS to CAS delay time, tRCD (ns) 11.634 11.634 Minimum row precharge time, tRP (ns) 11.634 11.634 Minimum active to precharge time, tRAS (ns) 23.268 23.268 Supported timing at highest clock speed 34-42-42-84 34-42-42-84 Minimum Active to Auto-Refresh Delay, tRC (ns) 34.902 34.902 Minimum Write Recovery Time, tWR (ns) 30.000 30.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) 295.000 295.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) 160.000 160.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) 130.000 130.000 Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Read Command Delay Time, Same Bank Group, tCCD_L_WTR (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Read Command Delay Time, Different Bank Group, tCCD_S_WTR (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Read to Precharge Command Delay Time, tRTP (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Four Activate Window, tFAW (ns) 0.000 0.000 Advanced Memory Overclocking Features Real-Time Memory Frequency Overclocking Not supported Not supported Intel Dynamic Memory Boost Not supported Not supported System CMD Rate Mode 2N 2N Vendor Personality Byte 0x00 0x00 XMP Profile 2 Profile name TG-6000-38-38-78 TG-6000-38-38-78 XMP Certified No No Recommended number of DIMMs per channel 1 1 Module VPP voltage 1.80V 1.80V Module VDD voltage 1.25V 1.25V Module VDDQ voltage 1.25V 1.25V Memory Controller voltage 1.10V 1.10V Clock speed (MHz) 3000 3000 Transfer Speed (MT/s) DDR5-6000 DDR5-6000 Bandwidth (MB/s) PC5-24000 PC5-24000 Minimum clock cycle time, tCK (ns) 0.333 0.333 Supported CAS latencies 38 38 Minimum CAS latency time, tAA (ns) 12.654 12.654 Minimum RAS to CAS delay time, tRCD (ns) 12.654 12.654 Minimum row precharge time, tRP (ns) 12.654 12.654 Minimum active to precharge time, tRAS (ns) 25.974 25.974 Supported timing at highest clock speed 38-38-38-78 38-38-38-78 Minimum Active to Auto-Refresh Delay, tRC (ns) 38.628 38.628 Minimum Write Recovery Time, tWR (ns) 30.000 30.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) 295.000 295.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) 160.000 160.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) 130.000 130.000 Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Read Command Delay Time, Same Bank Group, tCCD_L_WTR (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Write to Read Command Delay Time, Different Bank Group, tCCD_S_WTR (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Read to Precharge Command Delay Time, tRTP (ns) 0.000 (0 nCK) 0.000 (0 nCK) Minimum Four Activate Window, tFAW (ns) 0.000 0.000 Advanced Memory Overclocking Features Real-Time Memory Frequency Overclocking Not supported Not supported Intel Dynamic Memory Boost Not supported Not supported System CMD Rate Mode 2N 2N Vendor Personality Byte 0x00 0x00 EXPO Attributes EXPO version 1.0 1.0 PMIC feature support PMIC 10 mV step size support No No EXPO Profile 1 DIMMs per channel supported 1 1 EXPO Optional Block Support Block 1 enabled Yes Yes SDRAM VDD 1.40V 1.40V SDRAM VDDQ 1.40V 1.40V SDRAM VPP 1.80V 1.80V Clock speed (MHz) 3610 3610 Transfer Speed (MT/s) DDR5-7220 DDR5-7220 Bandwidth (MB/s) PC5-28800 PC5-28800 Minimum clock cycle time, tCK (ns) 0.277 0.277 Minimum CAS latency time, tAA (ns) 9.418 9.418 Minimum RAS to CAS delay time, tRCD (ns) 11.634 11.634 Minimum row precharge time, tRP (ns) 11.634 11.634 Minimum active to precharge time, tRAS (ns) 23.268 23.268 Supported timing at highest clock speed 34-42-42-84 34-42-42-84 Minimum Active to Auto-Refresh Delay, tRC (ns) 34.902 34.902 Minimum Write Recovery Time, tWR (ns) 30.000 30.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC1 (ns) 295.000 295.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFC2 (ns) 160.000 160.000 Minimum Auto-Refresh to Active/Auto-Refresh Delay, tRFCsb (ns) 130.000 130.000 Minimum Active to Active Command Delay Time, Same Bank Group, tRRD_L (ns) 5.000 5.000 Minimum Read to Read Command Delay Time, Same Bank Group, tCCD_L (ns) 5.000 5.000 Minimum Write to Write Command Delay Time, Same Bank Group, tCCD_L_WR (ns) 20.000 20.000 Minimum Write to Write Command Delay Time, Second Write not RMW, Same Bank Group, tCCD_L_WR2 (ns) 10.000 10.000 Minimum Four Activate Window, tFAW (ns) 8.888 8.888 Minimum Write to Read Command Delay Time, Same Bank Group, tWTR_L (ns) 10.000 10.000 Minimum Write to Read Command Delay Time, Different Bank Group, tWTR_S (ns) 2.500 2.500 Minimum Read to Precharge Command Delay Time, tRTP (ns) 7.500 7.500

Die Hersteller wie Gskill, Teamgroup, etc. kaufen ihre ICs in großen Trays ein (--> so günstig wie möglich) und binnen diese selber.

Das 5600er Profil von Teamgroup entspricht keiner JEDEC Norm und ist deshalb selbst von Teamgroup definiert.

Du müsstest dein Heatsink abmachen und schauen, ob der IC ein Class V oder A ist. Das kann etwas über die Qualität sagen, bei den Mengen was aber zurzeit im Umlauf sind oder auch die letzten Jahre gebinnt wurde, muss es das aber nicht.

6000C26 ob 16GB oder 24Gb sind beides Class V. Evtl. gibt es da draußen noch Class A die noch besser sind, der Yield ist aber so klein das sich ein Verkauf nichtmal lohnen würde.

Kurzgesagt: selber binnen und bewerten. Was im SPD steht, ist egal.

Beitrag automatisch zusammengeführt:

FCLK mit P95 oder YCruncher testen. Dann hast du eine Aussage über die Stabilität.fclk auf 2500 mit sehr moderater vsoc mit einem 8400f.

habe ich bisher nicht so oft gesehen, nur deshalb mal gezeigt.

Anhang anzeigen 1127003

Anhang anzeigen 1127005

hci memtest stabil. das setting ist nicht tm5 getestet.

bei den tm5 90 min testversuchen hatte ich dreimal erfolg, jedoch mit anderen 6200er settings. alle weiteren versuche endeten mit einem späten error alle nach >50 min und bei >50°C. ich interpretiere das als temp-grenze bei ansonsten stabilen settings. wie auch immer, ich lass das vorerst so laufen...

Meist wenn TM5 spät Fehler wirft liegt es an einem tick zu wenig VDD. Also um 0.01V anpassen. VDDIO unter 1,1V macht keinen Sinn. Es ist lediglich die I/0 Spannung -> gleiches gilt auf Mem Seite für VDDQ. Zu niedrig = weniger Performance.

Spannungen erst dann Anpassen, wenn das Setup stabil ist und nicht während man FCLK oder Timings anpasst. -> Zu viele Stellschrauben = mühsame Fehlersuche

Zuletzt bearbeitet:

- Mitglied seit

- 16.09.2004

- Beiträge

- 430

Hi,

welchen RAM würdet Ihr kaufen, rein von der Leistung:

Kingston Fury Renegade RGB KF580C36RLAK2-48

G.Skill Trident Z5 NEO RGB F5-6000J2636H24GX2-TZ5NRW leider aktuell nicht kaufbar.

Aktuell habe ich ein 9800x3D mit Asus B650E-E Board. Würde der Fury da auch 6000MHz@CL26 bzw 28 packen?.

Vermutlich ist der besser da er neuer ist oder?

THX

welchen RAM würdet Ihr kaufen, rein von der Leistung:

Kingston Fury Renegade RGB KF580C36RLAK2-48

G.Skill Trident Z5 NEO RGB F5-6000J2636H24GX2-TZ5NRW leider aktuell nicht kaufbar.

Aktuell habe ich ein 9800x3D mit Asus B650E-E Board. Würde der Fury da auch 6000MHz@CL26 bzw 28 packen?.

Vermutlich ist der besser da er neuer ist oder?

THX

- Mitglied seit

- 20.01.2017

- Beiträge

- 4.818

- Ort

- am Rhein

- Desktop System

- Gaming | Büro

- Laptop

- MacBook Air M2

- Details zu meinem Desktop

- Prozessor

- 9800X3D | 7950X

- Mainboard

- X870E Nova | B850 Steel Legend

- Kühler

- Freezer 36 | Core 1 + SuperNova

- Speicher

- 6400-26 | 6200-28

- Grafikprozessor

- 6900 LC | 9070 XT

- Display

- LG 55 Zoll 4K | 3440x1440 + 2560x1440

- Gehäuse

- Fractal North | BQ Silent Base 802

- Netzteil

- BQ 1000W | Corsair 1000W

Das ist ja mal garkeine sinnvolle Schlussfolgerung.Vermutlich ist der besser da er neuer ist oder?

Zunächst ist mal die Frage, ob du 1:1, also 6000er oder 2:1, also 8000er willst.

6000-30 schaffen beide und der Rest hängt viel mehr von deiner CPU als den Riegeln ab.

Ich würd immer zum GSkill greifen, weil der den besseren Spannungscontroller hat. Und die 6000-26 sind schon sehr gute Riegel, wähend 8000er Abenteuer beim Ryzen nicht so viel (mehr) bringen.

Ähnliche Themen

- Antworten

- 24

- Aufrufe

- 2K

- Antworten

- 80

- Aufrufe

- 10K

- Antworten

- 29

- Aufrufe

- 3K