Werbung

Auf dem VLSI-Symposium in Japan hat Intel weitere Leistungsdaten zur ab der zweiten Jahreshälfte 2025 in die Massenproduktion übergehende Fertigung in Intel 18A präsentiert. Man könnte davon sprechen, dass Intel mit Intel 18A "All in" geht – zumindest wenn es um das Auftragsfertiger-Geschäft geht. Allerdings zeichnete sich zuletzt an, dass nicht Intel 18A, sondern wohl eher der Optimierungsschritt Intel 18A-P und der Nachfolger Intel 14A die größere Hoffnung ist, während Intel 18A allenfalls für die eigenen Produkte wichtig ist.

Vor einem Jahr präsentierte Intel die Details zur Fertigung in Intel 3 und verglich diese mit Intel 4 und Intel 7. Hier erstmals zum Einsatz kam die EUV-Fertigung – zumindest für einige wenige Lagen. Zusammen mit der nächsten Transistoren-Generation GAA-Transistoren (Gate all around) und der rückseitigen Stromversorgung (BSPDN, Backside Power Delivery Netwerk) PowerVia soll die Fertigung in Intel 18A der größte Schritt sein, den Intel in den vergangenen Jahren gemacht hatte.

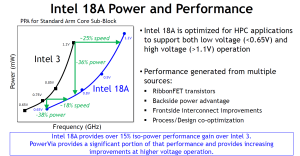

In der für die Industrie üblichen PPA (Power, Performance, Aera) für einen Sub-Block eines ARM-Kerns präsentiert Intel ein Frequenze/Leistungsdiagramm. In diesem werden für verschiedene Spannungen die erreichten Frequenzen sowie die Leistungsaufnahme aufgeführt.

Laut Intel hat man den 18A-Prozess für HPC-Applikationen und niedrige Spannungen optimiert. Gegenüber der Fertigung in Intel 3 sieht Intel eine ISO-normierte Leistungsverbesserung im Bereich von 15 %. Je nach Spannungsbereich sind bei gleicher Spannung (1,1 V) aber auch ein um 25 % höherer Takt möglich oder die Leistungsaufnahme geht bei gleicher Leistung um 38 % zurück. Für etwa 0,75 V spricht Intel von einer um 18 % höheren Leistung oder eine um 38 % niedrigere Leistungsaufnahme.

Neben den Verbesserungen durch die GAA-Transistoren und rückseitige Versorgung mittels PowerVia beschreibt Intel Optimierungen bei den Frontside-Interconnects und Prozess/Design Co-Optimierungen.

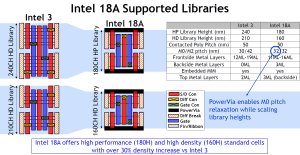

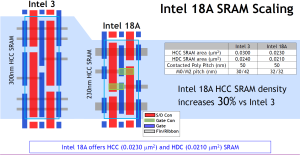

Mitsamt der neuen Fertigung gibt es neue Zellen, in denen sich die Transistoren in bestimmten Strukturen befinden. Wie immer gibt es sogenannte Performance- und High-Density-Zellen, die in etwa 30 % kleiner als in Intel 3 ausfallen.

| Intel 4 | Intel 3 | Intel 18A | |

| Höhe HP-Zelle | 240 nm | 240 nm | 180 nm |

| Höhe HD-Zelle | - | 210 nm | 160 nm |

| Poly Pitch | 50 nm | 50 nm | 50 nm |

| M0/M2 Pitch | 30/45 nm | 30/42 nm | 32/32 nm |

| Frontseitige Metalllagen | 14 bis 21 | 12 bis 19 | 11 bis 16 |

| Rückseitige Metalllagen | 0 | 0 | 3 |

| Integierter MIM | Ja | Ja | Ja |

| Top-Metalllagen | 2 | 2 | 3 (rückseitig) |

Aufgrund der rückseitigen Stromversorgung verfügen die in Intel 18A gefertigten Zellen über rückseitigen Metalllagen. Dadurch ist Intel beispielsweise in der Lage, in der obersten Metalllage (M0) den Abstand von 30 auf 32 µm zu entspannen. Dies macht es in der Fertigung natürlich etwas einfacher und ist weniger fehleranfällig. Dies ist eines der Hauptargumente für eine rückseitige Stromversorgung.

Neuer Aufbau der Metalllagen

Durch die rückseitige Stromversorgung gibt es im Metallstack einen völlig neuen Aufbau. Im Anschluss vergleichen wir diesen und ziehen dazu die Performance-Variante von Intel 3 mit 21 Metalllagen und Intel 18A mit 22 Metalllagen heran. Für Intel 18A gibt es drei Varianten: Eine auf Kosten optimierte Variante mit 17 Metalllagen, eine ausgewogene Variante mit 21 Metalllagen und eine Performance-Variante mit 22 Metalllagen.

| Lage | Pitch in Intel 7 | Pitch in Intel 4 | Pitch in Intel 3 (21ML) | Pitch in Intel 18A (22ML) |

| Kontakt-Gate | 54 nm | 50 nm | 50 nm | |

| M0 | 40 nm | 30 nm | 30 nm | 32 nm |

| M1 | 36 nm | 50 nm | 50 nm | 50 nm |

| M2 | 44 nm | 45 nm | 42 nm | 32 nm |

| M3 | 52 nm | 50 nm | 50 nm | 40 nm |

| M4 | 52 nm | 45 nm | 42 nm | 40 nm |

| M5 | 84 nm | 60 nm | 60 nm | 80 nm |

| M6 | 84 nm | 60 nm | 60 nm | 80 nm |

| M7 | 84 nm | 84 nm | 84 nm | 80 nm |

| M8 | 112 nm | 84 nm | 84 nm | 80 nm |

| M9 | 112 nm | 98 nm | 84 nm | 80 nm |

| M10 | 160 nm | 98 nm | 84 nm | 80 nm |

| M11 | 160 nm | 130 nm | 98 nm | 120 nm |

| M12 | 160 nm | 130 nm | 98 nm | 120 nm |

| M13 | 160 nm | 160 nm | 130 nm | 160 nm |

| M14 | 400 nm | 160 nm | 130 nm | 160 nm |

| M15 | - | 280 nm | 160 nm | 280 nm |

| M16 | - | - | 160 nm | - |

| M17 | - | - | 280 nm | - |

| M18 | - | - | 280 nm | - |

| (G)M0 | 1.080 nm | 1.080 nm | 1.080 nm | - |

| (G)M1 | 11 µm | 4 µm | 4 µm | - |

| PowerVia | - | - | - | 160 nm |

| BM0 | - | - | - | 160 nm |

| BM1 | - | - | - | 300 nm |

| BM2 | - | - | - | 480 nm |

| BM3 | - | - | - | 1.080 nm |

| BM4 | - | - | - | 1.080 nm |

| BM5 | 4 µm |

Während die M0-Metalllage entspannter gestaltet werden kann, sind die Abstände in den Lagen M1 bis M10 enger, entspannen sich aber in M11 bis M15. Die rückseitige Versorgung kommt erst ab Intel 18A zum Einsatz. Entsprechend sehen wir erst hier die Abstände für die PowerVia sowie die rückseitigen Lagen BM0 bis BM5.

Laut Intel kommt die Belichtung mittels EUV für die Metalllagen M0 bis M4 zum Einsatz. Durch den Einsatz reduziert sich der Einsatz der notwendigen Masken um 44 %, was sich in deutlich weniger Schritten in der Fertigung zeigt.

Erster Einsatz in sparsamen Chips

Der erste Einsatz von Intel 18A ist für das Compute-Chiplet von Panther Lake vorgesehen. Auch die kommende "Xeon 7"-Generation rein mit Efficiency-Kernen alias Clearwater Forest, wird in Intel 18A hergestellt. Ab wann sich der Fokus auf die "Hochleistungsprodukte" wie zum Beispiel die Desktop-Prozessoren verschiebt, ist nicht bekannt.