Werbung

Bereits mit dem ersten Auftauchen der X3D-Technologie, die AMD dann später als 3D V-Cache vermarktet hat, deutete sich an, dass AMD die Größe des Caches über ein Stapeln mehrerer Schichten skalieren kann. Inzwischen sind die Prozessoren mit zusätzlichem Cache zu einem wichtigen Merkmal in AMDs Prozessor-Portfolio geworden. In der nächsten Generation der Ryzen- und EPYC-Prozessoren soll es nun soweit sein. Dies berichtet Moore's Law is Dead, dessen Meldungen meist mit Vorsicht zu genießen sind, der in einigen Details aber auch immer mal wieder richtig liegt.

Dass AMD an einem stapelbaren 3D V-Cache arbeitet, hatten wir bereits Anfang 2021 enthüllt, denn im BIOS eines Servers der EPYC-7003-Serie (Milan) entdeckten wir eine Option namens "X3D" und dort die Möglichkeit den X3D-Stack mit einen, zwei oder vier Stacks anzusprechen. Bereits damals war klar: AMD arbeitet an einem stapelbaren 3D V-Cache.

Mit den CCDs für Zen 6 soll die Anzahl der Kerne auf derer zwölf ansteigen. 50 % mehr Kerne sollen auch mit 50 % mehr Cache einhergehen. Die Kapazität des direkt im CCD vorhandenen L3-Cache steigt von 32 auf 48 MB an. Dies gilt auch für den 3D V-Cache, der in der einfachen Ausführung von 64 auf 96 MB anwächst. Mit zwei Lagen sollen es dann 192 MB sein.

Theoretisch besteht also die Möglichkeit, dass AMD einen Ryzen-Prozessor mit zwölf Kernen und 240 MB (48 + 192 MB) auf den Markt bringt. Ob sich derart viel Cache bei einem Gaming-Prozessor lohnt, ist jedoch fraglich. Hier dürften für AMD auch wirtschaftliche Aspekte zum Tragen kommen. So blieb es bis heute dabei, dass bei den Ryzen-9000-Prozessoren mit zwei CCDs nur eines davon mit dem zusätzlichen Cache ausgestattet wurde. So könnte es am Ende dazu kommen, dass AMD den gestapelten 3D V-Cache nur bei den EPYC-Prozessoren zum Einsatz bringt.

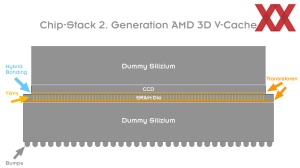

Mit den Ryzen-9000X3D-Prozessoren ging AMD den nächsten Schritt für die 3D-V-Cache-Technologie und platziert den SRAM-Chip unter dem CCD mit seinen Kernen. Durch die Platzierung des SRAM-Chips unter dem CCD ist kein Füller-Chiplet mehr notwendig, welches für einen höheren thermischen Widerstand gesorgt hat. Dieser soll zum Beispiel beim Ryzen 7 9800X3D (Test) um 47 % geringer ausfallen, da der CCD direkt mit dem Heatspreader in Kontakt gebracht wird. Weitere Details zum Aufbau findet ihr in unserem Artikel zu diesem Thema.

Die aus dem neuen Aufbau resultierenden, niedrigeren Temperaturen, sorgen dafür, dass AMD einen um 300 MHz höheren Boost-Takt und einen um 500 MHz höhere Basis-Takt für den Ryzen 7 9800X3D anlegen kann. Zudem legt die TjMax nun nicht mehr bei 89 °C, sondern bei 95 °C wie bei den weiteren Prozessoren der Ryzen-9000-Prozessoren, sodass der Prozessor mehr Spielraum bekommt seine Maximalleistung abzurufen.

Inwieweit sich Änderungen im Aspekt der Kühlung durch den gestapelten 3D V-Cache ergeben, lässt sich aktuell noch kaum abschätzen.

2026 werden wir schlauer sein, denn dann sollen die Prozessoren mit den Zen-6-Kernen und dem geänderten CCD-Design auf den Markt kommen. Für die nächste EPYC-Generation Venice setzt AMD auf bei TSMC in 2 nm gefertigte CCDs, womit auch die Fertigung der SRAM-Lagen einen Schritt in eine kleinere Prozessgröße machen dürften.