News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Venice

-

Bis zu 60 Milliarden USD: Meta kauft Custom MI450, Helios Racks, Venice- und Verano-CPUs

AMDs Aufwind im Datacenter-Geschäft geht weiter. Nach der letztjährigen Ankündigung durch OpenAI und AMD, man wolle 6 GW an Leistung installieren, folgt nun Meta mit einer Ankündigung in gleicher Größe. Das erste Gigawatt an installierter Leistung soll bereits in der zweiten Jahreshälfte folgen. OpenAI erwartet die ersten Racks mit den Instinct-MI450-Beschleunigern ebenfalls in diesem Zeitraum, auch wenn es in der vergangenen Woche daran... [mehr]

AMDs Aufwind im Datacenter-Geschäft geht weiter. Nach der letztjährigen Ankündigung durch OpenAI und AMD, man wolle 6 GW an Leistung installieren, folgt nun Meta mit einer Ankündigung in gleicher Größe. Das erste Gigawatt an installierter Leistung soll bereits in der zweiten Jahreshälfte folgen. OpenAI erwartet die ersten Racks mit den Instinct-MI450-Beschleunigern ebenfalls in diesem Zeitraum, auch wenn es in der vergangenen Woche daran... [mehr] -

2026 geht AMD in den Angriffsmodus: Details zur Instinct MI400-Familie

AMD nutzte des CES nicht nur zur Vorstellung des Ryzen 7 9850X3D, oder der neuen Ryzen-AI- und Ryzen-AI-MaxProzessoren, sondern auch um seine Strategie für das Datacenter-Geschäft noch einmal aufzuzeigen. Hier steht mit dem Epyc-Prozessoren auf Basis der Zen-6-Architektur (Venice) und der Instinct-MI400-Serie in diesem Jahr ein größerer Sprung an. Dieser soll AMD in die Lage versetzen auf Augenhöhe mit NVIDIA zu operieren. Dabei wird nun... [mehr]

AMD nutzte des CES nicht nur zur Vorstellung des Ryzen 7 9850X3D, oder der neuen Ryzen-AI- und Ryzen-AI-MaxProzessoren, sondern auch um seine Strategie für das Datacenter-Geschäft noch einmal aufzuzeigen. Hier steht mit dem Epyc-Prozessoren auf Basis der Zen-6-Architektur (Venice) und der Instinct-MI400-Serie in diesem Jahr ein größerer Sprung an. Dieser soll AMD in die Lage versetzen auf Augenhöhe mit NVIDIA zu operieren. Dabei wird nun... [mehr] -

Fire Range und Venice: AMD verrät Details zukünftiger Prozessoren

Über das eigene Technical Information Portal verrät AMD einige Details zu den zukünftigen Prozessoren. Genannt wird unter anderem der Embedded "Fire Range" (Epyc Embedded 2005 Series) Embedded "Venice" (Epyc Embedded). Anhand des Codenamens "Fire Range" verwenden die Prozessoren der Embedded 2005 Series offenbar das gleiche Design wie die Ryzen-9000HX- und -HX3D-Prozessoren für Notebooks. Zudem werden bis zu 16 Zen-5-Kerne,... [mehr]

Über das eigene Technical Information Portal verrät AMD einige Details zu den zukünftigen Prozessoren. Genannt wird unter anderem der Embedded "Fire Range" (Epyc Embedded 2005 Series) Embedded "Venice" (Epyc Embedded). Anhand des Codenamens "Fire Range" verwenden die Prozessoren der Embedded 2005 Series offenbar das gleiche Design wie die Ryzen-9000HX- und -HX3D-Prozessoren für Notebooks. Zudem werden bis zu 16 Zen-5-Kerne,... [mehr] -

Supercomputer am HLRS: Auch Herder setzt auf Instinct MI430X und AMD Epyc Venice

Im Januar diesen Jahres ging das Übergangssystem Hunter am HLRS (Höchstleistungsrechenzentrum Stuttgart) in Stuttgart in Betrieb. Wir konnten das System im Sommer besuchen und uns einen Eindruck davon verschaffen, wie man sich in Stuttgart auf den Nachfolger Herder vorbereitet, der ab Ende 2027 wieder eine Spitzenposition einnehmen soll. Bisher hatte das HLRS nicht enthüllt, welche Hardware für Herder zum Einsatz kommen wird. Doch nun hat... [mehr]

Im Januar diesen Jahres ging das Übergangssystem Hunter am HLRS (Höchstleistungsrechenzentrum Stuttgart) in Stuttgart in Betrieb. Wir konnten das System im Sommer besuchen und uns einen Eindruck davon verschaffen, wie man sich in Stuttgart auf den Nachfolger Herder vorbereitet, der ab Ende 2027 wieder eine Spitzenposition einnehmen soll. Bisher hatte das HLRS nicht enthüllt, welche Hardware für Herder zum Einsatz kommen wird. Doch nun hat... [mehr] -

Alice Recoque Supercomputer: Zweites europäisches Exascale-System kommt mit AMD-Hardware

AMD, das französische Forschungsinstitut GENCI sowie die Atombehörde CEA in Frankreich haben den Bau des zweiten europäischen Exascale-Supercomputers namens Alice Recoque angekündigt. Erst heute wurde die aktualisierte Liste der Top500 der Supercomputer veröffentlicht, in welcher der Jupiter Booster nicht nur den vierten Platz belegt, sondern mit einer Rechenleistung von 1.000 PFLOPS auch das schnellste europäische System darstellt... [mehr].

AMD, das französische Forschungsinstitut GENCI sowie die Atombehörde CEA in Frankreich haben den Bau des zweiten europäischen Exascale-Supercomputers namens Alice Recoque angekündigt. Erst heute wurde die aktualisierte Liste der Top500 der Supercomputer veröffentlicht, in welcher der Jupiter Booster nicht nur den vierten Platz belegt, sondern mit einer Rechenleistung von 1.000 PFLOPS auch das schnellste europäische System darstellt... [mehr]. -

Lux und Discovery: Zwei neue Supercomputer mit AMD-Hardware von HPE für das ORNL

HPE und das Oak Ridge National Laborator (ORNL) verkünden, dass man auf Basis des Cray Rackdesigns GX500 und Storage Systems K3000 zwei neue Exascale-Supercomputer aufbauen werde. Die Basis-Hardware beider Systeme wird von AMD kommen. Lux, so der Name eines der Systeme, soll für KI-Anwendungen besonders flexibel einsetzbar sein. Discovery hingegen, das zweite System, ist ein Next-Gen-Supercomputer, der HPC- und KI miteinander kombiniert. Zur... [mehr]

HPE und das Oak Ridge National Laborator (ORNL) verkünden, dass man auf Basis des Cray Rackdesigns GX500 und Storage Systems K3000 zwei neue Exascale-Supercomputer aufbauen werde. Die Basis-Hardware beider Systeme wird von AMD kommen. Lux, so der Name eines der Systeme, soll für KI-Anwendungen besonders flexibel einsetzbar sein. Discovery hingegen, das zweite System, ist ein Next-Gen-Supercomputer, der HPC- und KI miteinander kombiniert. Zur... [mehr] -

OCP Summit: Epyc Venice bis 1.400 W und Packages zukünftig mit mehreren Kilowatt

Am 5. und 6. August hat in Taiwan die asiatische Ausgabe des OCP Summit stattgefunden. In gleich mehreren Präsentationen finden sich dabei einige interessante Annahmen und Projektionen, wie die Kühlung zukünftiger CPU- und GPU-Packages umgesetzt werden soll. Während die Thermal Design Power (TDP) bei den Server-Prozessoren sowohl bei AMD, wie auch Intel, aktuell bei maximal etwa 500 W festgesetzt ist, dürfen sich die KI-Beschleuniger... [mehr]

Am 5. und 6. August hat in Taiwan die asiatische Ausgabe des OCP Summit stattgefunden. In gleich mehreren Präsentationen finden sich dabei einige interessante Annahmen und Projektionen, wie die Kühlung zukünftiger CPU- und GPU-Packages umgesetzt werden soll. Während die Thermal Design Power (TDP) bei den Server-Prozessoren sowohl bei AMD, wie auch Intel, aktuell bei maximal etwa 500 W festgesetzt ist, dürfen sich die KI-Beschleuniger... [mehr] -

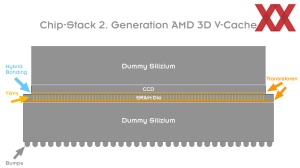

Zen 6 mit 3D V-Cache: AMD soll Cache in zwei Schichten stapeln

Bereits mit dem ersten Auftauchen der X3D-Technologie, die AMD dann später als 3D V-Cache vermarktet hat und inzwischen zu einem wichtigen Merkmal in AMDs Prozessor-Portfolio geworden ist, deutete sich an, dass AMD die Größe des Caches über ein Stapeln mehrerer Schichten skalieren kann. In der nächsten Generation der Ryzen- und EPYC-Prozessoren soll es nun soweit sein. Dies berichtet Moore's Law is Dead, dessen Meldungen... [mehr]

Bereits mit dem ersten Auftauchen der X3D-Technologie, die AMD dann später als 3D V-Cache vermarktet hat und inzwischen zu einem wichtigen Merkmal in AMDs Prozessor-Portfolio geworden ist, deutete sich an, dass AMD die Größe des Caches über ein Stapeln mehrerer Schichten skalieren kann. In der nächsten Generation der Ryzen- und EPYC-Prozessoren soll es nun soweit sein. Dies berichtet Moore's Law is Dead, dessen Meldungen... [mehr] -

AMD EPYC Venice: AMD und TSMC zeigen in N2 gefertigten CCD mit Zen-6-Kernen

Aktuell bereist AMD-CEO Lisa Su Taiwan, um unter anderem TSMC, einen der zentralen Fertigungspartner, zu treffen. Im Rahmen eines gemeinsamen Events wurde bestätigt, dass die CCDs der kommenden EPYC-Generation "Venice" (Zen 6) im 2-nm-Prozess (N2) mit GAA-Nanosheet-Transistoren gefertigt werden. Laut AMD und TSMC zählen die Zen-6-basierten CCDs zu den ersten HPC-Dies, die im N2-Node in die Serienproduktion überführt werden. Die N2-Fertigung... [mehr]

Aktuell bereist AMD-CEO Lisa Su Taiwan, um unter anderem TSMC, einen der zentralen Fertigungspartner, zu treffen. Im Rahmen eines gemeinsamen Events wurde bestätigt, dass die CCDs der kommenden EPYC-Generation "Venice" (Zen 6) im 2-nm-Prozess (N2) mit GAA-Nanosheet-Transistoren gefertigt werden. Laut AMD und TSMC zählen die Zen-6-basierten CCDs zu den ersten HPC-Dies, die im N2-Node in die Serienproduktion überführt werden. Die N2-Fertigung... [mehr]