Werbung

Neben der Fertigung von Chips in den aktuellsten Herstellungsprozessen gehört das Advanced Packaging zu den Aushängeschildern von TSMC und ist für die allermeisten Chips auch unabdingbar. Entsprechend baut TSMC nicht nur die Kapazitäten seiner Fabs weitreichend aus, sondern auch die für das Advanced Packaging. Auf die Weiterentwicklungen in diesem Bereich kommen wir später.

Im Rahmen des Advanced Packaging und der Integration von HBM4 wird den Base-Dies eine wichtige Rolle zukommen. Diese werden nicht mehr von den Speicherherstellern wie Micron, Samsung und SK Hynix hergestellt werden. Stattdessen wird es hier standardkonforme Base-Dies geben, die relativ einfach integriert werden können.

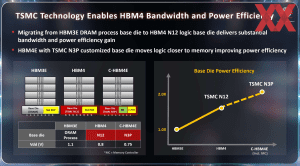

Aber schon mit den Base-Dies soll es Verbesserungen geben, da nicht mehr ein DRAM-Standardprozess, sondern mit N12 ein vermeintlich weitaus fortschrittlicher Prozess zum Einsatz kommt. Untermalt wird dies seitens TSMC mit der Angabe einer von 1,1 auf 0,8 V reduzierten Betriebsspannung. Dies soll die Effizienz um den Faktor 1,5 steigern. Für HBM4 kommt noch ein Standard-PHY, also ein standardisiertes physikalisches Interface, zum Einsatz.

HBM4E bzw. C-HBM4E soll dann einen großen Sprung auf N3P machen. Neben einer weiteren Reduzierung der Spannung von 0,8 auf 0,75 V spricht TSMC von einer Steigerung der Effizienz um den Faktor zwei gegenüber dem aktuellen DRAM-Prozess. Zudem verfügt der Base-Die auch über die Speichercontroller, die sich sonst im Chip befinden, an den der HBM angebunden wird. Entsprechend ist das physikalische Interface (PHY) ebenfalls eine spezifische Lösung.

HBM4 wird erstmals mit den KI-Beschleunigern wie der Instinct-MI400-Serie von AMD und der Rubin-Generation von NVIDIA zum Einsatz kommen. Für die Beschleuniger von AMD werden Kapazitäten von 432 GB bei einer Speicherbandbreite von 19,6 TB/s erreicht. NVIDIA wird mit der Rubin-Generation ebenfalls 20 TB/s erreichen.

TSMC zu CoWoS, SoIC und SoW als Packaging-Optionen

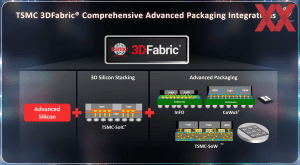

Zum Advanced Packaging zählen CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer). Letzteres findet beispielsweise bei Cerebras Anwendung und wird mit SoW-P und SoW-X weiterentwickelt. InFO dient als direkte Chip-Verbindung über eine Brücke – AMD nutzt dies bei Instinct-Beschleunigern. Mit InFO-POP und InFO-2.5D will TSMC mehr Flexibilität im Chipdesign ermöglichen, was allerdings zu höherer Komplexität führt.

CoWoS bleibt das Kerngeschäft und kombiniert Compute-Chiplets mit bis zu acht HBM-Chips. Die Entwicklung begann 2016 mit CoWoS-S bei 1,5-fachem Reticle-Limit und vier HBM-Chips in N16-Fertigung. Heute erreicht CoWoS-S ein 3,3-faches Reticle-Limit mit acht HBM-Chips und N5/N4-Fertigung. CoWoS-R bietet höhere Interconnect-Bandbreiten und unterstützt N3-Chips. Die nächste Generation CoWoS-L ermöglicht ein 5,5-faches Reticle-Limit (ca. 4.500 mm²) mit bis zu 12 HBM3E/HBM4-Chips – zugeschnitten auf KI-Beschleuniger wie AMDs Instinct MI450X und NVIDIAs Vera Rubin für 2026. Für 2027 ist CoWoS-L mit A16-Fertigung, 9,5-fachem Reticle-Limit und über 12 HBM-Chips geplant.

3D-Stacking mit SoIC gewinnt an Bedeutung. Der 3D V-Cache demonstriert bereits die Möglichkeit, SRAM-Chips über oder unter Compute-Chiplets zu platzieren. Aktuell werden N4-auf-N5-Konfigurationen mit einem Bump-Pitch von 6 µm gefertigt, wobei die Chipgrößen von 0,4 auf 0,8-faches Reticle-Limit gewachsen sind. Ab diesem Jahr startet TSMC SoIC mit N3 auf N4, wobei Chips theoretisch jeweils 830 mm² erreichen können – ohne Größenbeschränkung für den oberen Chip.

Für TSMC ist es in der Zusammenarbeit mit den Partnern und Kunden wichtig, dass man solche komplexen Strukturen im 2.5D/3D-Packaging möglichst einfach umschreibt bzw. mit einer eindeutigen Definition versieht. Die von TSMC entwickelte "3Dblox"-Sprache ermöglicht es, hierarchische Konstruktionen innerhalb des Chip-Designs zu definieren und zu strukturieren, sodass diese Konstrukte mehrfach wiederverwendet werden können. Durch dieses Prinzip der Hierarchisierung und Modularisierung ist eine einmalige Verifikation ausreichend. So muss etwa der Interface-Check – beispielsweise, ob alle µBumps korrekt verdrahtet sind – nur einmal erfolgen. Anschließend kann dieser geprüfte Block beliebig oft im Design eingesetzt werden, ohne eine erneute Überprüfung zu benötigen.

Eine weitere wichtige Funktion im Framework von 3Dblox ist die Inter-Chiplet-Verification mittels Design Rule Checking (DRC), das durch Layer Projection durchgeführt wird. Dabei wird geprüft, ob die Entwurfsrichtlinien auch beim Zusammenspiel mehrerer Chiplets eingehalten werden.

Bei großen Packages in modernen, hochintegrierten Chips müssen heute bereits über 100 Millionen µBumps platziert und korrekt verdrahtet werden. Die Komplexität steigt mit fortschreitender Miniaturisierung: Während der Bump Pitch – also der Abstand zwischen den Kontaktpunkten – bislang bei etwa 9 µm lag, wird inzwischen ein Pitch von nur 5 µm für Chiplets angestrebt. Beispielhaft hierfür sind verschiedene Packaging-Technologien: CoWoS-S arbeitet mit rund 15 Millionen Bumps, CoWoS-L kommt auf etwa 50 Millionen, während SoW- (System on Wafer) Lösungen sogar bis zu 400 Millionen Bumps benötigen.

Die Vielfalt der eingesetzten Strukturkomponenten – Substrate, Interposer und SoC – bringt unterschiedliche Bump Pitches mit sich. Damit im 3D-Stacking eine korrekte Zuteilung der Verbindungen gewährleistet ist, muss die Ausrichtung der beteiligten Ebenen präzise angepasst werden. Im Physical Design, insbesondere im Floorplanning, werden die Design-Blöcke mit einem spezifischen 3D-Bump-Muster assoziiert. Dadurch lassen sich diese Blöcke von der obersten SoC-Ebene schrittweise bis hinunter auf das Substrat ableiten. Kommt es während des Designprozesses zu Änderungen im Floorplan, können die bereits überprüften und zugeordneten Design-Blöcke flexibel übernommen werden, wodurch sich Anpassungen effizient und konsistent umsetzen lassen.

Zu den drei Säulen von TSMC, dem Advanced Silicon, Stacking und Packaging, haben wir einen gesonderten Beitrag verfasst.