Meine Erkenntnisse aus den letzten Wochen harter Arbeit an meiner Kombination:

Ja RAM hat Einfluss auf die Bus Systeme D2D und NGU. Sowohl RAM als auch die Bus Systeme haben Einfluss auf die Latenz, auch auf die messbare Cache Latenz.

Warum geht NGU und D2D nicht mehr so hoch, wenn der RAM gezwirbelt wird?

Ganz einfach: Der RAM lastet den BUS aus. Somit wird der BUS erst dann richtig belastet.

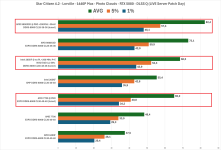

Im Chat verlauf hier, hatte ich schon 4,2 GHz Synchron D2D zu Cache zu NGU gezeigt. RAM war aber lahm.

Beim RAM kann man so genannte Race Conditions erzeugen, bei denen besonders viel vom RAM kommt. Besonders Write to Read und Read to write sind da kritisch.

Es bedarf also genauer Abwägung, wie man vorgehen möchte. Ich verfolge gerade den Ansatz mit niedriger tFAW (32-40) diese Race Conditions zu erzeugen und dann mit der CPU abzufangen.

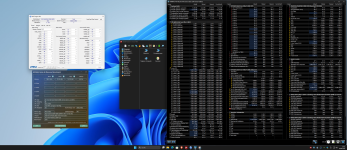

Seit ich diese Race Conditions erzeuge, geht da richtig was, jedoch kommt der IMC nicht hinterher. Hier versuche ich gerade Timings zu lockern, um das wieder stabil zu bekommen.

D2D und NGU habe ich momentan auf 3,5 GHz gesenkt und muss richtig Spannung rein klotzen. Trotzdem habe ich ab dem zweiten Durchgang TM5 Fehler. Den RAM selbst habe ich mit niedrigen NGU und D2D bereits getrennt getestet. Da war es so weit okay - manchmal.

Somit stimmt es, dass RAM und BUS Systeme stark zusammen hängen. Ring nicht vergessen. Es kann sogar sein, dass ein Setup durch REDUKTION des Rings wieder instabil wird, wenn man das so macht.

Ich hatte weiter oben geschrieben, dass meine Kerne nicht stabil werden. Das stimmt so nicht, es ist der Zusammenhang Ring, D2D, NGU und RAM.

Weitere Erkenntnisse: IMC >1,45V und VccSA > 1,38V ist kritisch, VnnAON muss schon bei 1,0V/3,5 GHz sein, wenn D2D ausgelastet wird.