br0da

Experte

Thread Starter

- Mitglied seit

- 31.12.2016

- Beiträge

- 455

Mainboard VRM Guide

Letztes Update: 11.08.2018

Inhalt

- VRM Aufbau und Funktion

[*]VRMs in der Praxis

[*]Verluste und Belastbarkeit von VRMs

[*]FAQ

[*]Links

Die leistungsstarken VRMs auf ATX Mainboards basieren auf dem Prinzip des Abwärtswandlers (englisch: buck converter oder auch step-down converter). Seine Funktionsweise besteht darin, eine Gleichspannung mittels eines Schalters zu zerhacken und das daraus resultierende Rechtecksignal wieder zu glätten. Hinter dem Filterglied zur Glättung stellt sich dann die gewünschte Gleichspannung ein, die dem Prinzip entsprechend stets kleiner als die Eingangsspannung sein muss.

Folgende elektrische Bauteile werden typischer Weise auf ATX Mainboards eingesetzt, um einen solchen Wandler umzusetzen:

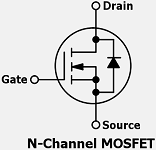

Transistoren gelten als die zur Zeit wichtigsten Bauteile der Elektronik. Sie sind Schalter, mit denen Schaltkreise gesteuert werden können. Üblicher Weise kommen so genannte n-Kanal Feld-Effekt Transistoren in VRMs für ATX Mainboards zum Einsatz. Kurz herunter gebrochen bestehen diese aus einem Halbleiter-Stromkanal, dessen Widerstand durch ein elektrisches Feld gesteuert wird. Besagter Stromkanal entsteht zwischen den beiden Elektroden Source (=Quelle) und Drain (=Senke), durch das vom Halbleitermaterial elektrisch isolierte Gate (=Tor) wird die Steuerung per Spannung vorgenommen, da bekanntlich mit jeder elektrischen Spannung ein elektrisches Feld einher geht. Source und das p-dotierte Halbleitersubstrat werden elektrisch verbunden, da ein Potentialunterschied zwischen Source und Substrat die elektrischen Eigenschaften des gesamten FETs verändern kann. Diese Verbindung nennt man Inversdiode (oder body diode) und dem entsprechend wird sie im Schaltsymbol als Diode eingezeichnet, die für einen Stromfluss von Drain nach Source sperrt. Rechts ist das typische Schaltsymbol eines solchen n-Kanal MOSFETs zu sehen. |

|

auch Luft sein) gewickelt, fällt das Magnetfeld lokal verändert aus und eine Spule entsteht. Elektrisch betrachtet widersetzen Spulen sich schnellen Stromänderungen und bauen bei einem Durchfluss durch Strom besagtes magnetisches Feld auf, man spricht von magnetischer Induktion. Spulen, die in VRMs auf Mainboards eingesetzt werden, sind in aller Regel Kupferdraht auf einem ferrimagnetischen Kern. Ferrimagnetika können die Induktivität der Spule durch ihre Magnetisierbarkeit ähnlich der von Ferromagneten stark erhöhen, jedoch sind Ferrimagnete Isolatoren, somit können keine Verluste durch das Induzieren von Wirbelströmen in den Kern auftreten. Weiter werden diese Spulen gern in starre Isolatoren eingegossen, damit mechanisches Schwingen der Spulen auf dem Kern bei hoher Frequenz unterbunden werden kann, was sonst zu akustischem Fiepen in dieser hohen Frequenz führt. Rechts sind die beiden Schaltsymbole zu sehen, welche Induktivitäten repräsentieren sollen. |

|

Grund dafür ist die gespeicherte Energie aus dem elektrischen Feld, das sich zwischen den beiden Elektroden des Kondensators aufbaut, wenn Spannung angelegt wird. Die Energie aus dem Feld kann die elektrische Spannung für den Moment weiter aufrecht erhalten, wenn diese z.B. abrupt abgeschaltet werden sollte. Genutzt werden so genannte Elektrolyt-Kondensatoren (kurz: Elko), da mit diesen sehr hohe elektrische Kapazitäten erreicht werden können. Dies liegt am geringen Abstand zwischen den Elektroden, welcher realisierbar ist, da eine Elektrode aus Aluminium besteht, während die andere eine schwache Säure ist. Das Dielektrikum ist nur eine dünne Oxydschicht auf der Anode aus Aluminium. Neu und vermehrt im Einsatz sind auch trockene Tantal Elkos. Das Tantal als Anode wird für eine größere Oberfläche gesintert und in Mangannitratlösung getaucht. Durch Erhitzen entsteht passgenau der Feststoff Mangandioxid als zweite Elektrode. Auch hier ist rechts das Schaltsymbol für elektrische Kapazitäten abgebildet. |

|

Dieser Begriff umfasst sämtliche Bauteile, die eine ganze Gruppe von Bauteilen in einem Gehäuse zusammenfassen. Dies geschieht heute, indem auf einer dünnen Halbleiterplatte mit komplexen Belichtungs- und/ oder Ätztechniken elektrisch leitende Strukturen geschaffen werden, die die Eigenschaften der Einzelbauteile besitzen. Die Ein- und Ausgangsleiterbahnen werden dann an die Pins des Gehäuses gelegt, damit der Schaltkreis mit Strukturbreiten teils unter dem µm Bereich in seine Applikation verbaut und dort genutzt werden kann. Solche Schaltkreise in VRMs sind der Mikrocontroller, der das gesamte VRM steuert und weitere Steuerelemente wie Treiber für Transistoren oder Doppler Schaltkreise. Eine übliche Darstellungsform eines ICs ist rechts zu sehen, man betrachtet diese quasi als Blackbox. Was im Inneren geschieht taucht im Schaltplan nicht weiter auf, nur die Ein- und Ausgänge sind angedeutet und beschriftet. |

|

- Puls-Weiten-Modulation

Die Kenngrößen eines solchen Signals sind die Frequenz, der Tastgrad und der Scheitelwert. Ein PWM Signal ist außerdem immer periodisch, also es wiederholt sich in der Zeit, die als eine Periode definiert wurde.

In dieser Periode kann das Signal nun zwei Zustände annehmen: HIGH oder LOW, bzw. 1 oder 0, etc...

Wie lange nun welcher der beiden Zustände zutrifft, bestimmt der Tastgrad (englisch: duty cycle). Er wird typisch in Prozent als Anteil der gesamten Periode angegeben.

Zum Beispiel ist unten in schwarz ein PWM Signal mit 10% Tastgrad über mehrere Perioden zu sehen.

Rot eingezeichnet ist der Gleichspannungsanteil, dieser ist wie folgt definiert: U[SUB]DC[/SUB] = Û * (t[SUB]e[/SUB]/T) = Û * Tastgrad

Daraus folgt für dieses PWM Signal: U[SUB]DC[/SUB] = 12V * 10% = 1,2V

Auf diese Weise lässt sich der Abwärtswandler einfach steuern bzw. seine Ausgangsspannung berechnen: Bei +12V Eingangsspannung stellt sich in der Theorie eine +1,2V Ausgangsspannung ein, wenn 10% Tastgrad für die Steuerung eingestellt wird.

Wie diese Steuerung vorgenommen wird, wird im folgenden erläutert.

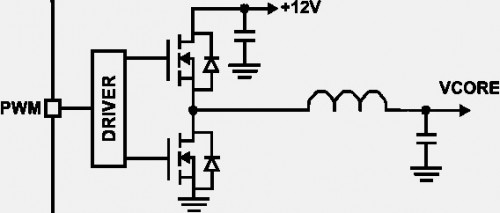

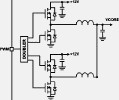

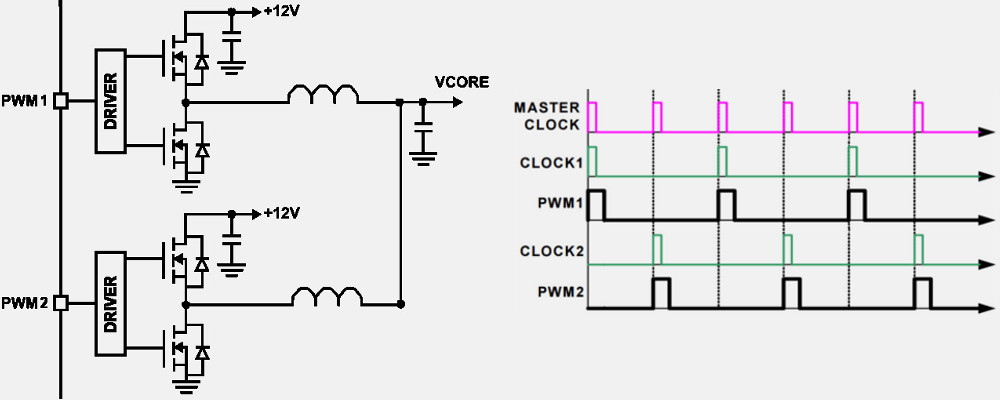

Das Schaltbild unten zeigt nun eine volle VRM Phase.

Von links nach rechts sind zuerst zwei ICs zu sehen, beginnend mit dem Controller. Von diesem ist nur ein Ausgang "PWM" abgebildet, angeschlossen daran ist ein dualer MOSFET Treiber, der zwei MOSFETs steuert: Am oberen Ausgang den so genannte highside FET und am unteren den lowside FET. Ersterer kann eine Verbindung von der +12V Eigangsspannung zur Spule ermöglichen, der lowside MOSFET schließt den Kreis für den Fall dass der highside MOSFET sperrt. Kondensatoren finden sich jeweils zwischen der Ein- und Ausgangsspannung in dem geteilten Nullpotential.

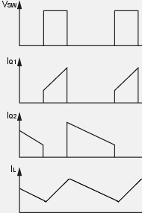

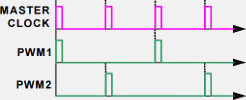

Rechts des Schaltplans ist ein Zeitdiagramm der Schaltung verschiedener Messpunkte über einige Perioden abgebildet.

Die Spannungswandlung läuft nun so ab:

Der Controller moduliert ein PWM Signal (wie oben beschrieben), an welches der Treiber angeschlossen ist. Das PWM Signal ist im Zeitdiagramm an der Achse V[SUB]SW[/SUB] aufgetragen.

Der Treiber steuert beide FETs folgendermaßen:

- Der highside FET wird mit dem positiven Puls vom Controller ein- und ausgeschaltet. Der Strom, der ihn durchfließt, ist mit I[SUB]Q1[/SUB] bezeichnet (siehe Zeitdiagramm).

- Der lowside FET wird immer dann eingeschaltet, wenn das PWM Signal auf LOW liegt. Also stets entgegengesetzt dem highside FET. Dieser Strom ist I[SUB]Q2[/SUB].

In diesem Aufbau spricht man auch vom synchronisierten Schaltwandler, da der Treiber die Ein- und Ausschaltzeiten der MOSFETs so synchronisiert, dass diese nie zusammen aktiv werden.

Über eine Periode betrachtet geschieht folgendes: Der highside FET wird eingeschaltet, Strom fließt durch die Spule und die Spannung am Ausgang des VRM steigt an, der Kondensator wird geladen. Wird nun der highside FET abgeschaltet, entlädt sich die Energie aus dem magnetischen Feld der Spule in Richtung des Kondensators bzw. dem VRM Ausgang.

Der nun eingeschaltete lowside MOSFET schließt den Stromkreis wieder. In der kurzen Zeit, in der der highside FET bereits abgeschaltet und auch der lowside FET inaktiv ist (so genannte Totzeit), kann der Stromfluss durch die Inversdiode des lowside FETs fließen.

Der Strom durch die Spule ist im Diagramm durch I[SUB]L[/SUB] beschrieben.

Dass am Ausgang des VRMs keine Ströme und Spannungen in Form von Rechteckimpulsen auftreten liegt daran, dass Spule und Kondensator einen Tiefpass bilden. Die hochfrequenten Amplituden werden durch diesen gedämpft und die pulsierende Wechselspannung damit ihrem Gleichspannungsanteil möglichst nahe gebracht - hier schleißt sich wieder der Kreis zum oben genannten Zusammenhang: Theoretisch entspricht der Gleichspannungsanteil des PWM Steuersignals der Ausgangsspannung des Wandlers.

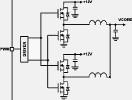

Wenn nun mehrere Phasen zum Einsatz kommen, ändert sich das Schaltbild wie zu erwarten:

Vom Controller kommt ein weiteres PWM Signal, mit dem die zweite Phase gesteuert wird. Die Komponenten der Phasen sind identisch, die Ausgänge der beiden Phasen werden elektrisch verbunden und die Kondensatoren am Ende werden zu einer additiven Gesamtkapazität zusammengefasst, indem sie parallel zueinander geschaltet werden.

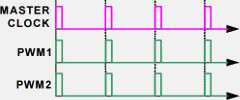

Diese beiden Phasen entlasten sich nun gegenseitig, indem vom Controller abwechselnd ein Puls auf beide PWM Ausgänge moduliert wird, wie im Zeitdiagramm rechts des Schaltbilds zu sehen ist. Jede Phase muss nur noch halb so oft Strom für den Verbraucher bereit stellen, was ihre Belastung halbiert.

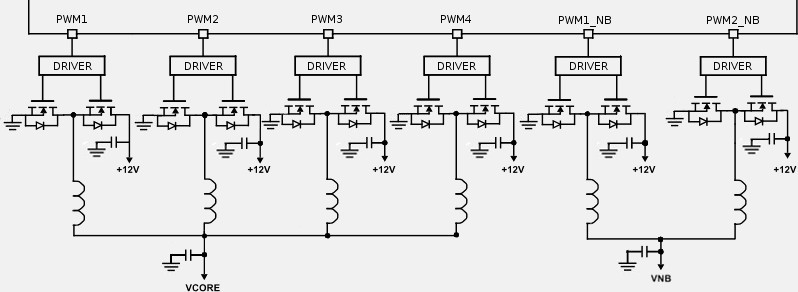

Gängige Controllermodelle können jedoch selten mehr als sechs Phasen für ein VRM steuern, oft gar nur vier. Dennoch sind häufig mehr Phasen angebracht, um die hohen Stromstärken liefern zu können, die für leistungsstarke x86 Prozessoren benötigt werden. Die Lösung dieses Problems ist das so genannte Doppeln.

Beim Doppeln werden mit dem PWM Signal einer Phase zwei Phasen gesteuert. Dies kann über zwei verschiedene Wege umgesetzt werden:

Im ersten Fall kommt kein neues Bauteil mit in den Schaltkreis, es wird stumpf völlig identisch in der zweiten, neuen Phase gesteuert. Das hat zur Folge, dass sich die ursprüngliche Charakteristik des VRM verändert, nun sind tatsächlich zwei Phasen genau gleichzeitig aktiv.

Im zweiten Fall bleibt diese Eigenschaft erhalten. Ein so genannter Doppler IC bekommt das PWM Signal des Controllers als Eingang und gibt zwei PWM Signale wieder aus. Diese haben die halbe Frequenz des Eingangssignals und sind um 180° phasenverschoben (360° ≙ 1 Periode), was das Abwechseln wiederherstellt.

Anmerkung der Vollständigkeit halber: Die Doppler im Schaltplan haben ganz offensichtlich auch integrierte Treiber.

Mikrocontroller, die typischer Weise auf aktuellen ATX Mainboards eingesetzt werden, um VRMs zu steuern, verfügen nicht nur über mehrere PWM Ausgänge, um mehrere Phasen zu steuern; sie besitzen zumeist auch mehrere Kanäle. Kanäle sind im Grunde die nächste Ebene über Phasen. So kann ein dual-channel Controller z.B. mit einem Kanal die Versorgungsspannung für Prozessorkerne und mit einem zweiten die Versorgungsspannung für die Northbridge Funktionen des Prozessors steuern. Jeder Kanal verfügt dann wieder über eigene Phasen.

Dieser Schaltplan zeigt ein 4+2 Layout für VCORE und VNB.

naVRMs in der Praxis

In der nachfolgenden Tabelle sind einige ausgewählte VRMs erläutert, um die praktische Umsetzung der oben beschriebenen VRM Komponenten zu sehen.

| Mainboard Modell | VRM Design | Bild |

|---|---|---|

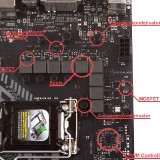

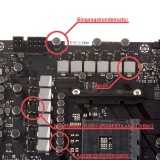

Gigabyte Z370 AORUS Ultra Gaming | 4+3 (VCC + VCCGT) Layout gesteuert vom ISL95866 Für VCC: - Pro Phase 2 highside MOSFETs vom Typ 4C10N - Pro Phase 2 lowside MOSFETs vom Typ 4C06N - Pro Phase 1 Spule Für VCCGT: - Pro Phase 1 highside MOSFET vom Typ 4C10N - Pro Phase 1 lowside MOSFET vom Typ 4C06N - Pro Phase 1 Spule Treiber sind zum Teil im Controller integriert, es sind nur insgesamt vier externe nötig (d.h. drei sind integriert). | |

ASUS ROG Strix H370/B360-F Gaming | (4x2)+1 (VCC + VCCGT) Layout gesteuert vom ASP1400CBT Für VCC: - Pro Phase 1 highside MOSFET vom Typ 4C10B - Pro Phase 1 lowside MOSFET vom Typ 4C06N - Pro Phase 1 Spule Für VCCGT: - Pro Phase 1 highside MOSFET vom Typ 4C10B - Pro Phase 2 lowside MOSFETs vom Typ 4C06N - Pro Phase 1 Spule Alle Treiber sind extern, in Summe sind 5 Treiber verbaut, an jedem der vier CPU VCC Treiber sind zwei Phasen angeschlossen, somit findet hier 'pseudo Doppeln' statt. | |

ASUS ROG Crosshair VII Hero | 10+2 (CPU + SoC) Layout gesteuert vom ASP1405I 5x IR3599 Doppler sorgt für 10+2 Phasen aus 5+2 PWM Ausgängen ('echtes Doppeln') Für CPU VCC und SoC VCC: - Pro Phase 1 powIRstage vom Typ IR3555 - Pro Phase 1 Spule -> powIRstages fassen highside FET, lowside FET und Treiber in ein IC zusammen | |

Gigabyte B450 Aorus Pro | 4+3 (CPU + SoC) Layout gesteuert vom ISL95712 Für CPU VCC: - Pro Phase 1 highside MOSFETs vom Typ 4C10N - Pro Phase 2 lowside MOSFETs vom Typ 4C06N - Pro Phase 1 Spule Für SoC VCC: - Pro Phase 1 highside MOSFET vom Typ 4C10N - Pro Phase 1 lowside MOSFET vom Typ 4C06N - Pro Phase 1 Spule Die zwei Spulen und lowside MOSFETs pro Phase werden parallel angesteuert. Diese Umsetzung entspricht weder einem strikten 4+3, noch einem (4x2)+3 Design. |

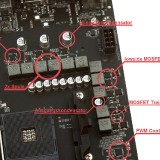

- Beispielbilder zum Identifizieren von Bauteilen

| Controller | ||||

|

|

|

| |

International Rectifier IR35201 | Intersil ISL95712 | Richtek RT8894A | ASUS ASP1400BT | |

| Treiber / Doppler | ||||

|

|

|

| |

International Rectifier IR3598 | International Rectifier IR3535 | Intersil ISL6625A | Richtek RT9624F | |

| MOSFETs | ||||

|

|

|

|

|

einzelner MOSFET SO-8 Package Vishay SiRA18DP | einzelner MOSFET PDFN-8 Package NIKO PK616BA | einzelner MOSFET TO-252 Package A&O AOD452A | PowIRstage International Rectifier IR3553M | NexFET Texas Instruments CSD87350D |

| Spulen | ||||

|

|

|

| |

Spule mit Kunstsstoff-Mantel | Spule mit halb offenem Kunststoff-Mantel | Luftspule ohne Mantellung | SMD-Spule mit Kunststoff-Mantel | |

| Kondensatoren | ||||

|

|

| ||

Kondensator mit flüssigem Elektrolyt | Polymer- (/ Feststoff-) Kondensator | SMD- Kondensator |

- Verluste

Folgende Verluste treten in den Komponenten eines VRMs auf:

- highside MOSFET

Ohmsche Verluste treten für die Zeit auf, in der der Kanal niederohmsch leitend wird. Für die Verluste kann hier vereinfachend der Zusammenhang P=I[SUP]2[/SUP]⋅R aus der Gleichstromlehre genutzt werden, hinzu kommt natürlich besagter Zeitfaktor in Form des Tastgrads.

P[SUB]on[/SUB] = I[SUB]out[/SUB][SUP]2[/SUP] ⋅ R[SUB]DS(on)[/SUB] ⋅ [ V[SUB]out[/SUB] / V[SUB]in[/SUB] ]

Für den Fall von zwei FETs parallel zueinander ist mit 1/2 R[SUB]DS(on)[/SUB] zu rechnen.

Schaltverluste entstehen, da Schaltvorgänge in der Praxis nie durch eine Flanke mit unendlicher Steigung geschehen, sondern in Rampenform. Dies sorgt für einen Vorfaktor 1/2 für die Verluste, da die Leistung bekanntlich unter einer U-I-Rampe entsteht und dieses Integral ein einfaches Dreieck ist. Neben Spannung und Strom gehen dann auch Schaltfrequenz und die Zeit des Schaltvorgangs ein.

P[SUB]sw[/SUB] = 1/2 ⋅ V[SUB]in[/SUB] ⋅ I[SUB]out[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ ( t[SUB]r[/SUB] + t[SUB]f[/SUB] )

Gate-Ladungs-Verluste entstehen durch das Laden der Kapazität am Gate, die für das elektrische Feld sorgt, das den leitenden Kanal ermöglicht. Neben der benötgiten Ladung gehen auch Frequenz und Gate-Spannung ein.

P[SUB]GC[/SUB] = Q[SUB]G[/SUB] ⋅ V[SUB]sw[/SUB] ⋅ f[SUB]sw[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Gate-Ladung auszugehen.

Ausgangskapazitätsverluste entstehen in jeder Periode durch das Aufladen der Kapazitäten zwischen Gate-Drain und Drain-Source. Zusammengefasst ist dies die C[SUB]OSS[/SUB] Kapazität.

P[SUB]COSS[/SUB] = 1/2 ⋅ V[SUB]in[/SUB][SUP]2[/SUP] ⋅ f[SUB]sw[/SUB] ⋅ C[SUB]OSS[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Ausgangskapazität auszugehen.

- lowside MOSFET

Für die ohmschen Verluste gilt gleicher Zusammenhang wie beim highside FET.

P[SUB]on[/SUB] = I[SUB]out[/SUB][SUP]2[/SUP] ⋅ R[SUB]DS(on)[/SUB] ⋅ [ 1 - V[SUB]out[/SUB] / V[SUB]in[/SUB] ]

Für den Fall von zwei FETs parallel zueinander ist mit 1/2 R[SUB]DS(on)[/SUB] zu rechnen.

Schaltverluste fallen durch die Inversdiode des lowside FETs geringer aus.

P[SUB]sw[/SUB] = 1/2 ⋅ V[SUB]D[/SUB] ⋅ I[SUB]out[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ ( t[SUB]r[/SUB] + t[SUB]f[/SUB] )

Gate-Ladungs-Verluste treten in gleicher Form wie im highside FET auf.

P[SUB]GC[/SUB] = Q[SUB]G[/SUB] ⋅ V[SUB]sw[/SUB] ⋅ f[SUB]sw[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Gate-Ladung auszugehen.

Ausgangskapazitätsverluste verhalten sich identisch zur highside.

P[SUB]COSS[/SUB] = 1/2 ⋅ V[SUB]in[/SUB][SUP]2[/SUP] ⋅ f[SUB]sw[/SUB] ⋅ C[SUB]OSS[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Ausgangskapazität auszugehen.

Totzeit Verluste entstehen, wenn beide FETs abgeschaltet sind und der Strom durch die Inversdiode fließen muss. Über eine solche fällt bekanntlich die Diffusionsspannung V[SUB]D[/SUB] ab, um das Feld der Sperrschicht des p-n-Übergangs zu überwinden. Neben der Stromstärke gehen ebenfalls die Schaltfrequenz, und natürlich die Zeiten ein, die hier großzügig ausschließlich durch die Verzögerungszeiten des Transistors repräsentiert werden. Weiter aufsummieren könnte man Verzögerungszeiten durch den Treiber.

P[SUB]D[/SUB] = V[SUB]D[/SUB] ⋅ I[SUB]out[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ (t[SUB]d,r[/SUB] + t[SUB]d,f[/SUB])

Für den Fall von zwei FETs parallel zueinander ist von halber Stromstärke auszugehen.

Sperrverzögerungs-Verluste entstehen durch den Wiederaufbau der Sperrschicht der Inversdiode des lowside FETs, wenn der highside FET wieder eingeschaltet wird.

P[SUB]RR[/SUB] = V[SUB]in[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ I[SUB]out[/SUB] ⋅ t[SUB]RR[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von halber Stromstärke auszugehen.

- Spule

Kupferverluste treten auf, da die Spule beim Durchfließen durch den Strom wie ein ohmscher Widerstand wirkt.

P[SUB]L,Cu[/SUB] = I[SUB]out[/SUB][SUP]2[/SUP] ⋅ R[SUB]DCR[/SUB]

Als Hystereseverluste bezeichnet man die zur Ummagnetisierung benötigte Energie, die innerhalb des Materials des Kerns in Wärme umgewandelt wird.

Weiter werden mit steigender Frequenz Nachwirkungsverluste größer, diese resultieren daraus, dass die Magnetisierung bei hoher Frequenz nicht mehr dem erregenden Feld folgen kann.

Diese beiden Verlusttypen sind jedoch ohne genau Kenntnis der Geometrie, geschweige denn umfangreiches Datenblatt im Grunde nicht zu berechnen.

Wirbelstromverluste treten bemerkbar nur in metallisch leitenden Werkstoffen auf, Ferritkerne fallen nicht in diese Gruppe.

- Kondensatoren

Ohmsche Verluste dominieren alle weiteren Verluste im Elektrolytkondensator, beschrieben wird der verursachende Widerstand durch den ESR (equivalent series resistor).

P[SUB]C,ESR[/SUB] = I[SUP]2[/SUP] ⋅ R[SUB]ESR[/SUB]

Da in den ESR bereits die Frequenz eingeht, kann ein präziserer ESR für die spezifische Anwendung über den Verlustfaktor tan(δ) und die Reaktanz (Blindwiderstand) über folgenden Zusammenhang errechnet werden:

R[SUB]ESR[/SUB] = tan(δ) ⋅ 1/(ωC) = tan(δ) ⋅ 1/(2π ⋅ f ⋅ C)

Verluste in Controllern, Treibern und Dopplern können über den Zusammenhang P=U⋅I bestimmt werden, in Datenblättern sind meist typische Werte für Eingangsspannung und -strom festgehalten.

Die Summe über sämtliche Teilverluste ergibt dann einen annehmbar exakten zu erwartenden Gesamtverlust pro Phase für ein VRM: P[SUB]tot[/SUB] = ΣP

Mit gewissem Aufwand lässt sich aus den Zusammenhängen oben mit einer Tabellenkalkulationssoftware ein rudimentärer Simulator für VRMs bauen, mit dem sich dann nach belieben verschiedene Konstellationen, Szenarien und Daten auswerten und vergleichen lassen.

Fertige Dokumente für diesen Zweck bieten aber auch bereits Halbleiterhersteller selbst an, z.B. ON Semi. oder Texas Instruments. Nachteil sind hier aber i.d.R. nicht bzw. nur schwer einsehbare Berechnungen, die diese Dokumente unflexibel und eher schlecht nachvollziehbar machen.

- highside MOSFET

Ohmsche Verluste treten für die Zeit auf, in der der Kanal niederohmsch leitend wird. Für die Verluste kann hier vereinfachend der Zusammenhang P=I[SUP]2[/SUP]⋅R aus der Gleichstromlehre genutzt werden, hinzu kommt natürlich besagter Zeitfaktor in Form des Tastgrads.

P[SUB]on[/SUB] = I[SUB]out[/SUB][SUP]2[/SUP] ⋅ R[SUB]DS(on)[/SUB] ⋅ [ V[SUB]out[/SUB] / V[SUB]in[/SUB] ]

Für den Fall von zwei FETs parallel zueinander ist mit 1/2 R[SUB]DS(on)[/SUB] zu rechnen.

Schaltverluste entstehen, da Schaltvorgänge in der Praxis nie durch eine Flanke mit unendlicher Steigung geschehen, sondern in Rampenform. Dies sorgt für einen Vorfaktor 1/2 für die Verluste, da die Leistung bekanntlich unter einer U-I-Rampe entsteht und dieses Integral ein einfaches Dreieck ist. Neben Spannung und Strom gehen dann auch Schaltfrequenz und die Zeit des Schaltvorgangs ein.

P[SUB]sw[/SUB] = 1/2 ⋅ V[SUB]in[/SUB] ⋅ I[SUB]out[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ ( t[SUB]r[/SUB] + t[SUB]f[/SUB] )

Gate-Ladungs-Verluste entstehen durch das Laden der Kapazität am Gate, die für das elektrische Feld sorgt, das den leitenden Kanal ermöglicht. Neben der benötgiten Ladung gehen auch Frequenz und Gate-Spannung ein.

P[SUB]GC[/SUB] = Q[SUB]G[/SUB] ⋅ V[SUB]sw[/SUB] ⋅ f[SUB]sw[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Gate-Ladung auszugehen.

Ausgangskapazitätsverluste entstehen in jeder Periode durch das Aufladen der Kapazitäten zwischen Gate-Drain und Drain-Source. Zusammengefasst ist dies die C[SUB]OSS[/SUB] Kapazität.

P[SUB]COSS[/SUB] = 1/2 ⋅ V[SUB]in[/SUB][SUP]2[/SUP] ⋅ f[SUB]sw[/SUB] ⋅ C[SUB]OSS[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Ausgangskapazität auszugehen.

- lowside MOSFET

Für die ohmschen Verluste gilt gleicher Zusammenhang wie beim highside FET.

P[SUB]on[/SUB] = I[SUB]out[/SUB][SUP]2[/SUP] ⋅ R[SUB]DS(on)[/SUB] ⋅ [ 1 - V[SUB]out[/SUB] / V[SUB]in[/SUB] ]

Für den Fall von zwei FETs parallel zueinander ist mit 1/2 R[SUB]DS(on)[/SUB] zu rechnen.

Schaltverluste fallen durch die Inversdiode des lowside FETs geringer aus.

P[SUB]sw[/SUB] = 1/2 ⋅ V[SUB]D[/SUB] ⋅ I[SUB]out[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ ( t[SUB]r[/SUB] + t[SUB]f[/SUB] )

Gate-Ladungs-Verluste treten in gleicher Form wie im highside FET auf.

P[SUB]GC[/SUB] = Q[SUB]G[/SUB] ⋅ V[SUB]sw[/SUB] ⋅ f[SUB]sw[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Gate-Ladung auszugehen.

Ausgangskapazitätsverluste verhalten sich identisch zur highside.

P[SUB]COSS[/SUB] = 1/2 ⋅ V[SUB]in[/SUB][SUP]2[/SUP] ⋅ f[SUB]sw[/SUB] ⋅ C[SUB]OSS[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von einer doppelten Ausgangskapazität auszugehen.

Totzeit Verluste entstehen, wenn beide FETs abgeschaltet sind und der Strom durch die Inversdiode fließen muss. Über eine solche fällt bekanntlich die Diffusionsspannung V[SUB]D[/SUB] ab, um das Feld der Sperrschicht des p-n-Übergangs zu überwinden. Neben der Stromstärke gehen ebenfalls die Schaltfrequenz, und natürlich die Zeiten ein, die hier großzügig ausschließlich durch die Verzögerungszeiten des Transistors repräsentiert werden. Weiter aufsummieren könnte man Verzögerungszeiten durch den Treiber.

P[SUB]D[/SUB] = V[SUB]D[/SUB] ⋅ I[SUB]out[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ (t[SUB]d,r[/SUB] + t[SUB]d,f[/SUB])

Für den Fall von zwei FETs parallel zueinander ist von halber Stromstärke auszugehen.

Sperrverzögerungs-Verluste entstehen durch den Wiederaufbau der Sperrschicht der Inversdiode des lowside FETs, wenn der highside FET wieder eingeschaltet wird.

P[SUB]RR[/SUB] = V[SUB]in[/SUB] ⋅ f[SUB]sw[/SUB] ⋅ I[SUB]out[/SUB] ⋅ t[SUB]RR[/SUB]

Für den Fall von zwei FETs parallel zueinander ist von halber Stromstärke auszugehen.

- Spule

Kupferverluste treten auf, da die Spule beim Durchfließen durch den Strom wie ein ohmscher Widerstand wirkt.

P[SUB]L,Cu[/SUB] = I[SUB]out[/SUB][SUP]2[/SUP] ⋅ R[SUB]DCR[/SUB]

Als Hystereseverluste bezeichnet man die zur Ummagnetisierung benötigte Energie, die innerhalb des Materials des Kerns in Wärme umgewandelt wird.

Weiter werden mit steigender Frequenz Nachwirkungsverluste größer, diese resultieren daraus, dass die Magnetisierung bei hoher Frequenz nicht mehr dem erregenden Feld folgen kann.

Diese beiden Verlusttypen sind jedoch ohne genau Kenntnis der Geometrie, geschweige denn umfangreiches Datenblatt im Grunde nicht zu berechnen.

Wirbelstromverluste treten bemerkbar nur in metallisch leitenden Werkstoffen auf, Ferritkerne fallen nicht in diese Gruppe.

- Kondensatoren

Ohmsche Verluste dominieren alle weiteren Verluste im Elektrolytkondensator, beschrieben wird der verursachende Widerstand durch den ESR (equivalent series resistor).

P[SUB]C,ESR[/SUB] = I[SUP]2[/SUP] ⋅ R[SUB]ESR[/SUB]

Da in den ESR bereits die Frequenz eingeht, kann ein präziserer ESR für die spezifische Anwendung über den Verlustfaktor tan(δ) und die Reaktanz (Blindwiderstand) über folgenden Zusammenhang errechnet werden:

R[SUB]ESR[/SUB] = tan(δ) ⋅ 1/(ωC) = tan(δ) ⋅ 1/(2π ⋅ f ⋅ C)

Verluste in Controllern, Treibern und Dopplern können über den Zusammenhang P=U⋅I bestimmt werden, in Datenblättern sind meist typische Werte für Eingangsspannung und -strom festgehalten.

Die Summe über sämtliche Teilverluste ergibt dann einen annehmbar exakten zu erwartenden Gesamtverlust pro Phase für ein VRM: P[SUB]tot[/SUB] = ΣP

Mit gewissem Aufwand lässt sich aus den Zusammenhängen oben mit einer Tabellenkalkulationssoftware ein rudimentärer Simulator für VRMs bauen, mit dem sich dann nach belieben verschiedene Konstellationen, Szenarien und Daten auswerten und vergleichen lassen.

Fertige Dokumente für diesen Zweck bieten aber auch bereits Halbleiterhersteller selbst an, z.B. ON Semi. oder Texas Instruments. Nachteil sind hier aber i.d.R. nicht bzw. nur schwer einsehbare Berechnungen, die diese Dokumente unflexibel und eher schlecht nachvollziehbar machen.

- Belastbarkeit

- MOSFETs

Der wichtigste Beiwert für die Belastbarkeit von MOSFETs ist ihre Temperatur. Eingesetzt werden Leistungshalbleiter auf Siliziumbasis in einem Temperaturbereich, in dem die so genannte Störstellenerschöpfung stattfindet (circa 25°C bis 150°C), in welcher die mit der Temperatur abnehmende Beweglichkeit der Ladungsträger im Material den elektrischen Widerstand erhöht.

Durch steigende Verluste bei steigender Belastung, die eine steigende Temperatur bedingen, ist also wiederum mit noch größeren Verlusten zu rechnen.

Einfach zusammengefasst bedeutet dieser Kreis: Der Silizium FET kann am besten bei niedriger Raumtemperatur belastet werden und sollte während seiner Belastung optimaler Weise auch auf dieser Temperatur gehalten werden.

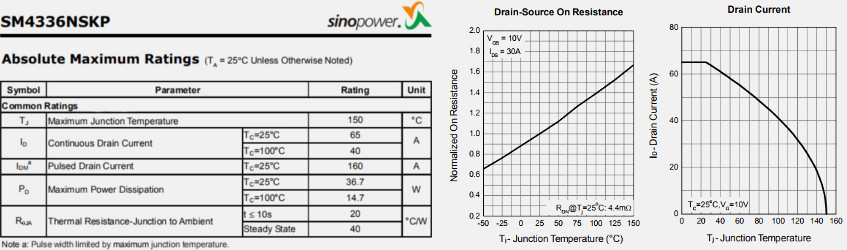

Mit welcher Belastbarkeit eines MOSFETs nun in der Praxis gerechnet werden darf, soll am Beispiel des sinopower SM4336NSKP gezeigt werden.

Der Auszug des Datenblatts oben zeigt einige der absoluten Maximalspezifikationen und die Abhängigkeiten des R[SUB]DS(on)[/SUB] und des I[SUB]D[/SUB] zur Halbleitertemperatur.

Auf den ersten Blick erscheinen maximaler permanenter Strom I[SUB]D[/SUB] und maximale Verlustleistung P[SUB]D[/SUB] selbst bei hoher Gehäusetemperatur des FETs relativ hoch, in der Praxis werden diese Werte aber nur bei sehr guter Kühlung relevant, wie sich schnell zeigen lässt:

R[SUB]θJA[/SUB] steht für den thermischen Widerstand zwischen Halbleitermaterial und Umgebung, die Einheit ist °C/W.

Demnach erwärmt sich ein sinopower SM4336NSKP MOSFET um 40°C mit jedem Watt Verlustleistung ohne Kühlkörper bei 25°C Umgebungstemperatur bei permanentem Stromfluss zwischen Source und Drain.

Dieser FET wird i.d.R. als lowside MOSFET eingesetzt, dessen Belastung kommt einem 'steady state' oder 'continuous rating' also schon recht nahe.

Wäre also aufgrund von Berechnungen eine Verlustleistung von 1,5W zu erwarten, müsste bei 30°C Umgebungstemperatur von einer Erwärmung auf knapp 90°C ausgegangen werden. Die maximal spezifizierte Stromstärke I[SUB]D[/SUB] würde um über 30% auf etwa 45A sinken.

Somit zahlt sich auch die Spezifiaktion für bis zu 14,7W Verlustleistung bei 100°C Gehäusetemperatur erst mit sehr effektiver Kühlung aus bzw. erhält überhaupt erst gewisse Relevanz.

Im Diagramm zum R[SUB]DS(on)[/SUB] ist ein Multiplikator für diesen in Abhängigkeit der Temperatur aufgetragen, dies stellt die oben beschriebene Problematik gut dar, mit steigender Temperatur steigt Widerstand des Halbleiters in einem Bereich von -50°C bis +150°C näherungsweise linear an.

Der konstante maximal spezifizierte Strom verhält sich bis 20°C nur auf Grund der maximalen Spezifikation der Bauform konstant.

Zusammenfassend werden die maximalen Spezifikationen für I[SUB]D[/SUB] und P[SUB]D[/SUB] von typischen MOSFETs in VRMs also erst mit sehr guter Kühlung in der Praxis relevant.

Umso weniger für eine niedrige Betriebstemperatur unter erhöhter Last getan wird, desto irrelevanter werden sie und es gilt viel mehr Verluste und damit einhergehende Erwärmung zu betrachten.

- Spulen

Während eine Spule relativ resistent gegen hohe Temperatur ist, gilt es den Zustand der Sättigung tunlichst zu vermeiden.

Wenn die Sättigungsstromstärke erreicht ist, kann keine weitere Energie mehr im Magnetfeld gespeichert werden und die Spule beginnt rein niederohmsch zu wirken.

Der Strom, der maximal durch eine Phase fließen darf, ist also von Seiten der Spule dadurch limitiert, dass die Sättigungsstromstärke nie erreicht werden darf.

Die Verluste der Spule sind natürlich dennoch (nicht nur wegen einer potentiell höheren Stromrechnung) nicht zu verachten, die abgegebene Wärme kann das Abführen der Wärme von MOSFETs oder Kondensatoren negativ beeinflussen bzw. diese direkt zusätzlich erwärmen.

Der wichtigste Beiwert für die Belastbarkeit von MOSFETs ist ihre Temperatur. Eingesetzt werden Leistungshalbleiter auf Siliziumbasis in einem Temperaturbereich, in dem die so genannte Störstellenerschöpfung stattfindet (circa 25°C bis 150°C), in welcher die mit der Temperatur abnehmende Beweglichkeit der Ladungsträger im Material den elektrischen Widerstand erhöht.

Durch steigende Verluste bei steigender Belastung, die eine steigende Temperatur bedingen, ist also wiederum mit noch größeren Verlusten zu rechnen.

Einfach zusammengefasst bedeutet dieser Kreis: Der Silizium FET kann am besten bei niedriger Raumtemperatur belastet werden und sollte während seiner Belastung optimaler Weise auch auf dieser Temperatur gehalten werden.

Mit welcher Belastbarkeit eines MOSFETs nun in der Praxis gerechnet werden darf, soll am Beispiel des sinopower SM4336NSKP gezeigt werden.

Der Auszug des Datenblatts oben zeigt einige der absoluten Maximalspezifikationen und die Abhängigkeiten des R[SUB]DS(on)[/SUB] und des I[SUB]D[/SUB] zur Halbleitertemperatur.

Auf den ersten Blick erscheinen maximaler permanenter Strom I[SUB]D[/SUB] und maximale Verlustleistung P[SUB]D[/SUB] selbst bei hoher Gehäusetemperatur des FETs relativ hoch, in der Praxis werden diese Werte aber nur bei sehr guter Kühlung relevant, wie sich schnell zeigen lässt:

R[SUB]θJA[/SUB] steht für den thermischen Widerstand zwischen Halbleitermaterial und Umgebung, die Einheit ist °C/W.

Demnach erwärmt sich ein sinopower SM4336NSKP MOSFET um 40°C mit jedem Watt Verlustleistung ohne Kühlkörper bei 25°C Umgebungstemperatur bei permanentem Stromfluss zwischen Source und Drain.

Dieser FET wird i.d.R. als lowside MOSFET eingesetzt, dessen Belastung kommt einem 'steady state' oder 'continuous rating' also schon recht nahe.

Wäre also aufgrund von Berechnungen eine Verlustleistung von 1,5W zu erwarten, müsste bei 30°C Umgebungstemperatur von einer Erwärmung auf knapp 90°C ausgegangen werden. Die maximal spezifizierte Stromstärke I[SUB]D[/SUB] würde um über 30% auf etwa 45A sinken.

Somit zahlt sich auch die Spezifiaktion für bis zu 14,7W Verlustleistung bei 100°C Gehäusetemperatur erst mit sehr effektiver Kühlung aus bzw. erhält überhaupt erst gewisse Relevanz.

Im Diagramm zum R[SUB]DS(on)[/SUB] ist ein Multiplikator für diesen in Abhängigkeit der Temperatur aufgetragen, dies stellt die oben beschriebene Problematik gut dar, mit steigender Temperatur steigt Widerstand des Halbleiters in einem Bereich von -50°C bis +150°C näherungsweise linear an.

Der konstante maximal spezifizierte Strom verhält sich bis 20°C nur auf Grund der maximalen Spezifikation der Bauform konstant.

Zusammenfassend werden die maximalen Spezifikationen für I[SUB]D[/SUB] und P[SUB]D[/SUB] von typischen MOSFETs in VRMs also erst mit sehr guter Kühlung in der Praxis relevant.

Umso weniger für eine niedrige Betriebstemperatur unter erhöhter Last getan wird, desto irrelevanter werden sie und es gilt viel mehr Verluste und damit einhergehende Erwärmung zu betrachten.

- Spulen

Während eine Spule relativ resistent gegen hohe Temperatur ist, gilt es den Zustand der Sättigung tunlichst zu vermeiden.

Wenn die Sättigungsstromstärke erreicht ist, kann keine weitere Energie mehr im Magnetfeld gespeichert werden und die Spule beginnt rein niederohmsch zu wirken.

Der Strom, der maximal durch eine Phase fließen darf, ist also von Seiten der Spule dadurch limitiert, dass die Sättigungsstromstärke nie erreicht werden darf.

Die Verluste der Spule sind natürlich dennoch (nicht nur wegen einer potentiell höheren Stromrechnung) nicht zu verachten, die abgegebene Wärme kann das Abführen der Wärme von MOSFETs oder Kondensatoren negativ beeinflussen bzw. diese direkt zusätzlich erwärmen.

- Welche Vorteile haben mehr Phasen?

Für alle zusätzlichen Phasen mit angepasster Phasenverschiebung zueinander (sprich echten Phasen und echt gedoppelte Phasen) gelten folgende Vorteile:

- Geringere Stromstärke an den MOSFETs und der Spule

Mit n Phasen anstelle von einer entspricht die Stromstärke pro Phase I[SUB]pp[/SUB] = I[SUB]tot[/SUB] / n.

Dies führt zu geringerer Belastung der stromführenden Komponenten und damit zu geringeren ohmschen Verlusten, für die bekanntlich gilt:

P = I[SUP]2[/SUP] ⋅ R

Für zwei Phasen bedeutet dies:

2 ⋅ ( ( 1/2 I)[SUP]2[/SUP] ⋅ R ) = P/2

Somit können mit mehr Phasen also entweder größere Ströme ohne Wechsel der Bauteile realisiert werden oder aber weniger belastbare Bauteile eingesetzt werden, um die gleichen Ströme durch den Wandler zu leiten.

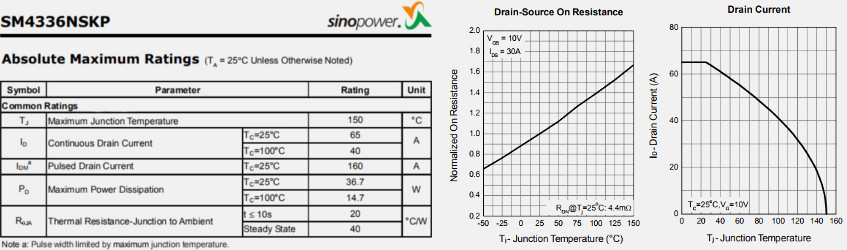

- Geringere Stromspitzen bzw. Restwelligkeit an den Eingangs- und Ausgangskondensatoren

Die Entlastung der Eingangskondensatoren geht einher mit oben genanntem ersten Vorteil. Die Höhe der Spitzen des Eingangsstroms wird halbiert, wenn statt einer zwei Phasen verschoben zueinander für eine Spitze sorgen. So kann mit zwei Phasen entweder mit gleicher Eingangskapazität höhere Stromstärke unter Einhaltung der Vorschriften für Restwelligkeit durch den Wandler fließen, als mit einer Phase. Oder aber es kann mit geringerer Kapazität der gleiche Strom innerhalb der Vorschriften den Wandler passieren.

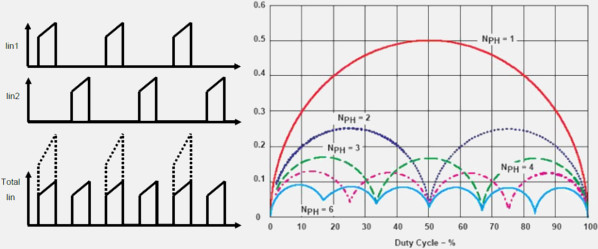

Im Diagramm unten links sind die Eingangsströme zweier Phasen zu sehen, darunter ihre Addition und nur gestrichelt die Erweiterung der Spitzen im Falle von nur einer Phase.

Das rechte Diagramm stellt den Zusammenhang zwischen dem Multiplikator für Restwelligkeit und dem Tastgrad bei unterschiedlicher Phasenanzahl dar.

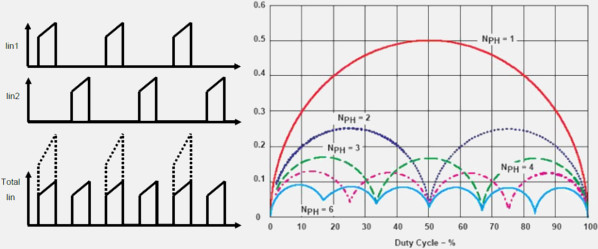

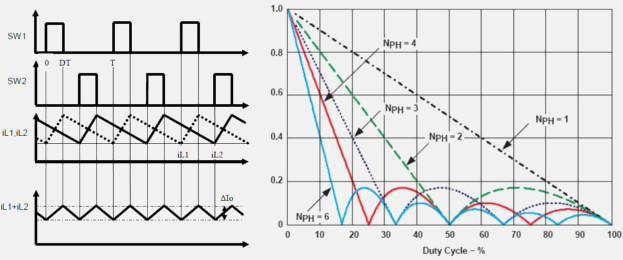

Die Ausgangskondensatoren haben weniger Restwelligkeit aus zwei Phasen als aus einer zu glätten, da zwei phasenverschobene Induktionen das ΔI[SUB]o[/SUB] (also die Restwelligkeit hinter der Spule) verringern. Das Diagramm unten links stellt dies dar, oben sind die beiden PWM Signale der Phasen abgebildet, darunter die Ströme durch die beiden Spulen. Diese beiden Stromverläufe addiert resultieren im neuen induktiven Ausgangsstrom ganz unten mit geringerer Differenz zwischen Scheitel und Tal.

Im rechten Diagramm ist wieder der Tastgrad gegen den Multiplikator für Restwelligkeit bei verschiedenen Anzahlen an Phasen aufgetragen.

- Verbessertes Verhalten bei Last Transienten

Ein besseres Vermeiden von größeren Unter- oder Überschwingern der Ausgangsspannung kann dann erreicht werden, wenn Änderungen an der Ansteuerung (der Modulation der V[SUB]SW[/SUB]) schneller in einer veränderten Ausgangsspannung resultieren. Um diesen Effekt zu erreichen, wird hohe Schaltfrequenz in Verbindung mit kleiner Induktivität der Spule eingesetzt, da der Strom bei geringerer Induktivität schneller durch diese fließt.

Anders als Kondensatoren verhalten sich parallele Induktivitäten wie parallele ohmsche Widerstände: Sie addieren sich nicht, sondern ergeben eine neue Gesamtinduktivität, die stets kleiner als die größte Einzelinduktivität ist. Genutzt wird diese Eigenschaft, indem der Controller bei einem detektierten transienten Szenario sämtliche Phasen zur gleichen Zeit pulst, was alle Spulen in eine Parallelschaltung versetzt und damit die effektive Induktivität (je nach Anzahl der Phasen) deutlichst verringert.

Da nun die Ausgangskondensatoren schneller geladen werden können, wird ein starker Unterschwinger verhindert, zu einem Überschwingen kann es nicht kommen, da weniger Energie im Feld der Spulen gespeichert ist.

- Geringere Stromstärke an den MOSFETs und der Spule

Mit n Phasen anstelle von einer entspricht die Stromstärke pro Phase I[SUB]pp[/SUB] = I[SUB]tot[/SUB] / n.

Dies führt zu geringerer Belastung der stromführenden Komponenten und damit zu geringeren ohmschen Verlusten, für die bekanntlich gilt:

P = I[SUP]2[/SUP] ⋅ R

Für zwei Phasen bedeutet dies:

2 ⋅ ( ( 1/2 I)[SUP]2[/SUP] ⋅ R ) = P/2

Somit können mit mehr Phasen also entweder größere Ströme ohne Wechsel der Bauteile realisiert werden oder aber weniger belastbare Bauteile eingesetzt werden, um die gleichen Ströme durch den Wandler zu leiten.

- Geringere Stromspitzen bzw. Restwelligkeit an den Eingangs- und Ausgangskondensatoren

Die Entlastung der Eingangskondensatoren geht einher mit oben genanntem ersten Vorteil. Die Höhe der Spitzen des Eingangsstroms wird halbiert, wenn statt einer zwei Phasen verschoben zueinander für eine Spitze sorgen. So kann mit zwei Phasen entweder mit gleicher Eingangskapazität höhere Stromstärke unter Einhaltung der Vorschriften für Restwelligkeit durch den Wandler fließen, als mit einer Phase. Oder aber es kann mit geringerer Kapazität der gleiche Strom innerhalb der Vorschriften den Wandler passieren.

Im Diagramm unten links sind die Eingangsströme zweier Phasen zu sehen, darunter ihre Addition und nur gestrichelt die Erweiterung der Spitzen im Falle von nur einer Phase.

Das rechte Diagramm stellt den Zusammenhang zwischen dem Multiplikator für Restwelligkeit und dem Tastgrad bei unterschiedlicher Phasenanzahl dar.

Die Ausgangskondensatoren haben weniger Restwelligkeit aus zwei Phasen als aus einer zu glätten, da zwei phasenverschobene Induktionen das ΔI[SUB]o[/SUB] (also die Restwelligkeit hinter der Spule) verringern. Das Diagramm unten links stellt dies dar, oben sind die beiden PWM Signale der Phasen abgebildet, darunter die Ströme durch die beiden Spulen. Diese beiden Stromverläufe addiert resultieren im neuen induktiven Ausgangsstrom ganz unten mit geringerer Differenz zwischen Scheitel und Tal.

Im rechten Diagramm ist wieder der Tastgrad gegen den Multiplikator für Restwelligkeit bei verschiedenen Anzahlen an Phasen aufgetragen.

- Verbessertes Verhalten bei Last Transienten

Ein besseres Vermeiden von größeren Unter- oder Überschwingern der Ausgangsspannung kann dann erreicht werden, wenn Änderungen an der Ansteuerung (der Modulation der V[SUB]SW[/SUB]) schneller in einer veränderten Ausgangsspannung resultieren. Um diesen Effekt zu erreichen, wird hohe Schaltfrequenz in Verbindung mit kleiner Induktivität der Spule eingesetzt, da der Strom bei geringerer Induktivität schneller durch diese fließt.

Anders als Kondensatoren verhalten sich parallele Induktivitäten wie parallele ohmsche Widerstände: Sie addieren sich nicht, sondern ergeben eine neue Gesamtinduktivität, die stets kleiner als die größte Einzelinduktivität ist. Genutzt wird diese Eigenschaft, indem der Controller bei einem detektierten transienten Szenario sämtliche Phasen zur gleichen Zeit pulst, was alle Spulen in eine Parallelschaltung versetzt und damit die effektive Induktivität (je nach Anzahl der Phasen) deutlichst verringert.

Da nun die Ausgangskondensatoren schneller geladen werden können, wird ein starker Unterschwinger verhindert, zu einem Überschwingen kann es nicht kommen, da weniger Energie im Feld der Spulen gespeichert ist.

- Sind mehr Phasen dann immer besser?

Mehrere Phasen bringen durchaus auch Nachteile mit sich.

Während die ohmschen Verluste der ursprünglichen Komponenten geringer werden, kommen nun neue Komponenten mit derartigen Verlusten hinzu, weiter müssen nun die Kapazitäten mehrerer MOSFETs tausendfach die Sekunde umgeladen werden, etc..

Simulatoren zeigen, dass Designs aus vielen Phasen besonders bei geringer Last durchaus ineffizienter werden können, als solche mit moderater Phasenanzahl.

Das Nutzen der oben genannte Vorteile ist auch eine Frage der tatsächlichen Implementierung des VRMs, es liegt in der Hand der Ingenieure, inwiefern diese genutzt werden.

Besonders dann, wenn mehrere Phasen völlig parallel zueinander fungieren (Pseudo-Doppeln), fallen alle Vorteile abgesehen von ersterem und letzterem grundsätzlich weg.

Somit muss die unbefriedigende Antwort auf diese Frage lauten: Nein.

Diese Thematik ist leider zu fallspezifisch, um eine gute, allgemeine Antwort zu finden. Das ist auch der Grund des Umfang dieses Guides: Er soll das Wissen vermitteln, um sich selbst ein Bild von seinem Fall zu machen und entsprechend abwägen zu können.

Während die ohmschen Verluste der ursprünglichen Komponenten geringer werden, kommen nun neue Komponenten mit derartigen Verlusten hinzu, weiter müssen nun die Kapazitäten mehrerer MOSFETs tausendfach die Sekunde umgeladen werden, etc..

Simulatoren zeigen, dass Designs aus vielen Phasen besonders bei geringer Last durchaus ineffizienter werden können, als solche mit moderater Phasenanzahl.

Das Nutzen der oben genannte Vorteile ist auch eine Frage der tatsächlichen Implementierung des VRMs, es liegt in der Hand der Ingenieure, inwiefern diese genutzt werden.

Besonders dann, wenn mehrere Phasen völlig parallel zueinander fungieren (Pseudo-Doppeln), fallen alle Vorteile abgesehen von ersterem und letzterem grundsätzlich weg.

Somit muss die unbefriedigende Antwort auf diese Frage lauten: Nein.

Diese Thematik ist leider zu fallspezifisch, um eine gute, allgemeine Antwort zu finden. Das ist auch der Grund des Umfang dieses Guides: Er soll das Wissen vermitteln, um sich selbst ein Bild von seinem Fall zu machen und entsprechend abwägen zu können.

- Wie viele Phasen brauche ich?

Es ist empfehlenswert zu planen, jede einzelne (Hardware-)Phase nicht mit mehr als 30A in der höchsten Last zu belasten. Grob gilt somit:

Weiter sollte dann überprüft werden, wie sich die VRM Komponenten des ins Auge geschlossenen Mainboards bei maximaler Stromstärke durch die Wandler verhalten.

Verluste können bei sehr verlustreichen MOSFETs bereits in einen Bereich fallen, der den Kühlkörpern nicht mehr zuzutrauen ist. Natürlich kann aber auch das Gegenteil der Fall sein, bei sehr hochwertigen Lösungen sind 30A pro Phase selbst unter Dauerlast noch kein Limit.

| N[SUB]PH[/SUB] | I[SUB]max[/SUB] | P[SUB]out[/SUB] @1,3V V[SUB]out[/SUB] |

|---|---|---|

3 | 90A | 117W |

4 | 120A | 156W |

6 | 180A | 234W |

8 | 240A | 312W |

Weiter sollte dann überprüft werden, wie sich die VRM Komponenten des ins Auge geschlossenen Mainboards bei maximaler Stromstärke durch die Wandler verhalten.

Verluste können bei sehr verlustreichen MOSFETs bereits in einen Bereich fallen, der den Kühlkörpern nicht mehr zuzutrauen ist. Natürlich kann aber auch das Gegenteil der Fall sein, bei sehr hochwertigen Lösungen sind 30A pro Phase selbst unter Dauerlast noch kein Limit.

- Wie warm darf ein VRM werden?

Bereits im Abschnitt zur Belastbarkeit der VRM Komponenten ist zu sehen, dass Leistungstransistoren aus Silizium in aller Regel nicht bei über 150°C eingesetzt werden können.

Weiter zeigt dort auch das I[SUB]D[/SUB] vs. T[SUB]j[/SUB] Diagramm, dass die maximal spezifizierte Drain Stromstärke ab über 100°C nicht mehr näherungsweise einem linearen Abfall entspricht, die negative Steigung wird hier steiler.

Kondensatoren, die in VRMs eingesetzt werden, sind i.d.R. für maximal 105°C Betriebstemperatur spezifiziert. Bei dieser Temperatur versprechen Hersteller 5000h bis 12000h Lebensdauer, wobei sich diese mit geringerer Temperatur deutlich verlängert.

Durch ihre recht geringen Verluste erreichen sie diese aber quasi nie von selbst, die Gefahr geht hier eher durch das Aufheizen durch andere, verlustreichere Komponenten in direkter Nähe aus.

Grundsätzlich sollte man sich zuerst vergewissern, was genau ein Sensor auf dem Mainboard an welcher Stelle misst, entsprechend muss dann abgewägt werden, welche Temperatur als kritisch anzusehen ist. Mit über 100°C sollte man sich aber nie zufrieden geben.

Weiter zeigt dort auch das I[SUB]D[/SUB] vs. T[SUB]j[/SUB] Diagramm, dass die maximal spezifizierte Drain Stromstärke ab über 100°C nicht mehr näherungsweise einem linearen Abfall entspricht, die negative Steigung wird hier steiler.

Kondensatoren, die in VRMs eingesetzt werden, sind i.d.R. für maximal 105°C Betriebstemperatur spezifiziert. Bei dieser Temperatur versprechen Hersteller 5000h bis 12000h Lebensdauer, wobei sich diese mit geringerer Temperatur deutlich verlängert.

Durch ihre recht geringen Verluste erreichen sie diese aber quasi nie von selbst, die Gefahr geht hier eher durch das Aufheizen durch andere, verlustreichere Komponenten in direkter Nähe aus.

Grundsätzlich sollte man sich zuerst vergewissern, was genau ein Sensor auf dem Mainboard an welcher Stelle misst, entsprechend muss dann abgewägt werden, welche Temperatur als kritisch anzusehen ist. Mit über 100°C sollte man sich aber nie zufrieden geben.

liLinks

VRM Listen: 1151 | 2066 | AM4 | TR4

Weblinks / Mehr zum Thema:

Einführung in die Spannungsversorgung von IluBabe

Geheimnis Spannungswandler von 3DCenter.org

VRM Guide von sinhardware.com

Quellenverzeichnis:

Efficiency of Buck Converter | ROHM

Intersil ISL95712 Datenblatt | Renesas

Intersil ISL6611A Datenblatt | Renesas

sinopower SM4336NSKP Datenblatt | sinopower

TI Power House Blog 2013/10/31 | Texas Instruments

TI Power House Blog 2015/09/18 | Texas Instruments

harwareLUXX Mainboard Tests | Marcel Niederste-Berg

Zuletzt bearbeitet: