Werbung

Mit der heute erfolgten Eröffnung der Fab 34 im irischen Leixlip fällt auch der Startschuss für das High-Volume Manufacturing in Intel 4. Der Compute-Tile von Meteor Lake wird vorerst der einzige Chip sein, der in Millionenstückzahlen in dieser Fertigung vom Band läuft. Im Rahmen unserer ersten Analyse zu Meteor Lake haben wir auch das Thema Intel 4 kurz angeschnitten, wollen uns diesen Prozessschritt nun aber noch genauer anschauen.

War und ist Intel 7 im Grunde nur ein etliche Male verbesserter Prozess in 10 nm, handelt es sich bei Intel 4 um eine deutlichere Weiterentwicklung in der Fertigungstechnik bei Intel. Womöglich wird man mit diesem Schritt auch wieder in Reichweite der Konkurrenz von TSMC kommen - zumindest in einigen Teilbereichen. Den jahrelang vom taiwanesischen Auftragsfertiger aufgebauten Vorsprung, wird man aber vermutlich erst mit Intel 20A und nachfolgenden Schritten egalisieren können.

Intel 4 ist zugleich aber auch ein vorbereitender Schritt für die nächste Mid-Node (so werden die Zwischenschritte bezeichnet), denn Intel 3 baut auf Intel 4 auf. In Intel 3 gefertigt werden sollen die wichtigen Xeon-Prozessoren Granite Rapids (Performance-Core-Xeons) und Sierra Forest (Efficiency-Core-Xeons). Die Client-Prozessoren machen nach Meteor Lake und der Fertigung in Intel 4 mit Arrow Lake gleich den Schritt zu Intel 20A.

Eine Kombination als falscher Materialwahl und einer zu komplexen Prozesskette hat bei Intel für die deutlichen Verzögerungen in der 10-nm-Fertigung geführt. Die Auswirkungen spürt man noch heute. Mit Intel 4 setzt man nun wieder auf EUV, allerdings sind ein paar Jahre vergangen und so soll die Nutzung von EUV für eine Vereinfachung in der Fertigung sorgen.

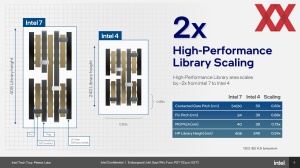

Gegenüber der aktuellen Fertigung in Intel 7 will Intel die Transistordichte für eine High-Performance-Logik um den Faktor zwei verbessern. Die Effizienz soll um mehr als 20 % steigen.

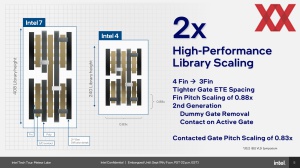

Die höhere Transistordichte ist nur über kleinere Bauelemente und geringere Abstände zwischen diesen möglich. Für eine High-Performance-Bibliothek wird die Höhe dieser von 408 auf 240 nm reduziert. In der Breite schrumpft diese von 60 auf 50 nm (Poly Pitch). Die HP-Bibliothek in Intel 7 kommt demnach auf 24.480 nm², in Intel 4 sind es 12.000 nm². In der HP-Bibliothek selbst sind die Abstände ebenfalls geringer geworden. Der Fin Pitch wird von 34 auf 30 nm reduziert und der Metal Pitch für M0 von 40 auf 30 nm. Fin Pitch und Metal Pitch sind nun identisch, was in der Fertigung zahlreiche Vorteile haben soll.

Mit Intel 7 führte Intel eine Technik namens Contact over active Gate (COAG) ein. Mit Intel 4 wird man eine zweite Generation dieser Technik einsetzen. Der Gate-Kontakt wird hier von außerhalb des aktiven Transistorbereichs in eben diesen versetzt. Die zweite Generation von COAG skaliert mit Intel 4 in die geringeren Abstände in der HP-Bibliothek.

Da in einem Prozessor mehrere HP-Bibliotheken nahe zusammen sitzen, muss zwischen diesen eine Trennung erfolgen können. Entsprechend sind Diffusionsunterbrechnungen zwischen den HP-Bibliotheken und in der zweigeteilten HP-Bibliothek selbst, vorgesehen. Diese Diffusionsunterbrechnungen wird in Intel 7 mittels eines Dummy Gates realisiert. Mit Intel 4 setzt Intel diese Technik fort, kann in der Zelle als Trennung aber auf zwei dieser Diffusionsunterbrechnungen verzichten und setzt nur noch eine ein.

Wikichip schätzt die Transistordichte von Intel 4 auf 123,4 MTr/mm², Intel 7 kommt auf 60,5 MTr/mm². Interessant ist sicherlich auch der Vergleich zu TSMC. Im N5-Prozess kommt der Auftragsfertiger in etwa auf 94,85 MTr/mm.

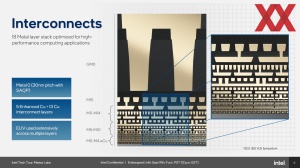

Ein Prozessor ist aus mehreren Schichten aufgebaut, die von den Kontakten, die nach außen in das Package geführt werden, bis hin zu den einzelnen Transistoren führten.

| Lage | Material in Intel 7 | Pitch in Intel 7 | Material in Intel 4 | Pitch in Intel 4 |

| Kontakt-Gate | Wolfram/Kobalt | 54 nm | Wolfram | 50 nm |

| M0 | Kobalt | 40 nm | verbessertes Kupfer | 30 nm |

| M1 | Kobalt | 36 nm | verbessertes Kupfer | 50 nm |

| M2 | Kupfer | 44 nm | verbessertes Kupfer | 45 nm |

| M3 | Kupfer | 52 nm | verbessertes Kupfer | 50 nm |

| M4 | Kupfer | 52 nm | verbessertes Kupfer | 45 nm |

| M5 | Kupfer | 84 nm | Kupfer | 60 nm |

| M6 | Kupfer | 84 nm | Kupfer | 60 nm |

| M7 | Kupfer | 84 nm | Kupfer | 84 nm |

| M8 | Kupfer | 112 nm | Kupfer | 84 nm |

| M9 | Kupfer | 112 nm | Kupfer | 98 nm |

| M10 | Kupfer | 160 nm | Kupfer | 98 nm |

| M11 | Kupfer | 160 nm | Kupfer | 130 nm |

| M12 | Kupfer | 160 nm | Kupfer | 130 nm |

| M13 | Kupfer | 160 nm | Kupfer | 160 nm |

| M14 | Kupfer | 400 nm | Kupfer | 160 nm |

| M15 | - | - | Kupfer | 280 nm |

| (G)M0 | Kupfer | 1.080 nm | Kupfer | 1.080 nm |

| (G)M1 | Kupfer | 11 µm | Kupfer | 4 µm |

Intel 7 setzt auf 17 Metallschichten, Intel 4 auf 18. In der Tabellen oben sind der Fin Pitch und der Contacted Gate Pitch aufgeführt. Als Füllmaterial (Contact Fill) kommt bei Intel 7 Wolfram-Kobalt zum Einsatz, für Intel 4 sieht Intel reines Wolfram vor. Die einzelnen Metallschichten sind als M0 bis M14, bzw. M15 beschrieben. Hinzu kommen noch die letzten Kontaktschichten. Für Intel 7 setzte Intel in den ersten fünf Schichten (M0 bis M4) auf Kobalt und Kupfer. Für Intel 4 wird hier auf verbessertes Kupfermaterial gewechselt, dessen Charakteristiken sich besser eigenen sollen.

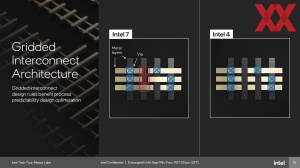

Es gibt einen Grund dafür, warum einige Abstände geschrumpft sind, während andere breiter wurden und es hat hauptsächlich mit der Optimierung des Zelllayouts zu tun. Bei Intel 7 greift Intel für Gate Pitch und M1 auf ein 3:2-Abstandsverhältnis zurück. Für den Fin Pitch, Gate Pitch und die Lagen M0 bis M4 verwendet Intel immer wieder gleiche Abstände, skaliert zwischen Fin Gate und und M2/4 im Verhältnis von 2:3. Intel generiert damit mehr sogenannter Pin Hit Locations. Das Design bietet bessere Verbindungen zwischen den Zellen und einen besseren Zugang auf Blockebene.

Bei der Materialwahl (Kupfer, Kupferlegierungen, Kobalt, etc.) muss Intel schon immer einen Kompromiss aus dem Leitungswiderstand und der Elektromigration eingehen. Reines Kobalt hat gute Eigenschaften für die Elektromigration, aber auch einen relativ hohen Leitungswiderstand. Die Kupferlegierungen können diesen reduzieren, dafür fällt die Elektromigration schlechter aus. Mit dem verbesserten Kupfer will will Intel das Beste aus beiden Welten zusammenführen.

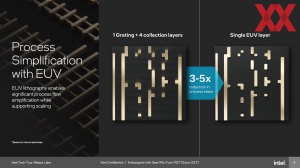

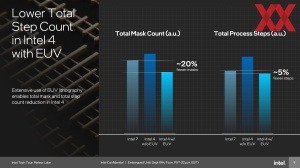

Einsatz von EUV vereinfacht den gesamten Prozess

Intel 4 ist der erste Prozess des Chipriesen, in dem EUV (Extreme Ultraviolet) für einige der Belichtungsschritte verwendet wird. Der Einsatz vereinfacht einige Fertigungsschritte bzw. macht es möglich, mit weniger Belichtungen auszukommen. Um den Faktor drei bis fünf weniger Prozessschritte sollen nun notwendig sein.

Eine zu hohe Komplexität im Zusammenspiel der gewählten Belichtungsschritte und Materialien sorgten für die langanhaltenden Probleme mit der Fertigung in 10 nm, die Intel erst nach der Umbenennung zu Intel 7 überwunden hat. Teilweise musste Intel in den Metallagen M0 und M1 in 10 nm 20 Schritte und 20 Masken verwenden, um diese Bereiche korrekt zu belichten. Dies kostet natürlich Zeit und Geld – war somit für eine Massenfertigung nicht tragbar. Mit Intel 4 sollen es nun deutlich weniger sein und insgesamt sind 60 % weniger Masken notwendig als noch mit Intel 7 aktuell.

Um das Design der Metalllagen und des gesamten Chips zu vereinfachen, hat Intel aber auch neue Designregeln festgelegt. Die Bereiche, in denen TSVs möglich sind, sind limitiert. Somit können Bereiche ohne die TSVs besser optimiert werden und die Fertigung wird vereinfacht.

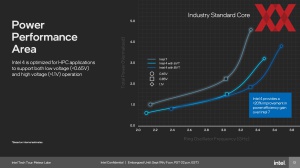

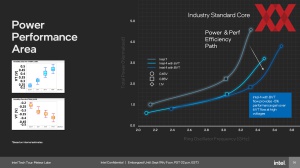

Intel 4 ist auf eine möglichst hohe Effizienz in seinem HP-Design ausgelegt. Dies beinhaltet auch, dass entsprechende Chips auf niedrigen Spannungen von 0,65 V oder auf hohen Spannungen von 1,1 V ausgelegt werden können. Auf die Leistungsaufnahme von Intel 7 normiert, bieten beide Spannungskurven ein um 20 % und besseres Performance/Leistungsaufnahme-Verhältnis.

In wie weit das Compute-Chiplet von Meteor Lake von dieser Flexibilität profitiert, wird sich noch zeigen müssen. Bei einer größeren Auswahl an Chips (HPC, Mobile, ...) wären diese Zahlen deutlich beeindruckender. Für Intel 4 aber steht Meteor Lake im Fokus. Allerdings wird Intel 3 auf Intel 4 aufbauen und so dürfte der Chipriese im nächsten Schritt ebenfalls von diesen Erfahrungen profitieren.

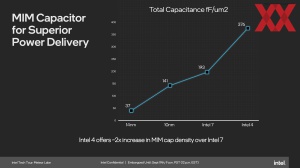

Für die stabile Spannungsversorgung eines Prozessors sind die MIM-Kapazitäten (Metal-Insulator-Metal) wichtig. Die sogenannte SuperMIMs in 10nm Super FinFET kamen auf 141 fF/µm2. Mit Intel 7 konnten 193 fF/µm2 erreicht werden und für Intel 4 kann Intel die Kapazität auf 376 fF/µm2 fast verdoppeln.

Bessere Ausbeute als bei 14 und 10 nm

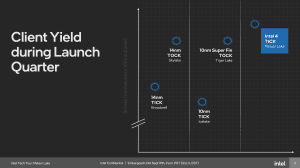

Mit Intel 4 spricht Intel von der besten Ausbeute für einen neuen Prozess in den vergangenen 10 Jahren – also in etwa die Spanne, in der man an 10 nm gearbeitet hat, das sei an der Stelle auch gesagt.

Wie hoch die Ausbeute genau ist, darüber macht Intel natürlich keinerlei Angaben. Zwar konnten wir die Die-Sort-Maschinen in Malaysia sehen, durch die geringe Zeit an der wir neben der Maschine standen, lassen sich daraus keinerlei belastbare Zahlen erstellen. Wir waren aber dennoch verwundert, wie viele Chips aussortiert wurden – egal aus welcher Fertigung diese stammen.

Für Intel ist die Fertigung in Intel 4 in der ersten Phase aber dennoch wohl recht erfolgreich – auch weil die Chips vergleichsweise klein sind.

Auf SoC-Ebene bietet Intel 4 eine Reduzierung der Leistungsaufnahme von bis zu 40 % in einem Iso-Frequenzvergleich oder einen um mehr als 20 % höheren Takt. Darüber hinaus bietet Intel 4 eine deutlich höhere Transistordichte im Vergleich zu Intel 7. Auf dem Papier ist Intel 4 sogar besser als N3 von TSMC oder 3GAE von Samsung.

Abschließend bleibt festzuhalten, dass Intel über eine sorgfältige Skalierung der Standardzellen und die Vereinfachung der darunter liegenden Prozessschritte die Komplexität deutlich reduziert hat. Zudem kehrt man zu Materialien zurück, die man besser im Griff hat und auch schon hatte. Die Einführung der EUV-Belichtung hilft sowohl in der Variabilität der Fertigung, wie auch der Komplexität von Masken sowie Prozessschritten und verringert deren Anzahl deutlich.

Dies alles geschieht in Vorbereitung auf Intel 3. Neben den eigenen Produkten will man Intel 3 auch über seine Intel Foundry Services (IFS) externen Kunden anbieten. Intel 3 soll gegenüber Intel 4 um weitere 18 % im Performance/Watt-Verhältnis zulegen. Zugleich wird Intel 3 der letzte Prozess von Intel sein, der noch auf die FinFETs setzt. Danach wird Intel auf das RibbonFET-Design wechseln und auch PowerVia als Backside-Power-Delivery-Technik wird dann Einzug halten.