Werbung

Eine Überraschung hielt AMD bis zuletzt noch zurück und sprach auf der Keynote der Computex über den Stand der Entwicklung der 3D-Packaging-Technologie, den man inzwischen erreicht hat. Vor einigen Tagen gab es bereits Gerüchte zu einem Milan-X getauften EPYC-Prozessor, der mit gestapeltem SRAM ausgestattet sein soll. Nicht für die EPYC-Serie aber stellte AMD eine solche Technik nun vor, sondern für die Ryzen-Prozessoren.

Entwickelt hat AMD die Technik gemeinsam mit TSMC, die für AMD die wichtigen CCDs mit den Zen-Rechenkernen und auch die GPUs fertigen. TSMC hat bereits zahlreiche 3D-Packaging-Technologien im Angebot und eben auf dieses Portfolio scheint AMD nun zurückzugreifen. In einem Nebensatz erwähnt Dr. Lisa Su zudem, dass dies auch für zukünftige HPC-Produkte zum Einsatz kommen wird. Milan-X scheint demnach ebenso real zu sein, wie die Ryzen-Prozessoren mit 3D V-Cache.

Es handelt sich laut AMD um einen Prototypen eines Ryzen-5000-Prozessors, der mit 64 MB zusätzlichem SRAM pro CCD ausgestattet wurde. Da sich AMD für den Prototypen für eine Variante mit zwei CCDs entschieden hat, kommen wir hier also auf 2x 32 MB L3-Cache, die sich ohnehin schon in den CCDs befunden haben und fügen noch weitere 2x 64 MB des neuen 3D V-Cache hinzu.

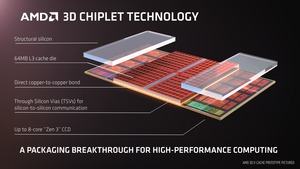

Der 3D V-Cache ist mittels der 3D-Packaging-Technologie direkt über TSVs (Through-silicon Via) mit dem CCD verbunden. Die Datenrate dieser Verbindung beträgt mehr als 2 TB/s. Sogenanntes "Structural Silicon" baut den Bereich höher auf, wo sich kein 3D V-Cache befindet, sodass die Bauhöhe des CCDs wieder gleichmäßig ist.

Auf den Renderings des 3D V-Cache bzw. des neuen Zen-3-CCDs mit diesem Speicher ist zu erkennen, dass sich dieser genau über dem Bereich des CCDs befindet, wo sonst auch schon der L3-Cache vorhanden ist. Die Bereiche, in denen sich die Zen-3-Kerne befinden, werden hingegen ausgespart. Dies verhindert, dass der 3D V-Cache die heißen Kerne bedeckt. Das Structural Silicon sorgt für eine Durchkontaktierung der Kerne zum Heatspreader.

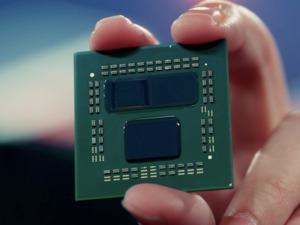

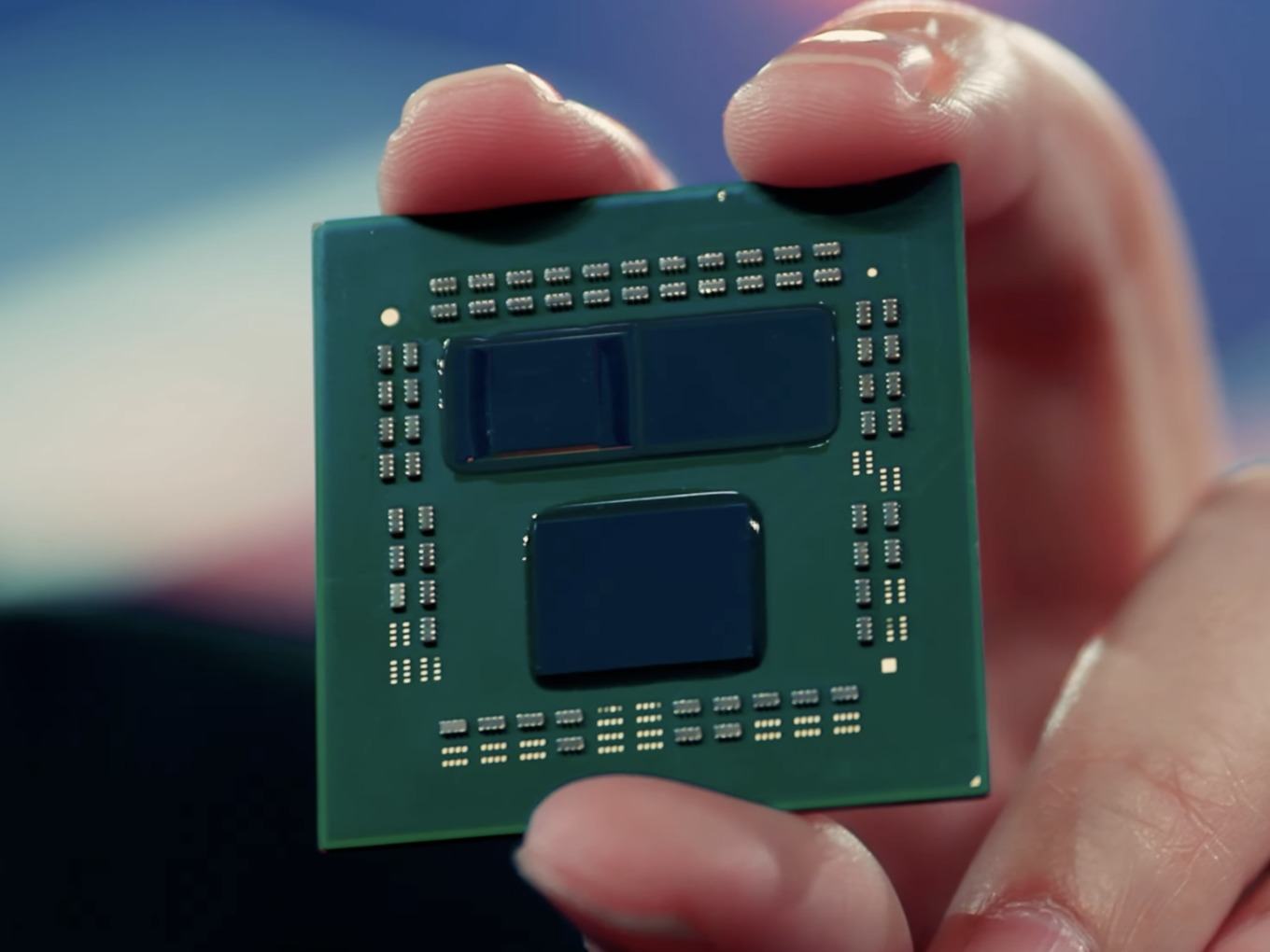

In der Keynote hielt Lisa Su einen Prototypen in die Kamera. Bei diesem handelte es sich um einen Ryzen-5000-Prozessor mit zwei CCDs. Um den Unterschied zu demonstrieren, verfügte aber nur ein CCD über den 3D V-Cache (links).

Hypothetisch sähen die Prozessoren bzw. der angebotene Cache dann wie folgt aus:

| L3-Cache | 3D V-Cache | Gesamt | |

| Ryzen 9 5950X | 64 MB | . | 64 MB |

| Ryzen 9 5950X mit 3D V-Cache | 64 MB | 128 MB | 192 MB |

| Ryzen 9 5900X | 64 MB | - | 64 MB |

| Ryzen 9 5900X mit 3D V-Cache | 64 MB | 128 MB | 192 MB |

| Ryzen 9 5800X | 32 MB | - | 32 MB |

| Ryzen 9 5800X mit 3D V-Cache | 32 MB | 64 MB | 96 MB |

| EPYC 7763 | 256 MB | - | 256 MB |

| EPYC 7763 mit 3D V-Cache | 256 MB | 512 MB | 768 MB |

Ein Ryzen-Prozessor mit zwei CCDs bringt es auf 128 MB 3D V-Cache und insgesamt auf 192 MB an L3-Cache. Bei einem CCD sind es zusätzliche 64 MB und damit insgesamt 96 MB. Bei den EPYC-Prozessoren, sollte Milan-X sieht dies dann ganz ähnlich aus, nur sprechen wir hier über andere Cache-Größen. Ein EPYC-Prozessor mit acht CCDs kommt ohnehin schon auf 256 MB L3-Cache. Der 3D V-Cache brächte zusätzliche 512 MB ins Spiel, sodass wir über insgesamt 768 MB sprechen würden. In welcher Form AMD seine Ryzen- und EPYC-Prozessoren aber mit 3D V-Cache ausstatten wird, bleibt abzuwarten.

Um die Vorteile des 3D V-Cache zu demonstrieren präsentierte AMD einen Benchmark. Gears 5 lief einmal auf einem Ryzen 9 5950X und einmal mit einem 3D V-Cache Prototypen mit 12 Kernen. Beide Prozessoren arbeiteten mit einem fixen Takt von 4 GHz. Während der Ryzen 9 5950X auf 184 fps kam, erreicht der Ryzen-Prozessor mit 3D V-Cache 206 fps. AMD spricht von einem durchschnittlichen Leistungsplus von 12 % über alle Anwendungen. Bei Spielen sollen es 15 % sein. Wir liegen hier also auf Niveau eines typischen IPC-Plus durch eine neue Mikroarchitektur.

Gegen Ende des Jahres sollen die ersten Produkte mit 3D V-Cache vorgestellt werden. Ein Ryzen-Refresh mit diesem zusätzlichen Speicher ist also mehr als wahrscheinlich – bevor man dann zu den ersten Zen-4-Prozessoren kommt.

Weitere News von AMD auf der Computex 2021:

- Ryzen 7 5700G und Ryzen 5 5600G ab 5. August für DIY-Bauer

- RDNA 2 goes Mobile: Radeon RX 6800M, 6700M und 6600M kommen ins Notebook

- Auch für GeForce-Karten: FidelityFX Super Resolution kommt am 22. Juni

- AMD Advantage: Ein Anforderungskatalog für einen guten Gaming-Laptop

Update: AMD beantwortet einige Fragen zum 3D V-Cache

Im Nachgang zur Keynote hatten wir die Gelegenheit mit Samuel Naffziger von AMD zu sprechen. Dieser konnte uns einige Fragen zum 3D V-Cache beantworten.

Zunächst einmal stellte AMD klar, dass es Ende 2021 den Produktionsstart der ersten Ryzen-Prozessoren mit 3D V-Cache geben wird. Ob diese Prozessoren dann noch 2021 verfügbar sein werden oder nicht und weitere Details werden später folgen. Es wird also definitiv solche Prozessoren (basierend auf der Zen-3-Architektur) geben. Aktuell fertigt man den 3D V-Cache in der gleichen Strukturbreite wie das CCD – also 7 nm, allerdings in einer optimierten Form und damit erreicht man auch die extreme Dichte.

Aus technischer Sicht stellte AMD klar, dass es sich um eine einzelne Lage an SRAM handelt, wir also noch keinen gestapelten SRAM sehen, sondern dieser eben auf dem CCD gestapelt wird. 64 MB in einer Lagebedeutet aber auch, wenn AMD hier weitere Lagen hinzufügt, kommen in der aktuellen Version mit jeder Lage weitere 64 MB hinzu. Dies dürfte für die EPYC-Prozessoren von Bedeutung sein, denn hier sollen bis zu vier Lagen zum Einsatz kommen.

Der Einfluss auf die Temperaturen soll vernachlässigbar sein, da der SRAM keine große Abwärme erzeugt. Ebenso verhält es sich bei der Leistungsaufnahme. Der mittels 3D V-Cache vergrößerte L3-Cache kann sogar dahingehend hilfreich sein, da die Hit-Rate im Cache ansteigt und weniger erneute Zugriffe auf den Speicher notwendig werden. Hinzu kommt, dass der bestehende Zen-3-CCD bereits für den 3D V-Cache vorbereitet ist und sich sämtliche Control- und Power-Logic im CCD befindet. Daher können 64 MB an 3D V-Cache auch in 36 mm² gepackt werden. Damit der CCD mit 3D V-Cache auf die gleiche Bauhöhe wie der IOD kommt, wird er flach geschliffen und dann der 3D V-Cache aufgesetzt.

Auf die Frage, ob die Latenzen im 3D V-Cache höher als im L3-Cache des CCDs sind antwortete AMD, dass es zwar eine geringfügige Erhöhung gäbe, diese aber moderat ausfällt und keinesfalls mit dem zu vergleichen ist, was bei Zugriffen auf den entfernten CCD an Latenzen anfällt.

Der existierende L3-Cache des CCDs wird um den 3D V-Cache ergänzt. Anpassungen der Software, damit dieser Cache angesprochen werden kann, gibt es nicht.

2. Update

Im Rahmen einer Episode der YouTube-Serie "The Bring Up" hat AMD einige weitere interessante Details zum 3D V-Cache verraten.

So wird der CCD um 180 ° gedreht und 95 % des Chips werden abgeschliffen. Am Ende bleiben nur noch 20 µm des ansonsten 400 µm dicken Chips als aktives Silizium übrig. Auf diese dünne Schicht wird dann der 3D V-Cache gestapelt. TSVs aus Kupfer stellen bekanntermaßen die Verbindung zwischen dem CCD und SRAM her. Laut AMD reicht die Adhäsion der Kupfer-Kontaktpunkte der TSVs auf beiden Seiten aus, um die beiden Chips miteinander zu verbinden.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen