Werbung

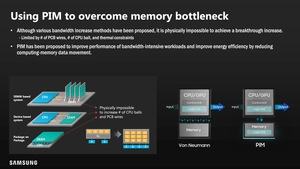

Anfang des Jahres stellte Samsung den HBM-PIM, den ersten HBM-Speicher mit eingebauter AI-Engine, vor. Einige Details kennen wir also bereits, auf der Hot-Chips-Konferenz sprach Samsung aber etwas genauer über die Motivation und die Ziele hinter einem solchen Speichertyp. Auch hat man bereits erste Produkte mit diesem Speicher ausgestattet und testet diese zusammen mit seinen potenziellen Kunden.

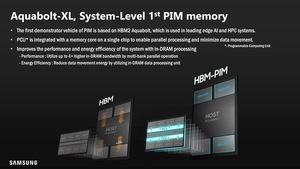

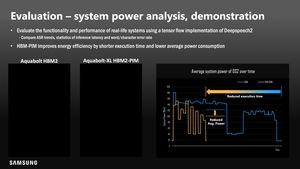

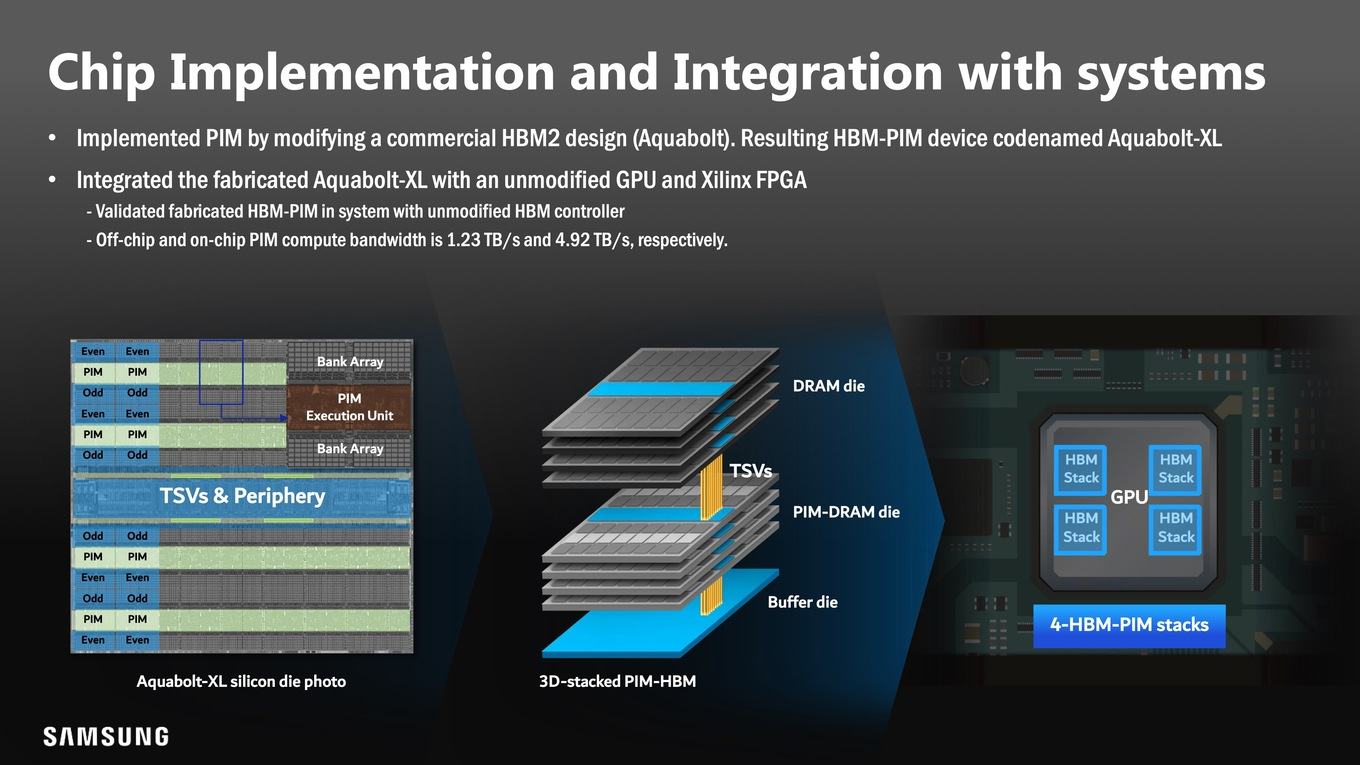

Beim Aquabolt-XL handelt es sich um HBM2-Speicher, der eine Processing-in-Memory (PIM) Architektur enthält. AI/ML- und HPC-Anwendungen sollen von einem solchen Speicher profitieren können, da die zu verarbeitenden Daten vorverarbeitet werden können. Die direkte Nähe der Daten zu den verarbeitenden Einheiten im Speicher ist hier natürlich von Vorteil.

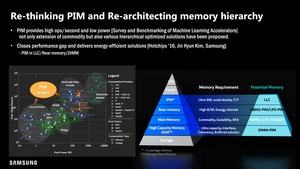

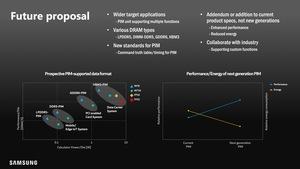

Ein PIM ist laut Samsung eine weitere Ebene in der Speicherhierarchie. GPUs und CPUs haben Caches, darauf folgt ein sogenannter Near Memory (HBM, GDDR), der auch als Last Level Cache (LLC) bezeichnet wird. Darauf folgt der Speicherpool eines Nodes, der Arbeitsspeicher, der in solchen Systemen als kohärenter Speicher von vielen Einzelkomponenten beansprucht wird. Ein PIM soll sich zwischen dem LLC und dem Arbeitsspeicher platzieren bzw. dort seinen Dienst verrichten und seine Vorteile ausspielen. Noch arbeitet Samsung an einem HBM2-PIM, geplant sind aber schon Varianten in Form eines HBM3-PIM und auch LPDDR- und DDR-Speicher soll es in einer PIM-Variante geben.

Über all dort, wo eine gewisse Effizienz gefragt ist oder die Leistung durch eine Vorverarbeitung optimiert werden kann, soll ein PIM-Speicher zum Einsatz kommen.

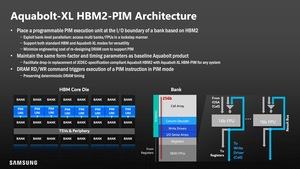

Den Aufbau des HBM2-PIM hat Samsung nun etwas genauer erläutert. Zwar kennen wir auch hier bereits einige Details, es gibt aber auch einige weitere Informationen.

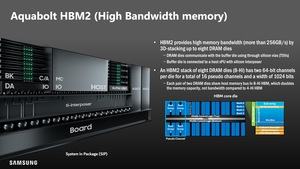

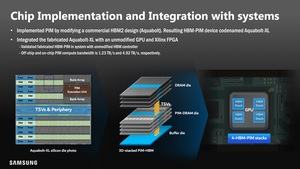

So verwendet Samsung für den HBM2-PIM einen Buffer Die, vier Lagen des Speichers mitsamt der Recheneinheiten (FIMDRAM) und weitere vier Lagen klassischen HBM2-Speichers (DRAM). Der Buffer-Die ist über einen Silicon-Interposer direkt mit dem Host-Prozessor (dies kann ein FPGA oder eine GPU sein) verbunden. TSVs stellen die Verbindungen zwischen dem Buffer-Die, den FIMDRAM- und den DRAM-Lagen her.

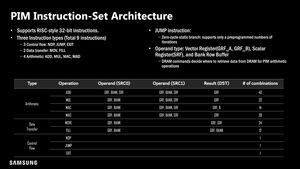

Jede Lage des FIMDRAM verfügt über jeweils 32 Rechenkerne. Organisiert sind diese in 16 Lanes zu jeweils zwei FP16-Recheneinheiten. Die Rechenleistung eines kompletten Speicherchips mit vier FIMDRAM-Layern beträgt also 4 x 32 x 32 Byte x 300 MHz = 1,2 TFLOPS für FP16-Berechnungen. Um die Rechenkerne ansprechen zu können, gibt es natürlich auch hier ein bestimmtes Instruction Set, welches in Ausschnitten RISC-Instruktionen mit 32 Bit unterstützt.

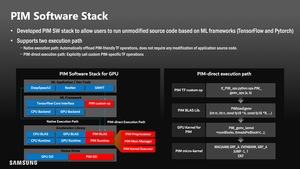

Der HBM2-PIM kann in verschiedenen Modi betrieben werden. Zunächst einmal kann er ohne jegliche Einbußen in der Bandbreite als klassischer HBM2 verwendet werden. Dann ist es möglich, dem PIM gewisse Bereiche des Speichers zuzuweisen, die exklusive der Vorverarbeitung zur Verfügung stehen. Die Bandbreite des Speicher als solches soll dadurch aber nicht beeinflusst werden, da sogenannte Pseudo-Channels den Speicher weiterhin schnell genug anbinden – auch wenn gewisse Bereiche ausgenommen sind.

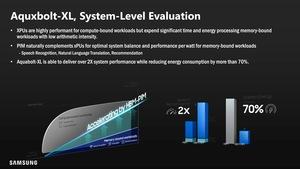

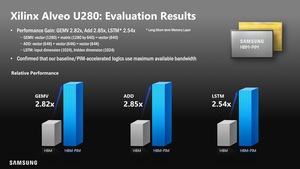

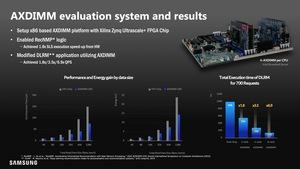

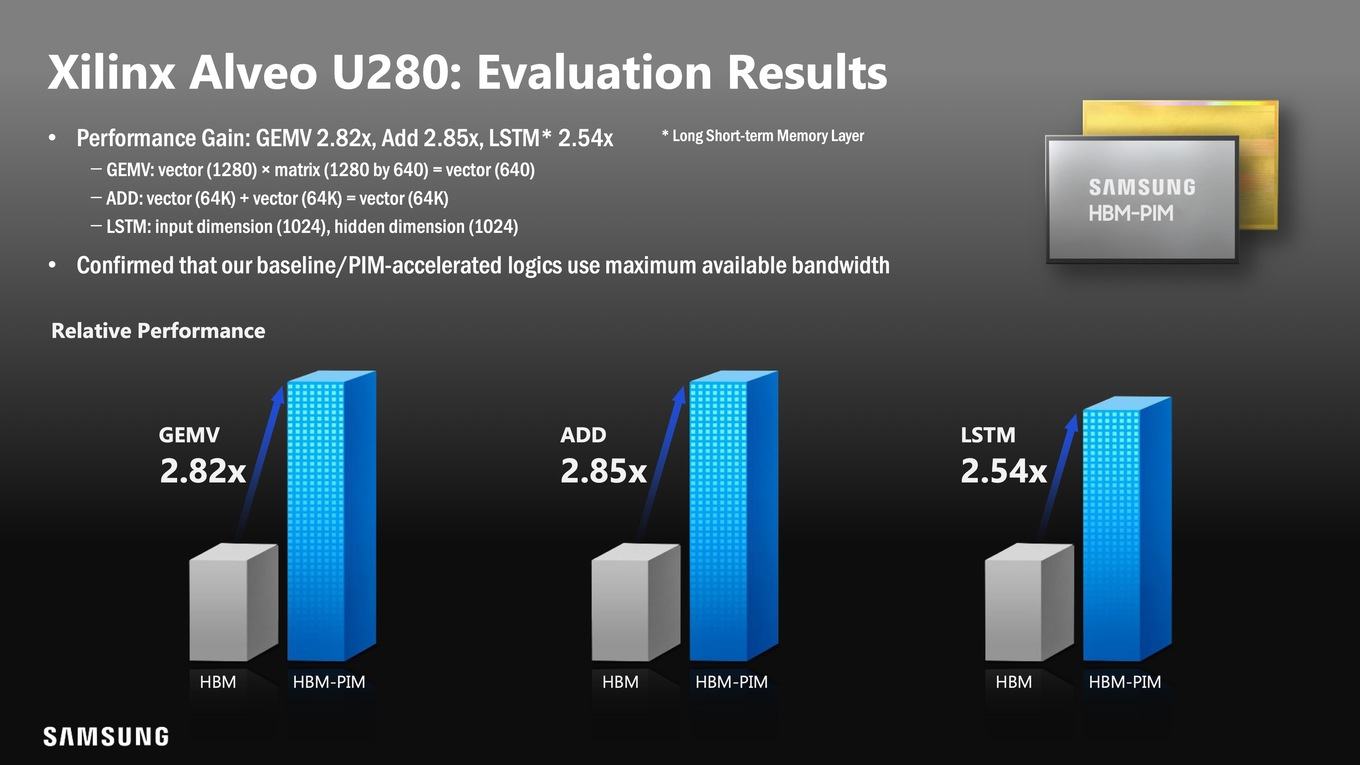

Getestet wurde der Aqualbolt-XL, so der Codename des HBM2-PIM, mit einem Xilinx FPGA. Der Speichercontroller für den HBM-Speicher muss auf Seiten des FPGAs nicht angepasst werden. Mit vier HBM2-PIM-Stacks (und einem 4.096 Bit breiten Speicherinterface) bliebt die Speicherbandbreite bei 1,23 TB/s. On-Chip, also im HBM2-PIM selbst, lag die Bandbreite bei 4,92 TB/s.

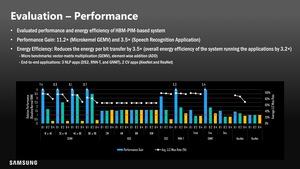

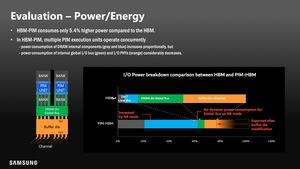

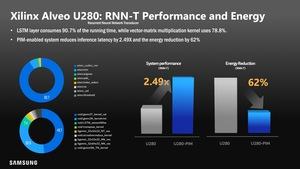

Je nach Anwendung und den gewählten Parametern für die Daten steigt die Leistung des Xilinx Alveo U280 um den Faktor 2,5 bis 2,8 an. In einigen weiteren Beispielen nennt Samsung auch weitaus größere Leistungssteigerungen. Auch die Energieeffizienz kann für solche Anwendungen deutlich gesteigert werden. Hier spricht Samsung von bis zu 70 %. Grundsätzlich verbraucht der Aquabolt-XL zunächst einmal 5,4 % mehr als der klassische HBM2 ohne die Recheneinheiten.

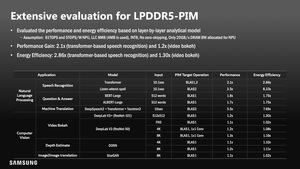

Ein nächster Schritt soll nun die Ausweitung des PIM in andere Speichertypen sein. Konkret spricht Samsung von einem LPDDR5-PIM. Auch DIMM-PIMs sind in Planung. Konkrete Produktankündungen zum HBM2-PIM gibt es aber noch nicht.