Werbung

Unser Besuch der ITT-US von Intel fördert die ersten und weiteren Details zur Panther Lake und Clearwater Forest zu Tage. Die Einladung nach Phoenix, genauer gesagt Chandler im US-Bundesstaat Arizona erfolgte aber auch, weil hier mit der Fab 52 das neueste Chipwerk von Intel steht, wo die Compute-Tiles in Intel 18A gefertigt werden.

Anfang 2023 konnten wir die Fab 23 von Intel in Israel besuchen. Dort fand damals die Fertigung in Intel 7 statt. Nach der Fertigung der Chips ermöglichte uns der Besuch der Packaging-Werke in Malaysia Mitte 2023 auch die weiteren Schritte hin zu einem fertigen Prozessor zu verfolgen.

Solche Einblicke sind selten, denn die Chiphersteller wollen sich ungern in die Karte blicken lassen. Zudem bergen solche Einblicke auch die Gefahrt, dass Firmengeheimnisse nach Außen gelangen. Die schon 2023 strickten Vorgaben haben sich auch in diesem Jahr nicht gelockert – eher im Gegenteil. Fotos aus dem Inneren der Fab waren uns nicht erlaubt. Daher konzentrieren wir uns bildlich auf die äußere Infrastruktur. Später aber können wir auch noch einen Blick ins Innere werfen.

Zunächst ein paar Fakten: Intel hat bereits 1980 die erste Fab am Ocotillo-Kampus in Chandler eröffnet. Insgesamt umfasst der Ocotillo-Kampus eine Fläche von 2,5 Millionen Quadratmetern, von denen aber noch längst nicht alles erschlossen ist. Neben dem Packaging findet in Chandler vor allem die Chipfertigung statt.

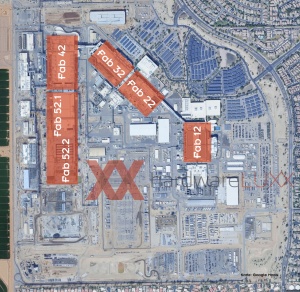

Über die vergangenen Jahrzehnte sind inzwischen fünf Chipwerke entstanden, eine sechste soll gebaut werden:

- Fab 12: ab den 1990er Jahren

- Fab 22: ab 1996

- Fab 32: ab 2007 Chips in 22/14/10 nm auf 300-mm-Wafer

- Fab 42: ab 2020 Chips in 10/5 nm auf 300-mm-Wafer

- Fab 52: ab 2024 Chips in 2 nm auf 300-mm-Wafer

Die Erweiterung in Form von Fab 62 (südlich der Fab 52) befindet sich aktuell im Bau. Für Fab 52 und 62 investiert Intel insgesamt 32 Milliarden US-Dollar. Fab 52 wurde in zwei Modulen ausgeführt: Fab 52.1 und Fab 52.2. Auf dem unten eingebetteten Satellitenbild ist das Modul 52.1 bereits fertiggestellt, während sich Modul 52.2 noch im Bau befindet. Auch innerhalb des Reinraums verwendet Intel die Modulbauweise und spiegelt die Aussattung im Ausbau, was die Planung der Anlagen vereinfacht.

Auf den Bildern kaum rüberzubringen sind die enormen Dimensionen der Gesamtanlage und einzelnen Gebäude. Von Fab 12 bis in Fab 52 gibt es geschlossene Brücken, welche die einzelnen Gebäude miteinander verbinden. Somit müssen die Gebäude nicht verlassen werden, wenn man zwischen diesen wechseln muss. Die Länge dieses Weges berägt in etwa 1,6 km. Aber nicht nur das gesamte Gelände hat gewaltige Ausmaße, auch der Blick auf die Infrastruktur zeigt, dass eine moderne Chipfertigung weit mehr ist, als nur ein Reinraum mit Belichtungsmaschinen.

Luft, Wasser und dutzende Chemikalen müssen vorgehalten, gereinigt und später auch wieder ausgeschieden bzw. entsorgt werden. Die neue Fab 52 verbraucht pro Tag 34 Millionen Liter Wasser. Das Wasser wird allerdings nicht einfach verbraucht und dann in die Kanalisation eingeleitet, sondern Intel hat hier einen Recycling-Prozess etabliert, der einen Großteil des Wassers immer wiederverwendet. Natürlich ist es dennoch ein gewisser Wiederspruch, dass eine solch wasserintensive Industrie ausgerechnet in einer Region aufgebaut wird, in denen Wasser (bis auf einige Extremregenereignisse) eher ein seltenes Gut ist.

Ähnliches gilt auch für den Stromverbrauch. Die gesamte Anlage verbraucht im Betrieb etwa 100 MW an Strom. Dieser wird laut Intel zu 100 % durch erneuerbare Energien gedeckt. Vor Ort werden diese erneuerbaren Energien aber nicht erzeugt, sondern Intel kauft die entsprechenden Kapazitäten an anderer Stelle und verbucht diese dann in Chandler auf den dortigen Verbrauch. Über den Parkplätzen sind Solarpanele mit einer Peak-Leistung von 3,3 MW verbaut. Diese können also nur einen Bruchteil der Energie decken, die hier verbraucht wird.

Bevor die eigentliche Fertigung betreten konnten, mussten wir uns zunächst umziehen. Die sogenannten Bunny-Suits dienen dem Schutz des Reinraums vor jeglicher Kontamination. Selbst ein einziges Staubkörnchen oder Rückstände von Make-up und Haargel können Verunreinigungen verursachen und sind daher strikt verboten. In einem Reinraum der Kategorie 1 darf sich auf 28 Liter Luftvolumen nur ein einziges Staubpartikel befinden. Durch eine Schleuse gelangt man zunächst in den Umkleidebereich.

Der komplette Bunny-Suit besteht aus Überziehern für Kopf und Füße sowie speziellen antistatischen Handschuhen. Darüber wird ein Einteiler getragen, in den man hineinschlüpfen muss. Abschließend folgen nochmals Handschuhe, und selbst einfache Utensilien wie Papier und Stift müssen für den Reinraum zertifiziert sein. Erst durch eine weitere Schleuse gelangt man schließlich in die eigentliche Fertigung. Dort wird das gesamte Luftvolumen dreimal pro Minute ausgetauscht.

Bis ein Wafer vollständig belichtet ist und daraus Chips geschnitten werden können, sind hunderte bis tausende Prozessschritte notwendig – das dauert mehrere Wochen bis Monate. In sogenannten Front Opening Universal Pods (FOUP) werden die Wafer an einem Deckenschienensystem mit bis zu 3 m/s transportiert. Pro Tag kann ein solcher FOUP bis zu 150 km zurücklegen. Jeder FOUP enthält 25 Wafer, zu denen das Personal keinen direkten Kontakt hat. Die Fachkräfte bedienen und warten ausschließlich die Maschinen. Der Industriestandard liegt derzeit bei einem Waferdurchmesser von 300 mm, und ein Wechsel auf 450 mm gilt als schwierig, da die gesamte Infrastruktur auf 300 mm ausgelegt ist – ein klassisches Henne-Ei-Problem. Größere Wafer würden zwar potenziell die Ausbeute erhöhen, doch der Aufwand wäre enorm.

Auch wenn sich die FOUPs und die darin befindlichen Wafer relativ schnell an der Decke bewegen, so ist die Durchlaufzeit des blanken Wafers bis zur vollen Belichtung relativ lang. Die genauen Zeiten hängen auch vom jeweiligen Produkt ab und so genannte Hot Lots können auch schneller durch die Fertigung geschleust werden. In etwa vier Monate dauert es im Schnitt, bis ein Wafer komplett bearbeitet ist, Hot Lots können auch in wenigen Wochen bearbeitet werden. Rapidus will sich durch besonders schnelle Fertigungszeiten auszeichnen, was auch ein komplexeres FOUP-System zur Folge hat.

Trotz der Reinraumbedingungen kann es zu Verunreinigungen kommen. Jeder Wafer wird daher kontrolliert und gegebenenfalls gereinigt. Diese Überwachung übernimmt das sogenannte DREAM-Team (Defect Remediation Engineering and Metrology), das Fehlerquellen identifiziert und Gegenmaßnahmen einleitet.

Neben den Reinräumen existiert umfangreiche Infrastruktur: Das Gebäude umfasst mehrere Ebenen, wobei der Reinraum die zentrale Etage bildet. Darüber und darunter verlaufen Versorgungsschichten für Wasser, Energie, Chemikalien und Gase. Externe Gebäudeteile übernehmen Wasseraufbereitung und Notstromversorgung.

Die mehrfache Belichtung der Wafer wechselt sich mit ein Ätzprozessen ab und bildet somit die Halbleiterstrukturen: Die moderne Belichtung und Verarbeitung von Wafern im Chipherstellungsprozess erfolgt heutzutage für die modernsten Chips primär durch Extreme-Ultraviolet-(EUV)-Lithographie, die bei einer Wellenlänge von 13,5 nm arbeitet. Dieser komplexe Prozess beginnt mit der Vorbereitung des Siliziumwafers. Zunächst wird der Wafer bei Temperaturen von 120 bis 150 °C für etwa 10 Minuten gebacken, um jegliche Feuchtigkeit zu entfernen. Anschließend erfolgt eine chemische Reinigung mit speziellen Lösungen wie der RCA-Reinigung, um organische und anorganische Verunreinigungen zu beseitigen. Nach der Reinigung wird ein Haftvermittler wie HMDS aufgetragen und schließlich der Photoresist mittels Spin-Coating bei 3.000 bis 5.000 Umdrehungen pro Minute gleichmäßig aufgebracht.

Die eigentliche Belichtung erfolgt durch eine präzise Ausrichtung zwischen Wafer und Photomaske mit Nanometer-Genauigkeit - moderne ASML-Systeme erreichen hierbei Overlay-Leistungen von unter 2 nm. Die EUV-Lichtquelle erzeugt durch einen gepulsten Hochleistungslaser, der 50.000 Mal pro Sekunde auf Zinntröpfchen trifft, ein intensives Plasma mit der erforderlichen 13,5-nm-Strahlung. Diese Strahlung wird über Spiegelsysteme - bestehend aus über 100 extrem dünnen Silizium- und Molybdänschichten - auf den mit Photoresist beschichteten Wafer fokussiert. Da EUV-Licht von den meisten Materialien absorbiert wird, findet der gesamte Prozess im Vakuum statt.

Nach der Belichtung wird der Wafer einem Post-Exposure-Bake (PEB) bei Temperaturen zwischen 95 bis 130 °C für wenige Minuten unterzogen, wodurch die chemischen Reaktionen im Photoresist stabilisiert werden. Die Entwicklung erfolgt durch Eintauchen in eine Entwicklerlösung, die selektiv die belichteten Bereiche des Photoresists auflöst und dadurch das gewünschte Muster freilegt.

Zum Schutz der kostspieligen Photomasken vor Partikelverschmutzung während des Belichtungsprozesses werden EUV-Pellicles eingesetzt - ultradünne Membranen aus Materialien wie Kohlenstoffnanoröhren mit einer EUV-Transmission von über 90 % und der Fähigkeit, Temperaturen bis 1.500 °C im Vakuum zu widerstehen.

Bei unserem Gang durch die Fab 52 sind wir dann auch auf die für Intel 18A eingesetzten Maschiene gestoßen. Auf dem obigen Bild zu erkennen ist eine ASML TWINSCAN NXE:3800E. Diese erreicht laut ASML eine Auflösung von 13 nm und einen Waferdurchsatz von 220 Wafern pro Stunde. Bei TWINSCAN NXE:3800E handelt es sich um den Nachfolger des TWINSCAN NXE:3600D und TWINSCAN NXE:3400C, die in den Chipfabriken dieser Welt für die Fertigung in 7 und 5 nm zum Einsatz kommen. Fertigungsprozesse für 3 und 2 nm werden vermehrt die TWINSCAN NXE:3800E zum Einsatz bringen.

Neben den kleineren Strukturen werden die neuen Scanner meist auch für einen höheren Durchsatz optimiert. Mit dem TWINSCAN NXE:3800E will ASML um bis zu 33 % mehr Wafer pro Stunde durchsetzen können, als dies mit dem TWINSCAN NXE:3600D möglich ist. Aber nicht nur Maschinen von ASML stehen in der Fab 52. Auch zahlreiche andere Zulieferer konnten wir entdecken, aufgrund der Geheimhaltung ist es uns aber nicht möglich, auf diese zu referenzieren.

Noch einmal: Die Dimensionen eines solchen Kampus mit all den Anlagen lässt sich kaum via Fotos und schon gar nicht über den Text transportieren. Die komplette Infrastruktur rund um die Fabs ist extrem aufwendig und belegt in etwa noch einmal die Fläche des eigentlichen Reinraums – von den mehreren Etagen der Gebäude einmal abgesehen. Der Einblick in die aktuell modernste Fertigung bei Intel darf als einmalige Gelegenheit verstanden werden. Dass TSMC seine Tore in dieser Form öffnet, ist nicht zu erwarten.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Intel stellte uns noch einige Drohnenaufnahmen der Fab 52 von Außen sowie einige weitere Aufnahmen aus dem Inneren zur Verfügung. Das Video gibt womöglich einen besseren Eindruck der Dimensionen der Anlage in Chandler.

Wafer und Chips in Intel 18A

Das, was Intel in der Fab 52 fertigt, konnten wir uns ebenfalls noch einmal genauer anschauen. Konkret handelt es sich dabei um die die Compute-Tiles für Clearwater Forest mit 24 E-Kernen organisiert in sechs Modulen.

Sehr gut sind die E-Kern-Cluster mit jeweils vier Kernen zu erkennen. Je sechs dieser Cluster bilden den Compute Tile. Auf den Bildern ist zu erkennen, dass vier Cluster enger zusammenstehen, während zwei weitere etwas getrennter davon platziert sind. Die Gründe dafür kennen wir nicht.

Auch die Chips auf dem Wafer mit den Compute-Tiles für Panther Lake haben wir abgelichtet. Hier deutlich zu erkennen sind die zwei E-Kern- sowie das einzelne LPE-Cluster. Ebenfalls zu erkennen sind die vier P-Kerne direkt unter den beiden E-Kern-Clustern. Dazwischen befindet sich der shared L3-Cache. Auch die NPU sowie der Memory Side Cache sind zu erkennen.

Hardwareluxx hat die Informationen zu diesem Artikel von Intel durch Einladung des Redakteurs zur Intel Tech Tour US in Phoenix, im Bundesstaat Arizona, erhalten.