Werbung

Mit Intel 18A und Intel 18A-P will Intel sowohl eigene Produkte als auch Chips für Kunden in einem der modernsten Fertigungsprozesse herstellen. Für den nächsten Schritt, Intel 14A, plant Intel zahlreiche Neuerungen – darunter die zweite Generation der RibbonFETs sowie PowerDirect als Weiterentwicklung der rückseitigen Stromversorgung PowerVia – und das alles unter Einsatz der High-NA-EUV-Lithografie.

Mit Intel 14A möchte Intel neue Designrichtlinien einführen, die auf den Erfahrungen (Learnings) aus der Entwicklung zwischen Intel 18A und Intel 18A-P basieren. Dabei sollen die Designregeln so angepasst werden, dass größere Spannungsbereiche möglich sind, wodurch Intel 18A-P letztlich eine höhere Leistung erreichen kann. Besonders KI- und HPC-Chips sollen davon profitieren.

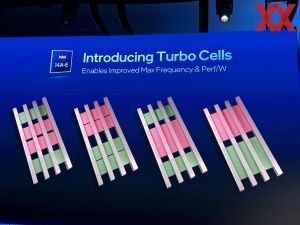

Eine zentrale Rolle in der Intel-14A-Fertigung sollen die sogenannten Turbo Cells spielen. Dabei handelt es sich um ein anpassbares Zellkonzept, das gezielt auf kritische Signalpfade in CPU- und GPU-Designs abzielt. Diese Pfade stellen die langsamsten Signalwege innerhalb eines Chips dar und bestimmen somit die maximal erreichbare Taktfrequenz. Ihre Beschleunigung kann die Gesamtleistung eines Prozessors erheblich steigern. Traditionell kommen in diesen Bereichen besonders schnelle, aber energiehungrige Transistoren zum Einsatz. Die Turbo Cells bieten laut Intel eine elegantere Lösung: Sie erhöhen gezielt den Drive Current in hochdichten Zellbibliotheken (sogenannten Short Libraries), ohne dabei die Flächen- oder Energieeffizienz übermäßig zu beeinträchtigen.

Für den 14A-Knoten stellt Intel drei Zellbibliotheken bereit:

- Tall Library: Für maximale Frequenz, jedoch mit hohem Leckstrom und niedriger Packungsdichte

- Mid-size Library: Optimiert für ein ausgewogenes Verhältnis zwischen Leistung und Energieverbrauch#

- Short Library: Für maximale Transistordichte bei geringem Energieverbrauch, typischerweise in CPUs und GPUs eingesetzt

Die Turbo Cells kommen bei den Short Libraries zum Einsatz. Durch die Verwendung sogenannter Doppelhöhe-Zellen (Double-Height) ermöglichen sie dort eine signifikante Leistungssteigerung, indem sie den Drive Current erhöhen – ohne die hohe Packungsdichte aufzugeben. Entwickler können das elektrische Verhalten feinjustieren, indem sie unterschiedliche Anordnungen, Breiten und Kombinationen der PMOS- und NMOS-Ribbons verwenden – je nach Bedarf an Leistung, Energieeffizienz und Fläche.

Diese Technologie erlaubt es, innerhalb eines Designs gezielt schnelle, weniger energieeffiziente Zellen mit effizienteren Varianten zu kombinieren. Das Ergebnis ist ein optimal ausbalanciertes Verhältnis zwischen Power, Performance und Area (PPA) – dem "heiligen Dreiklang" der Halbleitertechnik.

Intels Turbo Cells könnten sich somit als entscheidendes Werkzeug erweisen, um die Grenzen klassischer Designs zu überwinden und kritische, potenziell bremsende Pfade gezielt zu optimieren. Erste Produkte auf Basis dieser Technologien sind allerdings erst mit den ersten Chips zu erwarten, die in Intel 14A gefertigt werden. Laut Intels aktuellem Fahrplan wird dies frühestens im Jahr 2027 der Fall sein.