Werbung

Mit der Fertigung in Intel 18A wird Intel erstmals auf das Backside Power Delivery Network (BSPDN) namens PowerVia setzen, über dessen Vor- und Nachteile wir seit der Ankündigung bereits vielfach berichtet haben. Auf der Direct-Connect-Konferenz sprachen Intel und die EDA-Partner nun über konkrete Details zur Kosteneinsparung sowie zu Leistungsverbesserungen im Design.

Dass ein BSPDN nicht nur Vorteile mit sich bringt, wurde bereits mehrfach thematisiert. Intels Konkurrenten Samsung und TSMC agieren in dieser Hinsicht ebenfalls vorsichtiger – ihre Ansätze, etwa TSMCs Super Power Rail (SPR) und die Buried Power Rails (BPR), unterscheiden sich in Komplexität und Umsetzung von Intels PowerVia.

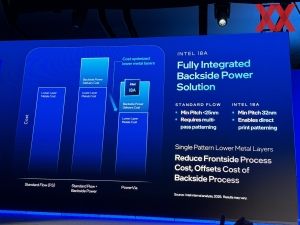

Die Einführung eines BSPDN anstelle einer reinen frontseitigen Stromversorgung führt zunächst zu höheren Kosten. Intel möchte dies jedoch durch die Vereinfachung des Frontside-Prozesses kompensieren.

Von Intel 7 über Intel 4 bis hin zu Intel 3 hat das Unternehmen offengelegt, wie viele Metalllagen im Frontside-Prozess erforderlich sind. Für ein Intel-3-Design sind es bis zu 18 Metalllagen mit einem minimalen Pitch von nur 30 nm. Bei solch kleinen Strukturen reicht in der EUV-Lithografie eine einfache Belichtung nicht mehr aus, was die Kosten für diese extrem dicht gepackten Lagen deutlich erhöht.

Bei Intel 18A mit PowerVia bleibt der minimale Pitch mit 32 nm zwar ähnlich klein, dennoch reduziert sich die Anzahl der notwendigen Fertigungsschritte. Die Vereinfachung des Frontside-Prozesses gleicht die höheren Kosten eines BSPDN somit nahezu aus. Dennoch wird eine Fertigung mit BSPDN am Ende stets teurer bleiben.

Cadence spricht über Details

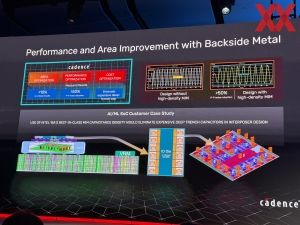

Die bislang eher grob umrissenen Angaben von Intel werden durch Cadence mit konkreten Zahlen ergänzt. Für die Integration von PowerVia sieht man dort ein Design mit fünf Metalllagen im Backside-Prozess vor. Im Gegenzug können im Frontside-Prozess zwei Metalllagen eingespart werden, die zudem einen größeren Pitch aufweisen. Auf den ersten Blick erscheinen fünf zusätzliche Backside-Lagen gegenüber zwei eingesparten Frontside-Lagen wenig attraktiv.

Doch hier zählen die Details: Im Frontside-Prozess kann nicht nur auf zwei Metalllagen verzichtet werden – auch die verbleibenden Lagen lassen sich einfacher routen, was insgesamt rund 15 % der Leitungsführung einspart. Diese Einsparung wirkt sich bis auf die Transistorebene aus, sodass Cadence von einer Reduzierung der Chipfläche um etwa 10 % ausgeht.

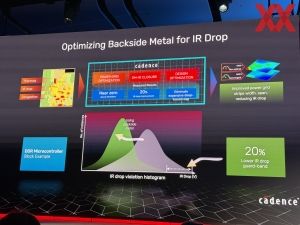

Die rückseitige Stromversorgung wird jedoch auch aus elektrischen Gründen eingeführt: Die Spannungseinbrüche (Vdroops) lassen sich um 20 % verringern. Das steigert einerseits die Chip-Leistung und reduziert andererseits die Notwendigkeit zusätzlicher Kondensatoren (MIMs).

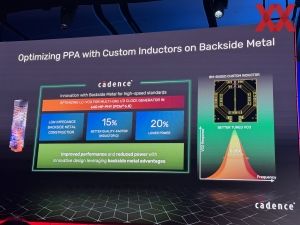

Im gesamten Chipdesign wirkt sich ein BSPDN besonders positiv auf IP-Blöcke aus, die für I/O-Anwendungen oder physikalische Schnittstellen (PHYs) vorgesehen sind. Eine um 20 % reduzierte Leistungsaufnahme und eine um 15 % verbesserte Signalqualität sollen mit PowerVia erreichbar sein.

Die Vorteile eines BSPDN lassen sich nur schwer isoliert betrachten – es wird kein Intel-Produkt geben, das zwar RibbonFETs in Intel 18A nutzt, aber nicht auf PowerVia setzt. Fertigungsgröße und der Einsatz von PowerVia gehen hier Hand in Hand. Intel hat jedoch eigene interne Studien durchgeführt und im Rahmen eines Intel-4-Prozesses separat untersucht, welche Vorteile PowerVia bietet. Die Ergebnisse decken sich weitgehend mit den Aussagen von Cadence.

Mit Panther Lake werden voraussichtlich noch in diesem Jahr die ersten Intel-Chips erscheinen, die auf Intel 18A mit PowerVia basieren.