Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

[Sammelthread] AMD K7 - Sockel A (462)

- Ersteller ItsFun

- Erstellt am

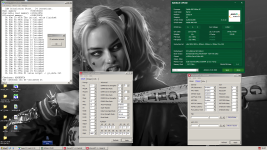

vielleicht sollten wir Tests in dem Sockel A thread weiter führen. Hier geht es unter. Dennoch ein 32M Screen.

So sei es. Ich versuche aktuell erstmal die gleiche Baseline herzustellen. Mit dem M2 Bios von dir friert mir das System bei 200x12 einfach in AIDA ein... Soll ich lieber das M3 oder das M4 Bios nehmen?

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Ja, das wäre der way to go. Mit dem M2 BIOS habe ich memtest Fehler gehabt. Den 12,5x200 Lauf habe ich mit dem M4 BIOS gemacht. Performance mode im BIOS aktiviert. Wobei ich noch nicht raus habe, ob und was der macht.So sei es. Ich versuche aktuell erstmal die gleiche Baseline herzustellen. Mit dem M2 Bios von dir friert mir das System bei 200x12 einfach in AIDA ein... Soll ich lieber das M3 oder das M4 Bios nehmen?

Mach sicherheitshalber auch einen clear CMOS.

edit.

Was gut ist, ASUS hat das System Modul im BIOS als letztes Modul eingebunden. Ein Mod mit dem Hex tool und dem acbrom geht schnell. Sprach-Modul ist Group2.

Irgendwas am M4 Bios ist jedenfalls komisch. Ich habe im Bios 2-3-3-6 eingestellt und erhalte nach Boot in Memset 4.1 2-3-2-5. Ist 2.5-4-3-9 eingestellt ergibt das 2.5-3-3-6. Da stimmt was mit der Benennung der Settings nicht würde ich sagen. Davon abgesehen friert mir das System bei 200x11 ein. Ich habe nun erstmal das 1009.002 beta Bios geflasht und mache damit einen 32M Lauf als Basis mit konservativen Settings. Einfach um generell einen Stabilitätstest zu haben.

Ram ist erstmal 1x512mb ETR. 512mb 6A mochte das Board nicht und anderen Ram der 2-2-2 bei wenig Spannung packt zu finden ist spannend... Du nutzt aktuell CE-6 oder DT-43?

EDIT:

32M 42m 44.357s

1009.002 Stock Bios

12.5x200

Alles im Bios auf Default

XP-m 2600+ 0451 XPMW 1.9V (ja, braucht es auf diesem Board! )

)

Ram 1x512mb ETR

2.5-3-3-5-2T

Meine Fresse ist das Board stock langsam...

Ram ist erstmal 1x512mb ETR. 512mb 6A mochte das Board nicht und anderen Ram der 2-2-2 bei wenig Spannung packt zu finden ist spannend... Du nutzt aktuell CE-6 oder DT-43?

EDIT:

32M 42m 44.357s

1009.002 Stock Bios

12.5x200

Alles im Bios auf Default

XP-m 2600+ 0451 XPMW 1.9V (ja, braucht es auf diesem Board!

)

)Ram 1x512mb ETR

2.5-3-3-5-2T

Meine Fresse ist das Board stock langsam...

Zuletzt bearbeitet:

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Clear CMOS? Ich habe testweise mal einen clear CMOS gemacht, es scheint zu funktionieren. Ob es an den SIPs liegt?Irgendwas am M4 Bios ist jedenfalls komisch. Ich habe im Bios 2-3-3-6 eingestellt und erhalte nach Boot in Memset 4.1 2-3-2-5. Ist 2.5-4-3-9 eingestellt ergibt das 2.5-3-3-6. Da stimmt was mit der Benennung der Settings nicht würde ich sagen. Davon abgesehen friert mir das System bei 200x11 ein. Ich habe nun erstmal das 1009.002 beta Bios geflasht und mache damit einen 32M Lauf als Basis mit konservativen Settings. Einfach um generell einen Stabilitätstest zu haben.

Bezüglich der RAM timings schau mal in die PCI register.

Bei mir passt es. Die tools lesen halt falsch aus.

Miss mal bei dir Vdimm. Soweit ich mich erinner, legt das board ungemoddet 2,8V auf den RAM an.Ram ist erstmal 1x512mb ETR. 512mb 6A mochte das Board nicht und anderen Ram der 2-2-2 bei wenig Spannung packt zu finden ist spannend... Du nutzt aktuell CE-6 oder DT-43?

Ich habe grade 1GB GSkill mit relabled Chips drauf. Vermutlich Nanya CS-5T Chips. Also eher in die Richtung CE-6 als Hynix

Naja kein Wunder bei den SIPs. Woran erinnern dich diese Tabellen:EDIT:

32M 42m 44.357s

1009.002 Stock Bios

12.5x200

Alles im Bios auf Default

XP-m 2600+ 0451 XPMW 1.9V (ja, braucht es auf diesem Board!)

Ram 1x512mb ETR

2.5-3-3-5-2T

Meine Fresse ist das Board stock langsam...

Die langsamsten beim NForce2 sehen ähnlich aus. Auch wenn das nicht umbedingt was bedeuten muss.

Jop, Memset 4.1 hat für Trp und Tras einen off-by-one Fehler. Vdimm ist bei mir etwa 2.8V, passt. Was die SIPs angeht müssen wir schauen. Ich glaube mein Board mag das was du im M2 und M4 Bios gebaut hast nicht. Ich habe keinen Vdd Mod drauf, sprich dort laufen noch die originalen 2.5V.Bei mir passt es. Die tools lesen halt falsch aus.

Erkenntnis am Rande: VIA hat den KT600 in 250nm gefertigt, Nvidia den NF2 in 150nm. Das erklärt dann auch die relativ hohe Differenz der Vdd - der modernere Prozess lässt weniger Spannung zu. Ob uns das umgekehrt beim FSB einholt wird sich zeigen.

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Ah okay. Kannst du mal verschiedene SIPs ausprobieren [bei 37D00h]? Ich habe meine Sammlung in die BIOSbude hoch geladen. Alternativ das original BIOS mit neuen SIPs?Jop, Memset 4.1 hat für Trp und Tras einen off-by-one Fehler. Vdimm ist bei mir etwa 2.8V, passt. Was die SIPs angeht müssen wir schauen. Ich glaube mein Board mag das was du im M2 und M4 Bios gebaut hast nicht. Ich habe keinen Vdd Mod drauf, sprich dort laufen noch die originalen 2.5V.

So wie ich das sehe, ist die Vdd Spannung an die RAM Spannung gekoppelt. Stelle ich 2,5V im BIOS ein, messe ich auch knappe 2,5V an einem möglichen Kerko Punkt am Chipsatz. Bei 2,85V dann die 2,8V am Messpunkt. Ich denke einfach mal den Vdimm mod abwarten und schauen was passiert.

Bis dahin könnte ich ausprobieren ob der Chipsatz skallieren kann mit der Spannung und mit SIPs. Dem VIA wird mit den schnelleren SIPs schnell die Puste ausgehen. Analog wie bei SIS auch.

Ah, das wusste ich nicht. Dann macht es sinn warum VIA da 2,5V anlegt. SIS ist afaik bei ca. 1,8v.Erkenntnis am Rande: VIA hat den KT600 in 250nm gefertigt, Nvidia den NF2 in 150nm. Das erklärt dann auch die relativ hohe Differenz der Vdd - der modernere Prozess lässt weniger Spannung zu. Ob uns das umgekehrt beim FSB einholt wird sich zeigen.

Hier nochmal die Optimierungen, die ich beim KT600 verwende

Code:

PCI register b0d0f0

offset 54 (CPU FSB Frequency select)

[2] PCI Master 8QW Operation

1 = enable

offset 55 (DRAM control)

[0] Write recovery time

DDR333 2T=0 / 3T=1

DDR400 3T=0 / 5T=1

[1] auto precharge for TLB read or CPU writeback

1= enable

[6] fast read-to-read-turn-around

1= enable

offset 66 (DRAM arbitration control)

[6] DRAM Access

2T=0 / 3T=1

offset 6B (DRAM arbitration control)

[5] Burst refresh

1= enable

offset 6C (DRAM drive control)

[0] DDR400 Twtr timing control

1T=0 / 2T=1

[5-4] SCMD/ MA early clock select (for 1T command)

00= latest

11= earliest

[7-6] CKE early clock select

00= latest

11= earliest

offset D4 (BIU control 1)

[0] fast write-to-read turnaround

1= enable

offset DF (BIU control 5)

[4] 166/200 performance improvement in host CPU master read ready logic

1= enable

[5] 166/200 performance improvement in master request logic

1= enable

[6] delay 1T for speculative read command

1= enable

[7] transparent MD to HD in synchronous mode for performance improvement

1= enableOffset 6C bietet Potenzial

---------

Ein Lauf mit Winbond BH5 und Chipsatz Optimierungen. Hier musste ich schon 2T schalten, da sonst instabil.

Vdimm 2,8V

Raiden Zero

Legende

Was meint ihr ist derzeit für das A7N8X das beste BIOS für Winbond/AT-6?

Wenn alles gut läuft werd ich übernächste Woche Trockeneis da haben und damit mal das Maximum ausloten. Muss zwar erstmal alle meine Riegel durchtesten, aber danach sollte definitiv was gehen. 300+ 1M waren auf NF4 ja recht easy drin.

Wenn alles gut läuft werd ich übernächste Woche Trockeneis da haben und damit mal das Maximum ausloten. Muss zwar erstmal alle meine Riegel durchtesten, aber danach sollte definitiv was gehen. 300+ 1M waren auf NF4 ja recht easy drin.

I think it is because Trp was moved to 60h and Trp and Trcd became 2-byte, not 1-byte like before (KT266-333). I've had this issue with KM400 and KM400A - wrong Trp and Tras was shown. Also I always recommend tweaking 6A=FF, gives a slight boost. But I think you should compare registers and SIPs with KT880 because it overclocks higher and maybe it's not only because of the die but settings too.Jop, Memset 4.1 hat für Trp und Tras einen off-by-one Fehler.

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Ich hätte gesagt, das ED55 BIOS mit dem DFI 12/18 preset zu probieren. Alternativ das 619XT BIOS ausprobieren. Das hängt immer davon ab was dein board mag und was nicht. Ich würde das vorher ausloten.Was meint ihr ist derzeit für das A7N8X das beste BIOS für Winbond/AT-6?

Wenn alles gut läuft werd ich übernächste Woche Trockeneis da haben und damit mal das Maximum ausloten. Muss zwar erstmal alle meine Riegel durchtesten, aber danach sollte definitiv was gehen. 300+ 1M waren auf NF4 ja recht easy drin.

Gegebenenfalls auch mit dem tweaker ausprobieren welche Werte passen.

Welche CPU wird gebencht?

I did try 6A=FF yesterday and got an intstant reboot.I think it is because Trp was moved to 60h and Trp and Trcd became 2-byte, not 1-byte like before (KT266-333). I've had this issue with KM400 and KM400A - wrong Trp and Tras was shown. Also I always recommend tweaking 6A=FF, gives a slight boost. But I think you should compare registers and SIPs with KT880 because it overclocks higher and maybe it's not only because of the die but settings too.

I will try other values. Maybe I can figure out what values do work.

I will try other values. Maybe I can figure out what values do work.As far as I remember, the KT880 chipset has different PCI register. So comparing will be difficult in my eyes. I couldn't find any datasheets fot the KT880 chipset.

Dies. ED oder ED55 und im Bios DFI 12/18 oder 12/31 oder 1/21 setzen. Ich meine 12/31 waren die schnellsten und 1/21 lief bei mir am besten. Zwischen den drei sind aber echt nur Nuancen.ED55 BIOS mit dem DFI 12/18 preset zu probieren. Alternativ das 619XT BIOS ausprobieren.

Versuch das direkt mit scharfen TRC und Trfc, sonst machst du dir mehr Arbeit als nötig. Ich habe Riegel die mit 13/15 gut laufen, mit 9/12 aber komplett versagen (<240Mhz). Das Board muss 9/12 aber auch mögen… infrared hat sogar ein Preset mit 7/12, das bekomme ich nicht stabil… alternativ geht auch 11/14.Muss zwar erstmal alle meine Riegel durchtesten,

Alphas kannst du etwas entschärfen auf 3-4-5-4-3-4-5 und wenn 32M klappt schrittweise anziehen. Ich hab dazu irgendwo ne Tabelle gemacht um das auszutesten.

VTT Mod kann auch helfen, je nach Riegel.

i assume this didn't work because there's some add setting on that byte. Also setting 0xFF should result in higher Trfc, especially for 1gbit dram (we don't use that anyways, as 1gbit means 1gbyte per rank with x8 chips).Also I always recommend tweaking 6A=FF, gives a slight boost.

So wie ich das sehe, ist die Vdd Spannung an die RAM Spannung gekoppelt.

Wenn ich das richtig sehe, dann sitzt der Vdd Mosfet für den Chipsatz (Q25) unterm Ende vom AGP Slot. Vdd ist im Bild gelb, Messpunkte gibt's also genug. Allerdings ist die Ansteuerung von Q25 echt fies gelöst. Das geht irgendwie über den LM324MX oben am ATX 20pin und durch diverse Widerstandsnetzwerke, die an GND, 3VSB und an einer Vref2.5 hängen. Das muss man als Schaltplan aufmalen um da durchzusteigen.

Jedenfalls wird die Vdd erstmal unabhängig von der VDimm über einen separaten Mosfet erzeugt. Eventuell gibt's im Feedback Loop einen Abgleich zur VDimm, das möchte ich nicht ausschließen.

Zuletzt bearbeitet:

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

6A nicht 60! Offset 6A sollte afaik tREF sein.i assume this didn't work because there's some add setting on that byte. Also setting 0xFF should result in higher Trfc, especially for 1gbit dram (we don't use that anyways, as 1gbit means 1gbyte per rank with x8 chips).

sehe ich auch so. Ich meine Vref2.5 ist der Feedback zu der RAM Spannung. Zumindest hängt da das irgendwie mit dran. Ich muss mir mal die Widerstände bzw. das Netzwerk mal aufzeichnen. Vielleicht kann ich mir dann die passenden Widerstände für ein Vdimm Rework raussuchen.Wenn ich das richtig sehe, dann sitzt der Vdd Mosfet für den Chipsatz (Q25) unterm Ende vom AGP Slot. Vdd ist im Bild gelb, Messpunkte gibt's also genug. Allerdings ist die Ansteuerung von Q25 echt fies gelöst. Das geht irgendwie über den LM324MX oben am ATX 20pin und durch diverse Widerstandsnetzwerke, die an GND, 3VSB und an einer Vref2.5 hängen. Das muss man als Schaltplan aufmalen um da durchzusteigen.

Jedenfalls wird die Vdd erstmal unabhängig von der VDimm über einen separaten Mosfet erzeugt. Eventuell gibt's im Feedback Loop einen Abgleich zur VDimm, das möchte ich nicht ausschließen.

Ich habe mir mal den VDimm Mod vorgenommen... Meine Herren ist das Board an der Stelle verzwickt aufgebaut. Soweit ich das verstanden habe, wirken die beiden NPN Transistoren als VDimm Senker. Also genau umgekehrt zu anderen Boards... Ich habe bei mir ein bisschen mit den Widerständen basteln müssen, weil ich weder 41.2kOhm noch 82.5kOhm im Bestand hatte. Resultat sind jetzt jedenfalls folgende Vdimm Stufen:

GPO0+1 - GPO1 - GPO0 - beide aus (Stock)

2.45V - 2.55V - 2.67V - 2.79V

Um also mehr als 2.8V raus zu bekommen, muss man den kompletten Feedback Loop anpassen. Zu allem Überfluss hat Asus natürlich keinen vollwertigen DC-DC Wandler verbaut, sondern realisiert die Nummer über einen LM324MX Komparator. Ja geil... Das Board ist an der Stelle echt verflucht... Zusätzlich setzt VIA auf ein aktives IC als Terminator für die Datenleitungen des Rams und das hängt (natürlich...) an der Chipsatzspannung UND der VDimm. Ja geil.

Um es noch komplizierter zu machen sind über diverse Widerstandsnetzwerke die 2.5V Vdd und die VDimm noch miteinander verschaltet.

GPO0+1 - GPO1 - GPO0 - beide aus (Stock)

2.45V - 2.55V - 2.67V - 2.79V

Um also mehr als 2.8V raus zu bekommen, muss man den kompletten Feedback Loop anpassen. Zu allem Überfluss hat Asus natürlich keinen vollwertigen DC-DC Wandler verbaut, sondern realisiert die Nummer über einen LM324MX Komparator. Ja geil... Das Board ist an der Stelle echt verflucht... Zusätzlich setzt VIA auf ein aktives IC als Terminator für die Datenleitungen des Rams und das hängt (natürlich...) an der Chipsatzspannung UND der VDimm. Ja geil.

Um es noch komplizierter zu machen sind über diverse Widerstandsnetzwerke die 2.5V Vdd und die VDimm noch miteinander verschaltet.

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Müsste nicht ein simpler Poti am Pin (Seite vom Feedback) vom LM324MX schon ausreichen um die Spannung zu ändern? Die Situation bei dem ASRock K7NF2 ist ähnlich. Auch da wird die Spannung über Komparatoren gesetzt. Einfach je nach Position den variablen Widerstand gegen GND oder höherer Spannung setzen und gut ist.

Ich neige grade faul zu sein und tendiere zu einem abschaltbaren Voltmod. Ansonsten müssten wir alle Widerstände neu dimensionieren, suchen und verlöten.

edit. Wobei ich nicht weiß was passiert wenn der Terminator der Datenleitungen ebenfalls höhere Spannungen bekommt.

Ich neige grade faul zu sein und tendiere zu einem abschaltbaren Voltmod. Ansonsten müssten wir alle Widerstände neu dimensionieren, suchen und verlöten.

edit. Wobei ich nicht weiß was passiert wenn der Terminator der Datenleitungen ebenfalls höhere Spannungen bekommt.

GPO0+1 - GPO1 - GPO0 - beide aus (Stock)

2.45V - 2.55V - 2.67V - 2.79V

Zuletzt bearbeitet:

Ja das sollte im Prinzip so klappen. Ich habe mich erstmal hingesetzt und anhand des Boardview vom A7V600 grob den VDimm Schaltplan nachgemalt. Nicht schön und ziemlich durcheinander, aber dennoch erhellend. Also:

1. Die Operationsverstärker ("OpAmps") in der Mitte (die acht Dreiecke) nehmen jeweils zwei Signale entgegen und geben die Differenz dieser hinten raus. Wenn man den Ausgang nun auf einen Eingang gibt, dann erhält man damit einen primitiven (aber wirkungsvollen) Regelkreis. Zumindest soweit ich die Dinger verstehe

2. Das Board stellt für den Ram eine Vdimm von ~2.5V bereit.

3. Das Board stellt für den Chipsatz eine Vdd von ~2.5V bereit.

4. Das Board generiert eine Referenzspannung 2.5Vref und füttert diese in die OpAmps rein. Daraus werden sowohl die Vdd als auch Vdimm generiert. Das führt dazu, dass bei Anpassen der Vdimm im Bios auch die Vdd mit verstellt wird Ja geil...

Ja geil...

5. Beim A7V600-X sind die Komponenten zur Vdimm Verstellung nicht bestückt (im Bild unten links die beiden NPN Transistoren und paar Widerstände). Das führt dazu, dass das Board immer 2.85V auf den Ram und den Chipsatz drückt. Die Verstellung ist außerdem so gebaut, dass die Vdimm und Vdd bei Aktivierung niedriger ausfällt. Default sind also 2.85V und dann geht es über 2.75V 2.65V bis 2.55V runter. Ja geil...

Ja geil...

6. Würden wir also entweder:

6a. die Verstellung manipulieren: fällt die Vdimm nur noch niedriger aus

6b. die Vref manipulieren: fällt die Vdd ebenfalls höher aus

7. Damit bleibt als einzige Möglichkeit die Vdimm zu beeinflussen, ohne das die Vdd leidet, nur direkt in den Regelkreis einzugreifen. In unserem Fall ist das im Bild unten rechts, genauer der OpAmp mit den Pins 8, 9 und 10. Pin 10 ist der Vref Eingang, Pin 9 die Regelschleife von der Vdimm zurück und Pin 8 der steuernde Ausgang zum VDimm Mosfet. Wenn man hier an Pin 9 einen Widerstand zu GND anlötet, sollte das die Vdimm anheben. Und zwar ohne, dass die 2.5Vref steigt. Es ergibt sich quasi ein Offset von Vdimm zu Vref und damit auch Vdd.

Ich habe testweise einen 50k VR benutzt. Bei etwa 20k ergibt sich bei einer Vref/Vdd von 2.8V eine Vdimm von 3V. Brauchbar natürlich kann man die Vdd über die Biosoption absenken und die Vdimm fällt dann auch.

natürlich kann man die Vdd über die Biosoption absenken und die Vdimm fällt dann auch.

Ich frage mich, ob es nicht leichter ist einfach den Vdimm Mosfet zu entfernen und dort anderweitig Spannung einzuspeisen.

1. Die Operationsverstärker ("OpAmps") in der Mitte (die acht Dreiecke) nehmen jeweils zwei Signale entgegen und geben die Differenz dieser hinten raus. Wenn man den Ausgang nun auf einen Eingang gibt, dann erhält man damit einen primitiven (aber wirkungsvollen) Regelkreis. Zumindest soweit ich die Dinger verstehe

2. Das Board stellt für den Ram eine Vdimm von ~2.5V bereit.

3. Das Board stellt für den Chipsatz eine Vdd von ~2.5V bereit.

4. Das Board generiert eine Referenzspannung 2.5Vref und füttert diese in die OpAmps rein. Daraus werden sowohl die Vdd als auch Vdimm generiert. Das führt dazu, dass bei Anpassen der Vdimm im Bios auch die Vdd mit verstellt wird

Ja geil...

Ja geil...5. Beim A7V600-X sind die Komponenten zur Vdimm Verstellung nicht bestückt (im Bild unten links die beiden NPN Transistoren und paar Widerstände). Das führt dazu, dass das Board immer 2.85V auf den Ram und den Chipsatz drückt. Die Verstellung ist außerdem so gebaut, dass die Vdimm und Vdd bei Aktivierung niedriger ausfällt. Default sind also 2.85V und dann geht es über 2.75V 2.65V bis 2.55V runter.

Ja geil...

Ja geil...6. Würden wir also entweder:

6a. die Verstellung manipulieren: fällt die Vdimm nur noch niedriger aus

6b. die Vref manipulieren: fällt die Vdd ebenfalls höher aus

7. Damit bleibt als einzige Möglichkeit die Vdimm zu beeinflussen, ohne das die Vdd leidet, nur direkt in den Regelkreis einzugreifen. In unserem Fall ist das im Bild unten rechts, genauer der OpAmp mit den Pins 8, 9 und 10. Pin 10 ist der Vref Eingang, Pin 9 die Regelschleife von der Vdimm zurück und Pin 8 der steuernde Ausgang zum VDimm Mosfet. Wenn man hier an Pin 9 einen Widerstand zu GND anlötet, sollte das die Vdimm anheben. Und zwar ohne, dass die 2.5Vref steigt. Es ergibt sich quasi ein Offset von Vdimm zu Vref und damit auch Vdd.

Ich habe testweise einen 50k VR benutzt. Bei etwa 20k ergibt sich bei einer Vref/Vdd von 2.8V eine Vdimm von 3V. Brauchbar

natürlich kann man die Vdd über die Biosoption absenken und die Vdimm fällt dann auch.

natürlich kann man die Vdd über die Biosoption absenken und die Vdimm fällt dann auch.Ich frage mich, ob es nicht leichter ist einfach den Vdimm Mosfet zu entfernen und dort anderweitig Spannung einzuspeisen.

Zuletzt bearbeitet:

digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

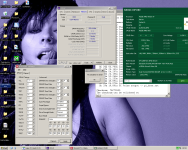

aktueller Wasserstand. Es geht langsam weiter.

Vdimm mod ist gesetzt. Höhere Spannungen wie 3,2V sind möglich. Die VTT Spannung wird vom board auch richtig gesetzt. Bis jetzt scheint es so, dass Spannungen ab 3V instabil werden. Ich denke, hier sollten wir noch nachforschen. Der Lauf hier ist bei Vdimm=2,97V und Vdd=2,8V gemacht worden. Beim modden musste ich den lm324a einmal ersetzen weil dieser dabei gestorben ist. Richtig viel Zuversicht gibt diese Schaltung nicht umbedingt. Vor allem wenn der PLL Chip ebenfalls mit der RAM Spannung versorgt wird. 🙈 Zum Glück kann man das ändern. Danke @Tzk

Ein wichtiger Punkt sind hier die Romsips. Genauso wie die Nforce2 Chipsätze haben auch die VIA Chipsätze verschiedene romsips. Ich habe bisher nur vier verschiedene gefunden. Egal ob KT600 oder KT880. Wahrscheinlich findet man die gleichen auch beim KT266A.

Jedenfalls bestimmen diese den maximalen Takt. Mehr noch als beim NForce2. Die schärfsten Romsips sind grade mal stabil bei ~160MHz, während die langsamsten bis 225MHz takten können [bei der Standardspannung].

Ein guter Kompromiss sind die 3. schnellsten womit ich auch diesen Lauf gemacht habe. Der Lauf ein paar Posts weiter oben ist mit den zweitschnellsten SIPs gemacht worden.

"217" SIPs / 2,97V Vdimm / 2,8V Vdd / keine Optimierungen; reiner Testlauf

Vdimm mod ist gesetzt. Höhere Spannungen wie 3,2V sind möglich. Die VTT Spannung wird vom board auch richtig gesetzt. Bis jetzt scheint es so, dass Spannungen ab 3V instabil werden. Ich denke, hier sollten wir noch nachforschen. Der Lauf hier ist bei Vdimm=2,97V und Vdd=2,8V gemacht worden. Beim modden musste ich den lm324a einmal ersetzen weil dieser dabei gestorben ist. Richtig viel Zuversicht gibt diese Schaltung nicht umbedingt. Vor allem wenn der PLL Chip ebenfalls mit der RAM Spannung versorgt wird. 🙈 Zum Glück kann man das ändern. Danke @Tzk

Ein wichtiger Punkt sind hier die Romsips. Genauso wie die Nforce2 Chipsätze haben auch die VIA Chipsätze verschiedene romsips. Ich habe bisher nur vier verschiedene gefunden. Egal ob KT600 oder KT880. Wahrscheinlich findet man die gleichen auch beim KT266A.

Jedenfalls bestimmen diese den maximalen Takt. Mehr noch als beim NForce2. Die schärfsten Romsips sind grade mal stabil bei ~160MHz, während die langsamsten bis 225MHz takten können [bei der Standardspannung].

Ein guter Kompromiss sind die 3. schnellsten womit ich auch diesen Lauf gemacht habe. Der Lauf ein paar Posts weiter oben ist mit den zweitschnellsten SIPs gemacht worden.

"217" SIPs / 2,97V Vdimm / 2,8V Vdd / keine Optimierungen; reiner Testlauf

230 2-2-2-5 schaut doch gut aus. Immerhin scheint der 512mb AT-6 halbwegs zu laufen. 1T scheitert vermutlich wieder am Chipsatz?

Wir können gerne 2.4ghz als Zieltakt nehmen, dann muss ich meine CPUs nicht so quälen. Das Ziel sollten damit vorerst 240x10 mit halbwegs guten Timings sein.

Solange man keine Mods bastelt ist es wegen Punkt 4 aus meinem Vorpost egal, weil VDD und Vdimm eh zusammen geregelt werden. Sobald man das aber trennt, drückt das Board die volle Vdimm in den ICS. Das kann ja nur schiefgehen, wenn an einem 2.5V Eingang 3V+ anliegen… setzt man eine Brücke um ist die Vdd die Quelle, was in meinen Augen deutlich sinnvoller ist.

Bild zum Mod muss ich nachliefern.

——

Und noch ein Gedanke: was passiert, wenn man genau zwischen dem beiden Fets Q10 (3V_Dual->Vdimm) und Q0302 (3.3V->3V_Dual) die Leiterbahn trennt und dort 5V einspeist? Auf dem Foto schaut es nicht so aus, als ob dort Durchkontaktierungen liegen oder weitere Leiterbahnen abgehen.

Den Mod halte ich aktuell noch nicht für nötig und würde ihn für später aufsparen…

EDIT2:

Mit dem 217er Bios, 512mb AT-7.5 und 2-2-2-6-2T (im Bios gesetzt) will mein System bei 220x10.5x nicht mehr booten. XP schmeißt einen BSOD. Mit 2.5-3-3-8-2T im Bios klappt es. 32M läuft auch nicht bei 230x10.5x. Vdd 2.82V, Vdimm 3.02V. Ich versuche mal einen kleineren Multi von 10...

Sonstiges im Bios:

-Turbo Modus ist aus

-Rank Interleave ist an

-Bank Interleave steht auf 4

-8QW steht auf Auto

Wir können gerne 2.4ghz als Zieltakt nehmen, dann muss ich meine CPUs nicht so quälen. Das Ziel sollten damit vorerst 240x10 mit halbwegs guten Timings sein.

Das sind so Design Entscheidungen die ich null verstehe. Asus hat in der Nähe des ICS94228 Taktgenerators zwei Brücken vorgesehen um eine zusätzliche Spannung zuzuführen - einmal als Quelle die Vdd vom Chipsatz und einmal die Vdimm.Vor allem wenn der PLL Chip ebenfalls mit der RAM Spannung versorgt wird. 🙈 Zum Glück kann man das ändern. Danke @Tzk

Solange man keine Mods bastelt ist es wegen Punkt 4 aus meinem Vorpost egal, weil VDD und Vdimm eh zusammen geregelt werden. Sobald man das aber trennt, drückt das Board die volle Vdimm in den ICS. Das kann ja nur schiefgehen, wenn an einem 2.5V Eingang 3V+ anliegen… setzt man eine Brücke um ist die Vdd die Quelle, was in meinen Augen deutlich sinnvoller ist.

Bild zum Mod muss ich nachliefern.

——

Und noch ein Gedanke: was passiert, wenn man genau zwischen dem beiden Fets Q10 (3V_Dual->Vdimm) und Q0302 (3.3V->3V_Dual) die Leiterbahn trennt und dort 5V einspeist? Auf dem Foto schaut es nicht so aus, als ob dort Durchkontaktierungen liegen oder weitere Leiterbahnen abgehen.

Den Mod halte ich aktuell noch nicht für nötig und würde ihn für später aufsparen…

EDIT2:

Mit dem 217er Bios, 512mb AT-7.5 und 2-2-2-6-2T (im Bios gesetzt) will mein System bei 220x10.5x nicht mehr booten. XP schmeißt einen BSOD. Mit 2.5-3-3-8-2T im Bios klappt es. 32M läuft auch nicht bei 230x10.5x. Vdd 2.82V, Vdimm 3.02V. Ich versuche mal einen kleineren Multi von 10...

Sonstiges im Bios:

-Turbo Modus ist aus

-Rank Interleave ist an

-Bank Interleave steht auf 4

-8QW steht auf Auto

Zuletzt bearbeitet:

Masterchief79

Legende

- Mitglied seit

- 08.04.2010

- Beiträge

- 5.063

Das Soltek SL-75KAV-X hat eine "Red Storm Overclocking Tech", die ich mal ausprobiert habe. Auto-OC auf Sockel A?

Er erhöht immer um 1MHz FSB und "checkt" dann irgendwas. Mit einem Tbred-B 2200 ist er von 1800 bis auf 1890MHz gekommen. Allerdings bricht er immer dort ab, egal was ich für Spannungen und Settings bei CPU und Ram einstelle, also ist vielleicht irgendein AGP/PCI-Gerät dann nicht mehr mit dem Takt einverstanden, der Chipsatz hat irgendwas oder die Utility kommt einfach an ihre Grenzen.

Er erhöht immer um 1MHz FSB und "checkt" dann irgendwas. Mit einem Tbred-B 2200 ist er von 1800 bis auf 1890MHz gekommen. Allerdings bricht er immer dort ab, egal was ich für Spannungen und Settings bei CPU und Ram einstelle, also ist vielleicht irgendein AGP/PCI-Gerät dann nicht mehr mit dem Takt einverstanden, der Chipsatz hat irgendwas oder die Utility kommt einfach an ihre Grenzen.

WMDK

Legende

Das Soltek SL-75KAV-X hat eine "Red Storm Overclocking Tech", die ich mal ausprobiert habe. Auto-OC auf Sockel A?

Gab es eigentlich jemals irgendeine Auto-OC Funktion, die auch nur ansatzweise brauchbar funktioniert hat? Egal welches "magische Tool" ich bisher aus Jux mal getestet habe, keines davon kommt auch nur im Ansatz in Bereiche, die mit manuellem OC innerhalb kürzester Zeit möglich sind.

oder die Utility kommt einfach an ihre Grenzen.

Plot Twist:

Am Ende zerlegt jemand das BIOS zur Analyse in seine Einzelteile und stellt fest, dass das Tool nur eine fest kodierte Funktion ist, die ein "Checking" simuliert und einfach am Ende stumpf den FSB auf 140MHz setzt und das als Ergebnis verkauft

Technik und Marketing haben sich vllt. einfach drauf geeinigt, dass man 5% pauschal geben kann

Technik und Marketing haben sich vllt. einfach drauf geeinigt, dass man 5% pauschal geben kann

Masterchief79

Legende

- Mitglied seit

- 08.04.2010

- Beiträge

- 5.063

Das wäre megaAm Ende zerlegt jemand das BIOS zur Analyse in seine Einzelteile und stellt fest, dass das Tool nur eine fest kodierte Funktion ist, die ein "Checking" simuliert und einfach am Ende stumpf den FSB auf 140MHz setzt und das als Ergebnis verkauftTechnik und Marketing haben sich vllt. einfach drauf geeinigt, dass man 5% pauschal geben kann

Falls jemand wirklich mal gucken will, ob man im BIOS was finden kann, es ist dieses Board mit BIOS Version Q11: https://theretroweb.com/motherboards/s/soltek-sl-75kav

Ansonsten teste ich gerade ein paar Bartons, die mir @keeel83 dankenswerterweise überlassen hat, auf meinem Epox 8KRAI (auch Via KT600). Hier die Ergebnisse:

Athlon 2500+ | AXDA2500KV4D | AQYFA 0350RPMW | 2290@1,65V | 2336@1,725V

Athlon 2500+ | AXDA2500KV4D | AQXEA 0321TPCW | 2244@1,65V | 2315@1,725V

Athlon 2600+ | AXDA2600KV4D | AQZFA 0348UPMW | 2190@1,65V auf KT600 | 2242 crash boot | 2242@1.725V boot | 2300 crash | 2305@1,775V BIOS

Athlon 2800+ | AXDA2800KV4D | AQXEA 0323MPM | 2350@1,65V | 2370 not exact in round 4M| 2425@1,725V | 2446 crash

Der 2800+ ist damit meine bisher beste Barton CPU, aus 8 oder 9 getesteten.

Mir ist auch aufgefallen, dass die sehr unterschiedlich warm werden. Der 2800+ liegt mit OC schon bei 47,5°C unter Last, ein 2500+ mit den gleichen Settings nur bei 38,5°C. Man merkt das auch direkt am Kühler, ist also kein Auslesefehler.

Ich mache auch mal einen 2,4GHz 32M Run auf dem Epox. Man kann da jede Menge Timings und Romsips direkt im BIOS verstellen, damit werde ich mal ein bisschen rumexperimentieren.

Zuletzt bearbeitet:

Das ist der Grund weshalb ich überlegt hatte einen Shunt in den 12V 4pin zu basteln oder irgendwie anders die Leistung zu messen. Ich glaube dass es auch bei Athlon XP CPUs mit verschieden hohen Leckströmen gibt. Mich interessiert ob sich ein Muster ergibt.Der 2800+ liegt mit OC schon bei 47,5°C unter Last, ein 2500+ mit den gleichen Settings nur bei 38,5°C. Man merkt das auch direkt am Kühler, ist also kein Auslesefehler.

WMDK

Legende

Ich glaube dass es auch bei Athlon XP CPUs mit verschieden hohen Leckströmen gibt.

Absolut. Das ist mir auch schon mehrfach aufgefallen.

Interessant wäre ob zum Beispiel einige CPUs vor eine Wand laufen, weil die Leckströme zu hoch werden oder ob Exemplare mit kleinen Leckströmen tendenziell auch höher Takten.

Ich bin nur zu geizig mir das Elmor PMD oder den TG Wireguard zu kaufen. Das muss günstiger gehen…

Ich bin nur zu geizig mir das Elmor PMD oder den TG Wireguard zu kaufen. Das muss günstiger gehen…

BlueFireXD

Enthusiast

- Mitglied seit

- 28.10.2020

- Beiträge

- 2.056

Nice, hast du auch mal Furmark CPU Stresstest getestet? Würde mich mal interessieren was da für temps und Stabilität nach 30 Minuten hast. Sie bei 2-3 CPUsDas wäre mega

Falls jemand wirklich mal gucken will, ob man im BIOS was finden kann, es ist dieses Board mit BIOS Version Q11: https://theretroweb.com/motherboards/s/soltek-sl-75kav

Ansonsten teste ich gerade ein paar Bartons, die mir @keeel83 dankenswerterweise überlassen hat, auf meinem Epox 8KRAI (auch Via KT600). Hier die Ergebnisse:

Athlon 2500+ | AXDA2500KV4D | AQYFA 0350RPMW | 2290@1,65V | 2336@1,725V

Athlon 2500+ | AXDA2500KV4D | AQXEA 0321TPCW | 2244@1,65V | 2315@1,725V

Athlon 2600+ | AXDA2600KV4D | AQZFA 0348UPMW | 2190@1,65V auf KT600 | 2242 crash boot | 2242@1.725V boot | 2300 crash | 2305@1,775V BIOS

Athlon 2800+ | AXDA2800KV4D | AQXEA 0323MPM | 2350@1,65V | 2370 not exact in round 4M| 2425@1,725V | 2446 crash

Der 2800+ ist damit meine bisher beste Barton CPU, aus 8 oder 9 getesteten.

Mir ist auch aufgefallen, dass die sehr unterschiedlich warm werden. Der 2800+ liegt mit OC schon bei 47,5°C unter Last, ein 2500+ mit den gleichen Settings nur bei 38,5°C. Man merkt das auch direkt am Kühler, ist also kein Auslesefehler.

Ich mache auch mal einen 2,4GHz 32M Run auf dem Epox. Man kann da jede Menge Timings und Romsips direkt im BIOS verstellen, damit werde ich mal ein bisschen rumexperimentieren.

Masterchief79

Legende

- Mitglied seit

- 08.04.2010

- Beiträge

- 5.063

Hab ich nicht, aber ich weiß dass du der Kernschmelze da ganz schön nahe gekommen bist, also kann ich das gerne mit meinem Setup mal gegentesten.

Hab sogar noch einen minimal besseren Barton gefunden. Wird wohl am späten Produktionsdatum liegen:

Athlon 3000+ | AXDA3000KV4D | AQYHA 0435SPMW | 2365@1,65V | 2442@1,725V

Lief mit 2450@1,725V noch durch SuperPi 1M, aber da hat der Ram auch schon 226MHz CL2-2-2-6, das kann bei 3V langsam eng werden. Ich teste morgen weiter, für heute ist Schluss.

Hab sogar noch einen minimal besseren Barton gefunden. Wird wohl am späten Produktionsdatum liegen:

Athlon 3000+ | AXDA3000KV4D | AQYHA 0435SPMW | 2365@1,65V | 2442@1,725V

Lief mit 2450@1,725V noch durch SuperPi 1M, aber da hat der Ram auch schon 226MHz CL2-2-2-6, das kann bei 3V langsam eng werden. Ich teste morgen weiter, für heute ist Schluss.

Zuletzt bearbeitet:

Liegt (auch) am Datum, aber das hier ist halt der Klassiker: solides Stepping AQYHA, Datum nach Jahreswechsel 03/04 und SPMW ist normalerweise auch ganz gut. Für einen 3000+ kann sich das echt sehen lassen. Wenn du weiterhin auf dem Epox unterwegs bist, kannst du evtl. versuchen den Multi im Betrieb zu ändern. Einfach mal CrystalCPUID greifen und testen. Ich bin mir gerade nicht sicher, ob du den 3000+ vorher zum Mobile modden musst.AQYHA 0435SPMW

WMDK

Legende

Interessant wäre ob zum Beispiel einige CPUs vor eine Wand laufen, weil die Leckströme zu hoch werden oder ob Exemplare mit kleinen Leckströmen tendenziell auch höher Takten.

Das hat Intel ja damals eigentlich schon beantwortet mit dem Prescott

Da war ja genau das eines der Probleme, nämlich dass die hohen Leckströme in den ersten Prescott-Versionen eben für sehr viel mehr Hitzeentwicklung gesorgt haben und gleichzeitig die eigentlich anvisierten Taktraten nicht erreicht werden konnten. Mit den späteren Steppings haben sie das ja verbessert und die Temperaturen gingen runter, der Takt etwas hoch, dennoch haben diese grundlegenden Problematiken verhindert, dass die Prescotts die ursprünglich anvisierten Taktraten jemals erreicht haben.

Da war ja genau das eines der Probleme, nämlich dass die hohen Leckströme in den ersten Prescott-Versionen eben für sehr viel mehr Hitzeentwicklung gesorgt haben und gleichzeitig die eigentlich anvisierten Taktraten nicht erreicht werden konnten. Mit den späteren Steppings haben sie das ja verbessert und die Temperaturen gingen runter, der Takt etwas hoch, dennoch haben diese grundlegenden Problematiken verhindert, dass die Prescotts die ursprünglich anvisierten Taktraten jemals erreicht haben.digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Die RomSIPs der VIA Chipsätze

Hallo zusammen, ich möchte meine gesammelten Informationen hier einmal ablegen, damit diese nicht verloren gehen.

Die VIA Chipsätze für Sockel A haben genauso ROMSIPs wie auch die NForce2 Chipsätze. Der Unterschied ist, dass sich damit kaum Jemand beschäftigt hat. Das möchte ich hiermit nachholen. Soweit ich es gesehen habe, hat VIA ab dem KT266er Chipsatz die ROMSIPs in das BIOS verlagert. Davor wurden diese immer durch die Southbridge [ja auch die mit dem enthaltenen Fehler] an die CPU gesendet worden. Ich habe mit ein paar BIOSe angesehen und bin bisher nur an vier verschiedene SIP Varianten gestoßen. Ich habe mir hierfür auch einfache abgekürzute Namen einfallen lassen. Hier in Übersicht von langsam zu schnell:

Auf dem ersten Blick ähneln diese Tabellen von denen von NVidia. Auch was man Leistungs-mäßig erwarten kann, passt es.

Aufgeschlüsselt, sind die einzelnen bits jedoch grundlegend anders. Mehr dazu weiter unten.

Eine Frage habe ich mir gestellt in wie weit die einzelnen Tabellen die maximale FSB Frequenz begrenzen und inwieweit der Chipsatz mit der Spannung skalliert. Das habe ich anschließend mit SuperPI 1M getestet und tabelarisch festgehalten:

SIP Werte im BIOS und PCI Register

Ein paar der SIP Werte lassen sich in den PCI registern finden. Ich habe für jeden einzelnen Multi die passenden S2K Werte aufgeschrieben.

Für das PCI register D1h habe ich keine Informationen gefunden.

Mit diesen Informationen habe ich einzelne Werte aus der SIP Tabelle getestet. Leider tauchen die meisten Werte nicht in den PCI registern auf oder diese werden nich beeinflusst. Darunter auch wichtige S2K Werte wie ReadToWrite- und WriteToRead Delay. Andere sind aber dann da und ändern dann an zwei Stellen die Bits. Ich denke hier tappe ich noch im Dunklen. Ich zeige dennoch meine vorläufigen Verknüpfungen

Übersichtlich die bits, die ich getestet habe:

Fazit

Die Frage ist jetzt in wie weit uns das weiter bringt. Meine Hoffnung war, dass man daduch die SIP Tabelle etwas anpassen kann und man bessere Übertaktung und bessere Leistung bekommen kann. Vergleicht man die ermittelten Werte mit den Nforce2 SIPs, sieht man als Beispiel, dass Nvidia für "WRDATA Delay" den Wert 3 statt 1 wie bei den VIA SIPs verwendet. Testweise habe den Wert 3 bei dem KT600 ausgetestet, doch das keinen Unterschied bei dem maximalen Takt bedeutet.

Andere Kombinationen führen schnell zu einem freeze oder non boot. Das Erarbeiten der funktionierenden SIPs wird hier deutlich schwerer sein als bei den Nvidia SIPs.

Am Ende haben wir immerhin eine Übersicht welche SIPs wir nutzen können und wie man das BIOS passend zuarbeiten kann um eine brauchbare Performance zu bekommen. Das ASUS A7V600-X, mit dem ich das alles getestet hatte, nutze nur die langsamsten SIPs ein Upgrade auf die "217" SIPs hat man schon einen kleinen Performance Boost ohne Einbußen bei der Übertaktung.

Ich mache noch ein paar Benchmarks, bevor ich mit diesem Projekt pausiere.

Hallo zusammen, ich möchte meine gesammelten Informationen hier einmal ablegen, damit diese nicht verloren gehen.

Die VIA Chipsätze für Sockel A haben genauso ROMSIPs wie auch die NForce2 Chipsätze. Der Unterschied ist, dass sich damit kaum Jemand beschäftigt hat. Das möchte ich hiermit nachholen. Soweit ich es gesehen habe, hat VIA ab dem KT266er Chipsatz die ROMSIPs in das BIOS verlagert. Davor wurden diese immer durch die Southbridge [ja auch die mit dem enthaltenen Fehler] an die CPU gesendet worden. Ich habe mit ein paar BIOSe angesehen und bin bisher nur an vier verschiedene SIP Varianten gestoßen. Ich habe mir hierfür auch einfache abgekürzute Namen einfallen lassen. Hier in Übersicht von langsam zu schnell:

Auf dem ersten Blick ähneln diese Tabellen von denen von NVidia. Auch was man Leistungs-mäßig erwarten kann, passt es.

Aufgeschlüsselt, sind die einzelnen bits jedoch grundlegend anders. Mehr dazu weiter unten.

Eine Frage habe ich mir gestellt in wie weit die einzelnen Tabellen die maximale FSB Frequenz begrenzen und inwieweit der Chipsatz mit der Spannung skalliert. Das habe ich anschließend mit SuperPI 1M getestet und tabelarisch festgehalten:

SIP Table | KT600 Chipset Voltage | max. FSB clock SuperPI 1M stable |

"D95" D930-2471-5F53-0209 | 2,5 V | 225 MHz |

"D95" D930-2471-5F53-0209 | 2,8 V | 240 MHz |

"217" 2131-2471-5B7B-0209 | 2,5 V | 225 MHz |

"217" 2131-2471-5B7B-0209 | 2,8 V | 240 MHz |

"21F" 2131-2471-5BFB 0209 | 2,5 V | 200 MHz |

"21F" 2131-2471-5BFB 0209 | 2,8 V | 208 MHz |

"69F" 6931-2471-57FB-0209 | 2,5 V | 160 MHz |

"69F" 6931-2471-57FB-0209 | 2,8 V | 170 MHz |

SIP Werte im BIOS und PCI Register

Ein paar der SIP Werte lassen sich in den PCI registern finden. Ich habe für jeden einzelnen Multi die passenden S2K Werte aufgeschrieben.

Für das PCI register D1h habe ich keine Informationen gefunden.

Code:

PCI register b0d0f0

[D0:7]=SYSDC (Probe)

[D0:6]=(same as bit7)

[D0:5]=SYSDCOUT Delay RW

[D0:4]=(same as bit5)

[D0:3]=SYSDCIN Delay RW

[D0:2]=(same as bit3)

[D0:1]=(same as bit3)

[D0:0]=(same as bit3)

[D2:6]=WrToRd Delay RW

[D2:5]=RdToWr Delay RW

[D2:4]=(same as bit5)

[D2:3]=(same as bit5)

[D2:2]=WRDATA Delay RW

[D2:1]=(same as bit3)

[D2:0]=(same as bit3)

[D3:7]=SYSDC (Probe)

[D3:6]=(same as bit7)

[D3:5]=SYSDCOUT Delay RW

[D3:4]=(same as bit5)

[D3:3]=SYSDCIN Delay RW

[D3:2]=(same as bit3)

[D3:1]=(same as bit3)

[D3:0]=(same as bit3)

[D7:7]=FID Value RO 00000=11.0 00001=11.5 00010=12.0

[D7:6]=00011=12.5 00100=5.0 00101=5.5 00110=6.0

[D7:5]=00111=6.5 01000=7.0 01001=7.5 01010=8.0

[D7:4]=01011=8.5 01100=9.0 01101=9.5 01110=10.0

[D7:3]=01111=10.5 10000=3.0 10001=3.5 100104.0 10011=4.5

Code:

====================================================================

| default "D95" BIOS 200MHz --> M3.0-M4.0=FSB133 |

====================================================================

multi | SOUT SIN W R WRD DC OUT IN | D0 D1 D2 D3 |

====================================================================

3.0 | 0011 1010 0101 0100 0 1 10 1 100 11 101 010 | 3A 54 6C EA |

4.0 | 0010 1001 0101 0101 0 1 10 1 011 11 101 010 | 29 55 6B EA |

5.0 | 0010 1000 1010 0011 0 1 10 1 010 11 101 010 | 28 A3 6A EA |

5.5 | 0010 1000 1010 0011 0 1 10 1 010 11 101 010 | 28 A3 6A EA |

6.0 | 0010 1000 1010 0011 0 1 10 1 010 11 101 010 | 28 A3 6A EA |

6.5 | 0010 1000 1010 0011 0 1 10 1 010 11 101 010 | 28 A3 6A EA |

7.0 | 0001 1000 1010 0011 0 1 10 1 010 11 101 010 | 18 A3 6A EA |

7.5 | 0001 1000 1010 0011 0 1 10 1 010 11 101 010 | 18 A3 6A EA |

8.0 | 0001 1000 1010 0011 0 1 10 1 010 11 101 010 | 18 A3 6A EA |

8.5 | 0001 1000 1010 0011 0 1 10 1 010 11 101 010 | 18 A3 6A EA |

9.0 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

9.5 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

10.0 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

10.5 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

11.0 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

11.5 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

12.0 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

12.5 | 0001 0111 1010 0011 0 1 10 1 001 11 101 010 | 17 A3 69 EA |

====================================================================

multi | D0 | D1 | D2 | D3 (BIU) | |

====================================================================

Code:

====================================================================

| faster "217" and "21F" romsips 200MHz --> M3.0-M4.0=FSB133 |

====================================================================

multi | SOUT SIN W R WRD DC OUT IN | D0 D1 D2 D3 |

====================================================================

3.0 | 0011 1000 1010 0101 0 1 10 1 011 11 101 010 | 38 A5 6B EA |

4.0 | 0010 1001 0110 0101 0 1 10 1 010 11 101 010 | 29 65 6A EA |

5.0 | 0010 0111 1111 0100 0 1 10 1 010 11 101 010 | 27 F4 6A EA |

5.5 | 0010 0111 1111 0100 0 1 10 1 010 11 101 010 | 27 F4 6A EA |

6.0 | 0010 0110 1111 0100 0 1 10 1 001 11 101 010 | 26 F4 69 EA |

6.5 | 0010 0110 1111 0100 0 1 10 1 001 11 101 010 | 26 F4 69 EA |

7.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

7.5 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

8.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

8.5 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

9.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

9.5 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

10.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

10.5 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

11.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

11.5 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

12.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

12.5 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

====================================================================

multi | D0 | D1 | D2 | D3 (BIU) | |

====================================================================

Code:

====================================================================

| fastest "69F" romsips 133MHz |

====================================================================

multi | SOUT SIN W R WRD DC OUT IN | D0 D1 D2 D3 |

====================================================================

3.0 | 0011 1000 1010 0101 0 1 10 1 011 11 101 010 | 38 A5 6B EA |

4.0 | 0010 1001 0110 0101 0 1 10 1 010 11 101 010 | 29 65 6A EA |

5.0 | 0010 0111 1111 0100 0 1 10 1 010 11 101 010 | 27 F4 6A EA |

5.5 | 0010 0111 1111 0100 0 1 10 1 010 11 101 010 | 27 F4 6A EA |

6.0 | 0010 0110 1111 0100 0 1 10 1 001 11 101 010 | 26 F4 69 EA |

6.5 | 0010 0110 1111 0100 0 1 10 1 001 11 101 010 | 26 F4 69 EA |

7.0 | 0001 0110 1111 0100 0 1 10 1 001 11 101 010 | 16 F4 69 EA |

7.5 | *crash @ 133MHz FSB* | -- -- -- -- |

8.0 | *crash @ 133MHz FSB* | -- -- -- -- |

8.5 | *crash @ 133MHz FSB* | -- -- -- -- |

9.0 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

9.5 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

10.0 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

10.5 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

11.0 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

11.5 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

12.0 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

12.5 | 0001 0101 1111 0101 0 1 10 1 001 11 101 010 | 15 F5 69 EA |

====================================================================

multi | D0 | D1 | D2 | D3 (BIU) | |

====================================================================Mit diesen Informationen habe ich einzelne Werte aus der SIP Tabelle getestet. Leider tauchen die meisten Werte nicht in den PCI registern auf oder diese werden nich beeinflusst. Darunter auch wichtige S2K Werte wie ReadToWrite- und WriteToRead Delay. Andere sind aber dann da und ändern dann an zwei Stellen die Bits. Ich denke hier tappe ich noch im Dunklen. Ich zeige dennoch meine vorläufigen Verknüpfungen

Übersichtlich die bits, die ich getestet habe:

Code:

2121 2059 5B7B 0209

------------------- ------------------- ------------------- -------------------

0010 0001 0010 0001 0010 0000 0101 1001 0101 1011 0111 1011 0000 0010 0000 1001

xoxx *ooo xx x * oooo x x x x oooo oox oo* * xx xx xx

*= freeze

x= no changes in PCI register

o= contained in PCI registerFazit

Die Frage ist jetzt in wie weit uns das weiter bringt. Meine Hoffnung war, dass man daduch die SIP Tabelle etwas anpassen kann und man bessere Übertaktung und bessere Leistung bekommen kann. Vergleicht man die ermittelten Werte mit den Nforce2 SIPs, sieht man als Beispiel, dass Nvidia für "WRDATA Delay" den Wert 3 statt 1 wie bei den VIA SIPs verwendet. Testweise habe den Wert 3 bei dem KT600 ausgetestet, doch das keinen Unterschied bei dem maximalen Takt bedeutet.

Andere Kombinationen führen schnell zu einem freeze oder non boot. Das Erarbeiten der funktionierenden SIPs wird hier deutlich schwerer sein als bei den Nvidia SIPs.

Am Ende haben wir immerhin eine Übersicht welche SIPs wir nutzen können und wie man das BIOS passend zuarbeiten kann um eine brauchbare Performance zu bekommen. Das ASUS A7V600-X, mit dem ich das alles getestet hatte, nutze nur die langsamsten SIPs ein Upgrade auf die "217" SIPs hat man schon einen kleinen Performance Boost ohne Einbußen bei der Übertaktung.

Ich mache noch ein paar Benchmarks, bevor ich mit diesem Projekt pausiere.

Das schaut doch super aus!

Ich habe ebenfalls das A7V600-X hier, mein Exemplar scheint aber deutlich schlechter zu laufen. Mit dem obigen 217 Sips komme ich bei 200Mhz durch 32M, bei 220 kann ich nicht booten, auch mit 2.75V Vdd nicht…

Der Via Chipsatz hat etliche Settings in den PCI Registern, umso spärlicher ist das BIOS. Dort gibt es noch S2K Drive strength, damit habe ich aber noch nicht experimentiert. Die aktuelle Wand bei unter 220Mhz macht allerdings wenig Lust auf mehr Ich werde es mit mehr Spannung versuchen und dann mal schauen.

Ich werde es mit mehr Spannung versuchen und dann mal schauen.

Ich habe ebenfalls das A7V600-X hier, mein Exemplar scheint aber deutlich schlechter zu laufen. Mit dem obigen 217 Sips komme ich bei 200Mhz durch 32M, bei 220 kann ich nicht booten, auch mit 2.75V Vdd nicht…

Der Via Chipsatz hat etliche Settings in den PCI Registern, umso spärlicher ist das BIOS. Dort gibt es noch S2K Drive strength, damit habe ich aber noch nicht experimentiert. Die aktuelle Wand bei unter 220Mhz macht allerdings wenig Lust auf mehr

Ich werde es mit mehr Spannung versuchen und dann mal schauen.

Ich werde es mit mehr Spannung versuchen und dann mal schauen.digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.513

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- ASRock B580 Steel Legend

- Display

- Acer B277UE

- SSD

- 2x500GB; 1x1000GB

- Soundkarte

- Xonar Essence / K340 / HD580

- Gehäuse

- Geometric Future King Arthur

- Netzteil

- BeQuiet! PurePower11 600W

- Keyboard

- Corsair K90

- Mouse

- Roccat Kova

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Danke!Das schaut doch super aus!

Ich finde es interessant, wie sehr sich die boards von der Leistung her auch bei dem VIA Chipsatz unterscheiden. Wäre interessant zu sehen, wie weit dieser Chipsatz generell skalliert. Bisher sieht es mit +0,3V schon sehr gut aus. Ich denke aufgrund des älteren Fertigungsverfahrens geht da noch einiges an Spannung. Sprich 3+VIch habe ebenfalls das A7V600-X hier, mein Exemplar scheint aber deutlich schlechter zu laufen. Mit dem obigen 217 Sips komme ich bei 200Mhz durch 32M, bei 220 kann ich nicht booten, auch mit 2.75V Vdd nicht…

Der Via Chipsatz hat etliche Settings in den PCI Registern, umso spärlicher ist das BIOS. Dort gibt es noch S2K Drive strength, damit habe ich aber noch nicht experimentiert. Die aktuelle Wand bei unter 220Mhz macht allerdings wenig Lust auf mehrIch werde es mit mehr Spannung versuchen und dann mal schauen.

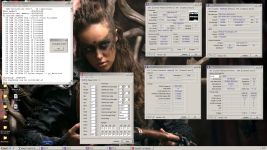

Ich habe noch ein paar Ergebnisse auf Lager. Mit einer FX5200 konnte ich bei 10x230 mehre loops pro Test fahren lassen. Das ging recht gut. Ich könnte mir vorstellen, dass man in dem Bereich auch Stabil bekommen kann. Mit einer 6600GT AGP ist das nicht ganz so einfach. Ich denke mal der Brückenchip hat kaum Lust auf den hohen AGP Takt.

Die Leistung reicht nicht um gegen den NF2 an zu stinken, dennoch ist das Ergebnis okay. War für eher ein Hynix ETR Test.

XP-M @10,5x230 | Hynix ETR @ 230MHz 2-3-2-6 @2,8v | 2,8V Vdd "217 SIPs"

Bei SuperPi bekomme ich 240MHz nicht durch 32M durch. Mit 1M geht es. 235Mhz geht dann mit 32M durch.

XP-M @10x240 | Hynix ETR @ 240MHz 2-3-3-7 @2,8v | 2,8V Vdd "217 SIPs"

XP-M @10x235 | Hynix ETR @ 235MHz 2-3-3-6 @2,8v | 2,8V Vdd "217 SIPs"