Werbung

In einem Architecture-Day gab Intel gestern erste Details zur kommenden Alder-Lake-Architektur und den Xe-Grafikkarten bekannt. Alder Lake ist der Codename für Intels zwölfte Generation der Core-Prozessoren und der erste Prozessor, der auf einer hybriden Architektur basiert. Zum Einsatz kommen Golden-Cove-Kerne für High-Performance-Anwendungen, auf der anderen Seite Gracemont-Kerne, die stromsparend agieren sollen.

Gerüchten zufolge werden die ersten Prozessoren mit dieser Architektur im Oktober des Jahres auf den Markt kommen und in Intels „Intel 7“-Prozess hergestellt, der einem 10nm-Enhanced-SuperFin-Prozess entspricht. Mit der hybriden Architektur verspricht sich Intel einen Effizienzvorteil, ähnlich wie man ihn schon bei ARM-Prozessoren mit ähnlichem Core-Setup gesehen hat.

Ein hybrides Design

Zur Seite stehen den Golden Cove- und Gracemont-Kernen aber auch eine Reihe weiterer Verbesserungen, die die Alder-Lake-Architektur zu einer 40 % besseren Performance gegenüber Skylake oder einer um 40 % niedrigeren Stromaufnahme bei gleicher Performance hieven sollen. Intel hat gegenüber der bisherigen Rocket-Lake-Mikroarchitektur an diversen Stellschrauben gedreht:

Das Front- und Back-End wurde überarbeitet, beispielsweise mit einem größeren Instruction Cache von 64 kb, einer verbesserten Branch Prediction mit vergrößerten History- und Structure-Sizes, verbesserten Out-of-Order-Dekoder mit insgesamt sechs Instruktionen pro Takt sowie einer massiv größeren paralleleren Verarbeitung innerhalb der Data Execution. Das Speichersubsystem wurde mit bis zu 4 MB Shared-L2-Cache für vier Kerne, einem tieferen Buffering, neuen Prefetchers und Dual Load+Store verbessert. Hinzu kommt ein neues Instruction-Set.

Im Blick behalten hat man beim Design neben der Performance aber auch die Leistungsaufnahme. Bereits auf Transistorebene wurde auf eine niedrigere Switching-Energie pro Instruktion geachtet, die mit einer niedrigeren Spannung für alle Frequenzen zu einem deutlich niedrigeren Stromverbrauch pro Transistor führen soll. Im Vergleich zum Skylake-Core spricht Intel von einer 40 % höheren Performance pro Thread oder einer um 40 % geringeren Stromaufnahme bei gleicher Performance. Im Multi-Thread-Bereich sollen sich eine um 80 % höhere Performance bei gleichem Stromverbrauch oder eine um 80 % verringerte Stromaufnahme bei gleichem Leistungslevel ergeben.

Modular für unterschiedliche Plattformen

Intels neuer Performance-Core ist breit aufgestellt – wider, deeper, smarter sind seine Rechenwerke, und mehr Daten soll er gleichzeitig verarbeiten können. Als Resultat gibt Intel bei SPEC CPU 2017 eine um 19 % höhere Performance gegenüber der elften Generation der Core-Prozessoren an – bei gleicher Taktfrequenz. Wie immer bei eigenen Benchmarks muss hier natürlich eine gewisse Vorsicht in der Interpretation herrschen, die Werte zeigen jedoch die gewünschte Effizienz des Kernes. Über den integrierten Support der Intel Advance Matrix Extensions (Intel AMX) sollen im Datacenter bei Tiled Matrix Multiplications eine achtfache Performance erreicht werden.

Der „Efficient Core“ genannte kleine Partner der Performance-Kerne wird über Intels Thread Director angesprochen, wenn es Sinn macht. Der Thread Director kann quasi in Realtime Empfehlungen an das Betriebssystem senden, welche Anwendungen auf den P-Cores und den E-Cores laufen sollen – beispielsweise Priority Tasks auf den stärkeren P-Cores und Hintergrund-Tasks auf den E-Cores.

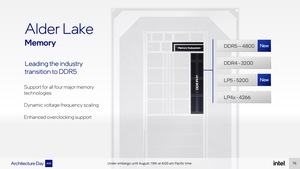

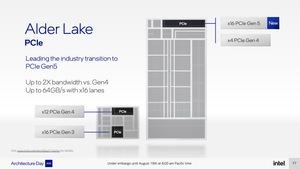

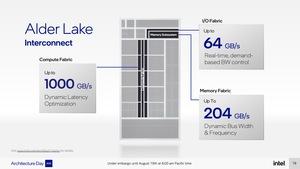

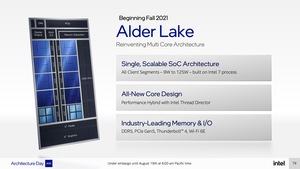

Aus diesen neuen Kernen setzt Intel dann Alder Lake zusammen – quasi eine System-on-a-Chip-Architektur, aus der man Prozessoren von 9 bis 125 W bauen möchte im neuen Intel 7 genannten Herstellungsprozess. Prozessoren auf der Alder-Lake-Architektur werden alle den Thread Director und die hybride Infrastruktur besitzen und außerdem auf moderne I/O-Techniken wie DDR5, PCIe Gen5, Thunderbolt 4 und WiFi 6E zurückgreifen können. Im Desktop-Bereich werden sie im Sockel LGA1700 umgesetzt. Einen neuen DMI-Link zur Anbindung des PCHs bringen sie ebenfalls mit.

Als Maximalausstattung gibt Intel an, 16 Cores erreichen zu wollen – acht Performance- und acht Effizienzkerne. Bis zu 24 Threads möchte man bieten, wobei die Performance-Kerne Hyperthreading unterstützen und die Efficient-Kerne nur einen Thread pro Kern abarbeiten können. Bis zu 30 MB Non-Inclusive-Low-Level-Cache unterstützen dann alle Cores zusammen im Maximalausbau.

In Zusammenarbeit mit DDR5-4800 als neuen Speicherstandard – oder alternativ immer noch DDR4-3200, PCIe Gen 5 und Gen 4, und einem optimierten Interconnect könnte uns ein spannender Herbst mit neuen Prozessoren bevorstehen!