Werbung

Synopsys verkündet ab dem dritten Quartal 2021 den DesignWare Controller und PHY IP, also die technische Basis für den Aufbau von PCI-Express 6.0 von Host bis Client, bereit zu haben. Die Spezifikationen von PCI-Express 6.0 wurden im vergangenen Jahr festgezurrt, neben Synopsys haben auch andere Hersteller in der Zwischenzeit Hardware zur Verifikation vorgestellt und ausgeliefert.

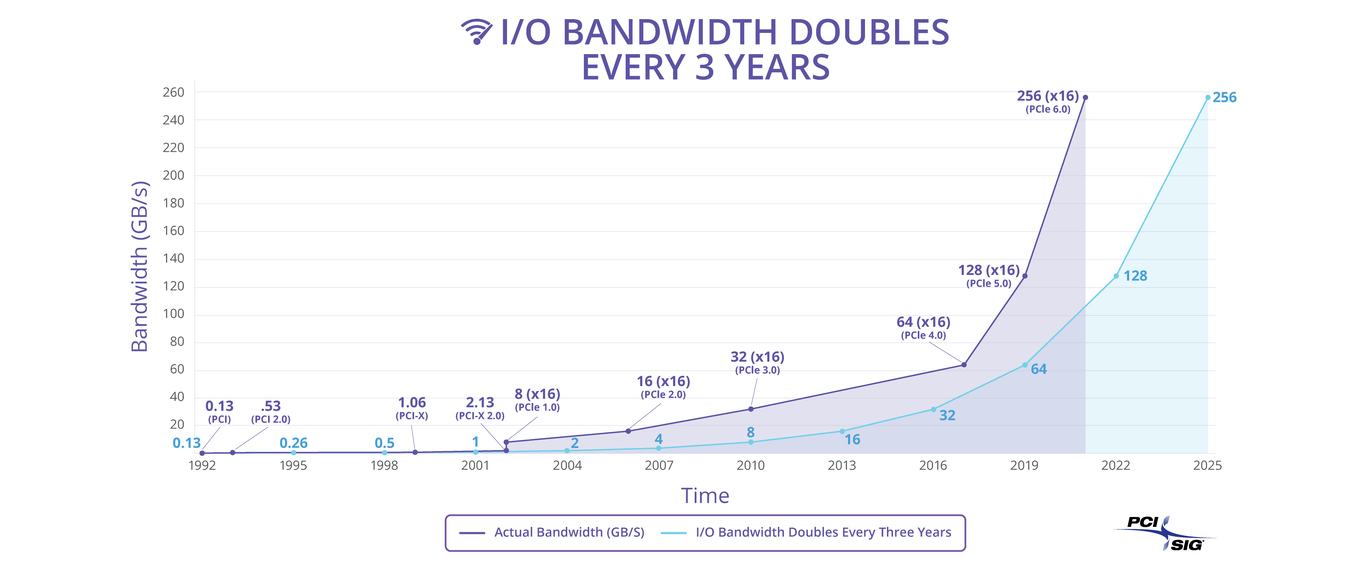

PCI-Express 6.0 wird Datenraten von 64 GT/s auf 16 Lanes ermöglichen. Dies entspricht einer weiteren Verdopplung und in etwa 128 GB/s in beide Richtungen (Overhead nicht beachtet). Das Fehlerkorrekturverfahren wird die Nettobandbreite etwas reduzierter ausfallen lassen. Erstmalig werden die Pulsamplitudenmodulation (PAM-4) und eine Fehlerkorrektur (RS-FEC) zum Einsatz kommen. Bei PCI-Express 3.0, 4.0 und 5.0 wird eine 128b/130b-Signalkodierung verwendet. Die Signalintegrität zu gewährleisten, wird zu einem immer wichtigeren Faktor in der Übertragung der Signale. Daher wird mit PCI-Express 6.0 wohl auch die Einführung eines Fehlerkorrekturverfahrens notwendig.

"PCI Express is the most widely-adopted and extensible interconnect technology in history," sagt Jim Pappas von Intel. "Synopsys' latest DesignWare IP for PCIe 6.0 is a leading indicator of the global ecosystems' ongoing commitment to this important industry standard and sets the stage for PCIe Gen 6 development and adoption on future Intel platforms."

Große Treiber im Bereich von PCI-Express sind vor allem die Datacenter Hardware und hier die Weiter- und Neuentwicklung schneller Interconnects wie CXL, die wiederum PCI-Express als Trägerstandard verwenden. In den kommenden zwei Jahren werden wir einen recht schnellen Wechsel von PCI-Express 5.0 und 6.0 sehen. Bereits Ende 2021 wird Intel sein Alder-Lake-Design vorstellen, welches PCI-Express 5.0 unterstützen wird. Sapphire Rapids als Serverdesign wird PCI-Express 5.0 ebenfalls verwenden.

Bei AMD dürfte die Einführung von PCI-Express 5.0 mit Zen 4 erfolgen - aktuell wird durch die Bank PCI-Express 4.0 unterstützt. Die erst kürzlich vorgestellte dritte EPYC-Generation alias Milan unterstützt ebenfalls noch PCI-Express 4.0 – genau wie Ice Lake-SP als nächste Xeon-Generation, die am 6. April offiziell vorgestellt werden wird. Intel wird mit Rocket Lake-S Ende März nachziehen.