Werbung

ARM hat erste Details zu seiner zukünftigen Server-IP veröffentlicht. Mit dem Neoverse-N1- und E1-Plattformen hat man in gewisser Weise den aktuellen Aufschwung bei den ARM-Serverdesigns neu aufleben lassen. Amazons Graviton2 setzt unter anderem auf ein angepasstes N1-Design und auch die zukünftigen Serverprozessoren von Nuvia verwenden eine ARM-Architektur.

Für das Neoverse-N1-Design peilte ARM eine Steigerung der in der Single-Threaded-Leistung von +60 % im Vergleich zu den Cortex-A72-Kernen an. Für die nächste Generation führt ARM eine neue V-Serie mit dem Codenamen (Zeus) ein, die auf maximale Leistung pro Kern ausgelegt ist. Im Vergleich zum N1-Design spricht ARM von einer abermals um 50 % höheren Single-Threaded-Leistung. Zudem gibt es ein Update von DDR4 auf DDR5, von PCI-Express 4.0 auf PCI-Express 5.0, von HBM2 auf HBM2E und den Interconnect-Standard CCIX 1.1 (zuvor 1.0). Neben den einzelnen Kernen wird also auch die komplette Infrastruktur der Plattform auf ein neues Level angehoben.

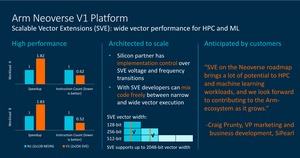

Mit dem V1-Design bzw. der zugrunde liegenden Architektur führt ARM zudem die Scalable Vector Extensions (SVE2) ein. Auf 2x 256 Bit weiten Vektoreinheiten können Berechnungen wie SIMD-Integer, Bfloat16 oder bestimmte Fließkommaberechnungen mit angepasster Software weitaus schneller ausgeführt werden. Im Grunde ein AVX von ARM.

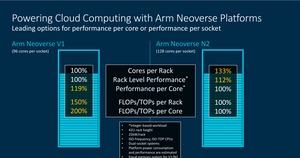

Die Zeus-Prozessoren werden in 7 und 5 nm gefertigt werden. Genaue Details dazu gibt man nicht bekannt. Die Anzahl der Kerne pro Sockel steigt von 64 auf 96. Ein SMT unterstützen die CPU-Kerne auf Basis des V1-Designs weiterhin nicht.

Im kommenden Jahr soll dann die N2-Plattform (Perseus) folgen. Die N2-Plattform ist der eigentliche Nachfolger der bereits bestehenden N1-Plattform und soll eine um 40 % höhere Single-Threaded-Leistung bieten. Hier zeigt sich dann auch der Unterschied zwischen dem V1- und N2-Design. Auch die N2-Plattform unterstützt die Scalable Vector Extensions, die Kerne besitzen allerdings nur 2x 128 Bit weite Vektoreinheiten. Das Datenformat Bfloat16 wird ebenfalls unterstützt.

Die N2-Plattform wechselt vollständig auf eine Fertigung in 5 nm. Zudem werden DDR5, HBM3, CCIX 2.0 und XCL 2.0 als Interconnect-Technologien erwähnt. Bis zu 128 Kerne sind auf Basis der N2-Plattform möglich. Eine Unterstützung von SMT ist nicht geplant.

In der Differenzierung zwischen dem V1- und N2-Design sieht ARM jeweils Vor- und Nachteile in den Plattform-Eigenschaften, so dass je nach Anwendungsbereich entschieden werden muss, welches nun das richtige Design ist. Geht es um maximal viel Rechenleistung im Rack, dann ist das N2-Design besser ausgerichtet. Geht es um eine möglichst hohe Leistung pro Kern, dann ist das V1-Design die bessere Wahl.

Für 2022 plant ARM mehrere Poseidon-Plattformen. Hier ist dann die Rede von einer Fertigung in 5 und/oder 3 nm, sowie der Unterstützung von PCI-Express 6.0 sowie den nächsten Generationen der Interconnect-Technologien.

Die ersten Prozessoren auf Basis der ARM-Designs werden in den kommenden Monaten erwartet. Der Rhea-HPC-Soc von SiPearl, der im Rahmen der European Processor Initiative (EPI) entwickelt wird, ist ein Kandidat für das V1-Design. Die heutige Ankündigung seitens ARM darf auch eine Art Vorschau verstanden werden. Anfang Oktober, auf der ARM-Entwicklerkonferenz, werden dann weitere Details erwartet.