Werbung

Erst Mitte Juni stellte Intel die Xeon-Prozessoren auf Basis von Cooper Lake vor. Aufgrund einiger Verzögerungen und Besonderheiten in der Mikro-Architektur sind diese nur für Serversysteme mit vier oder acht Sockel vorgesehen und werden wohl vor allem bei AI-Hyperscalern zum Einsatz kommen.

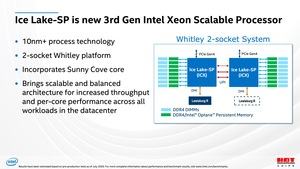

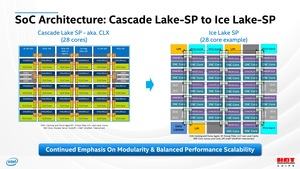

Auf der HotChips 32, die heute gestartet ist, hat Intel erste Details zu den Xeon-Prozessoren auf Basis von Ice Lake verraten. Diese werden das zweite Segment im Datacenter bedienen: Die kleineren Server mit einem oder zwei Sockeln. Dementsprechend werden die Ice-Lake-Xeons die Whitley-Plattform verwenden. Die Prozessoren auf Basis von Ice Lake-SP werden als 3. Generation der Xeon Scalable Prozessoren auf den Markt kommen – so wie auch schon die Cooper-Lake-Modelle.

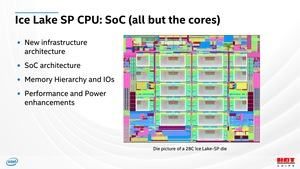

Bis zu 28 Sunny-Cove-Kerne wird Ice Lake-SP unterstützen. Das Octa-Channel-Speicherinterface wird DDR4 und Optane Persistent Memory unterstützen. Gefertigt werden die Prozessoren in 10nm+, also noch nicht in 10nm++ oder wie Intel es nennt: 10nm SuperFin Technology. Diese stellte man im Zusammenhang mit den Tiger-Lake-Prozessoren vor und will mit den umfangreichen Verbesserungen die Fertigung in 10 nm endlich in den Griff bekommen haben.

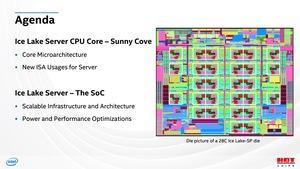

Intel konzentrierte sich zunächst aber auf den Sunny-Cove-Kern bzw. dessen Architektur, die für die Xeon-Prozessoren ebenfalls einige Änderungen erfahren hat. Grundsätzlich haben wir uns die Sunny-Cove-Architektur bereits angeschaut, legten damals aber den Fokus auf die mobilen Varianten.

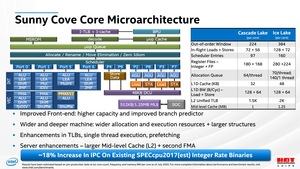

Es gibt also ein verbessertes Front-End und hier vor allem höhere Kapazitäten in den verschiedenen Registern und Buffern. Mit Sunny Cove wurde auch die Sprungvorhersage verbessert. Das Out-of-Order-Windows wurde von 224 auf 384 Einträge ausgeweitet. Load und Stores sowie Einträge im Scheduler können nun 128 + 72 bzw. 160 Einträge anstatt 72 + 56 bzw. 97 Einträge fassen. Der L1-Data-Cache wurde von 32 auf 48 kB ausgebohrt. Der L2-TLB (Translation Lookaside Buffer) wurde von 1.536 auf 2.048 Einträge ausgeweitet. Der Mid-Level-Cache wurden von 1 auf 1,25 MB vergrößert – auch das kennen wir schon.

Letztendlich will Intel die IPC-Leistung um 18 % erhöht haben. Dabei unterscheiden sich die Sunny-Cove-Kerne der Xeon-Prozessoren von den Kernen, wie wir sie von den mobilen Prozessoren kennen. Intel hat eine zusätzliche FMA-Einheit hinzugefügt (Fused Multiply Add). Sunny Cove für Server besitzt zwei FMA256- und eine FMA512-Einheit – Sunny Cove für den Desktop/Mobile nur zwei FMA256. Dies ist auch auf den Folien von der Computex im vergangenen Jahr zu erkennen. Hier zeigte Intel Sunny Cove in seiner Client-Ausführung. Die zusätzliche FMA512-Einheit für Sunny Cove in der Server-Ausführung ist unter anderem für die IPC-Leistungssteigerung verantwortlich.

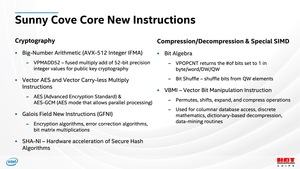

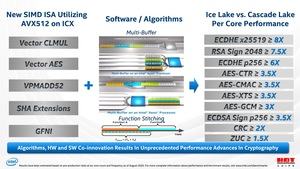

Um die Hardware effizienter Nutzen zu können, hat Intel einige neue Instruktionen entwickelt, die von den AVX512- oder Kryptographieeinheiten Gebrauch machen sollen. Diese sollen einen Beitrag dazu leisten, dass Ice Lake-SP um ein Vielfaches schneller ist, als die Vorgängerarchitekturen, die noch auf Skylake basieren.

Intel macht auf InfinityFabric

Intel hat einige Änderungen am Mesh-Interconnect vorgenommen, welcher die Kerne und SoC-Komponenten (Speichercontroller, PCI-Express-PHY, usw.) miteinander verbindet. Das Mesh der Skylake-Prozessoren besteht aus einer 2-dimensionalen Anordnung von Halbringen, die in vertikaler und horizontaler Richtung verlaufen und es ermöglichen, den kürzesten Weg zum richtigen Knoten zu nehmen.

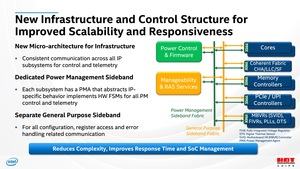

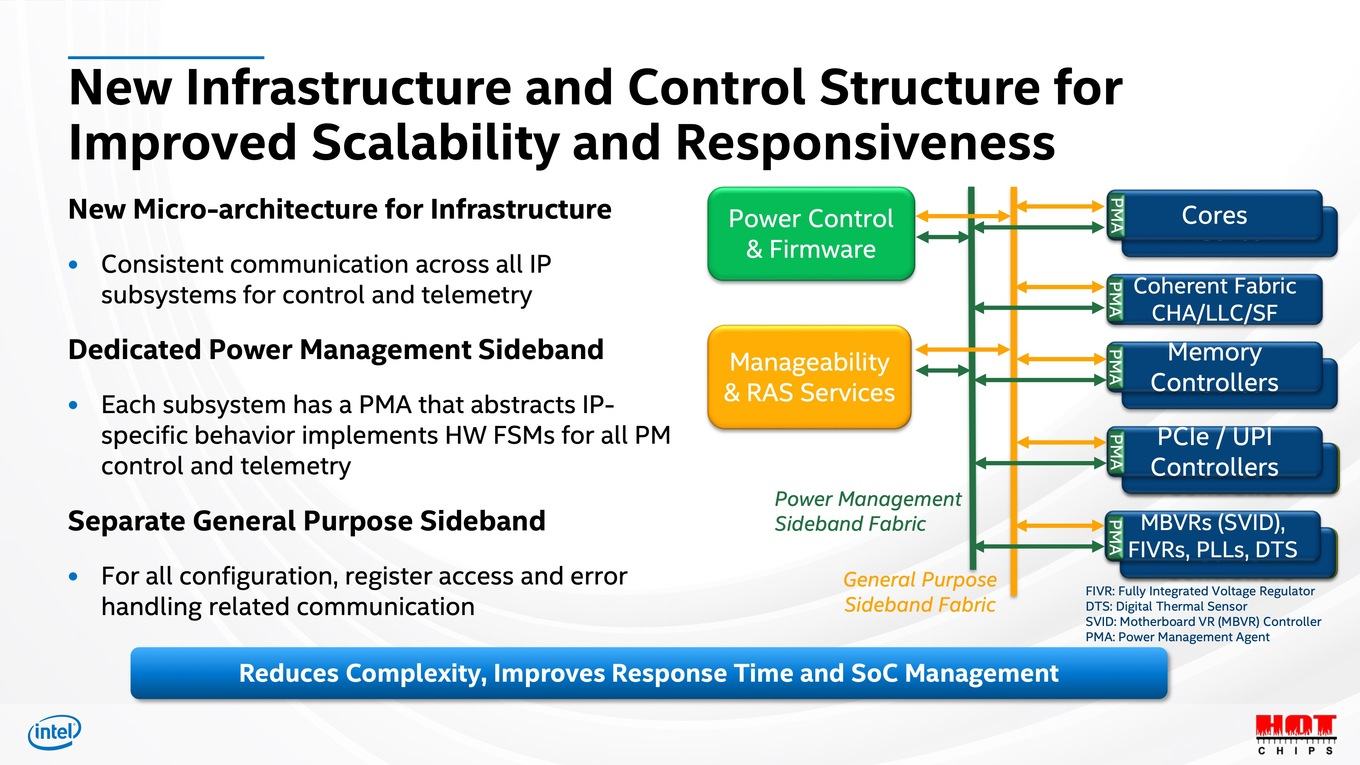

Für Ice Lake-SP gibt es nun ein Power Management Sideband Fabric und ein General Purpose Sideband Fabric. Dies erinnert stark an den Infinity Fabric bei AMD, der ebenfalls aus einem Data Fabric und einem Control Fabric besteht. Beide Sideband Fabrics verbinden aber noch immer die Kerne und Komponenten wie UPI, PCIe und DMI miteinander. Die Ringe des Mesh-Interconnects verlaufen auch bei Ice Lake-SP in horizontaler und vertikaler Richtung. Über die beiden Sideband Fabrics verspricht sich Intel eine bessere Kontrolle und Steuerung des Datenflusses sowie eine höhere Effizienz bzw. Leistung.

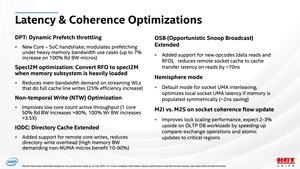

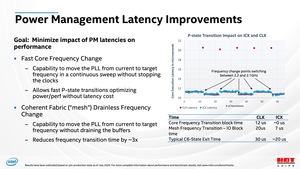

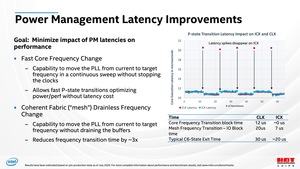

Die bessere Kontrolle über den Fabric soll unter anderem einen schnelleren Wechsel des Taktes ermöglichen. Anstatt 12 µs wie bei Cooper Lake sollen die Ice-Lake-SP-Prozessoren in weniger als 1 Mikrosekunde den Kerntakt ändern können. Für den Mesh reduziert Intel die Verzögerung von 20 auf 7 µs.

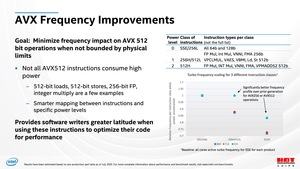

In die gleiche Kerbe schlägt eine neue Unterscheidung für die Nutzung von AVX512 und die damit verbundenen Taktraten. Zukünftig wird in Power Leveln unterschieden, welche Instruktionen hier für eine bestimmte Reduzierung im Takt angewendet werden. Sollen Skylake und Cooper Lake den Kerntakt im Bereich von 15 und fast 30 % reduziert haben, bleiben die Ice-Lake-SP-Prozessoren bei 100 bzw. fast 85 % des Normaltaktes.

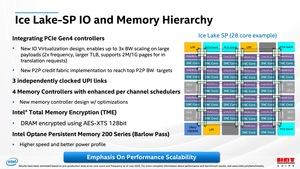

In der I/O- und Speicher-Hierarchie gibt es ebenfalls ein paar Änderungen. Anstatt zwei gibt es nun drei unabhängige UPI-Links. Es bleibt aber bei 3x UPI x20. Jeder der vier Speichercontroller kann zwei Speicherkanäle ansprechen. Für Skylake-SP verwendete Intel noch zwei Controller mit jeweils drei Kanälen. Das komplette Design der Speichercontroller wurde überarbeitet, sodass diese effizienter und schneller sein sollen. Die Aufteilung auf vier Speichercontroller soll die Zuteilung der Zugriffe vereinfachen. Zudem unterstützen sie Total Memory Encryption (TME) mittels AES-XTS 128Bit. Auch Optane Persistent Memory 200 Series (Barlow Pass) wird unterstützt.

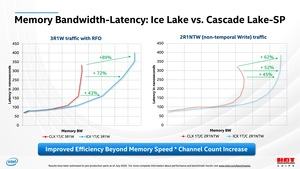

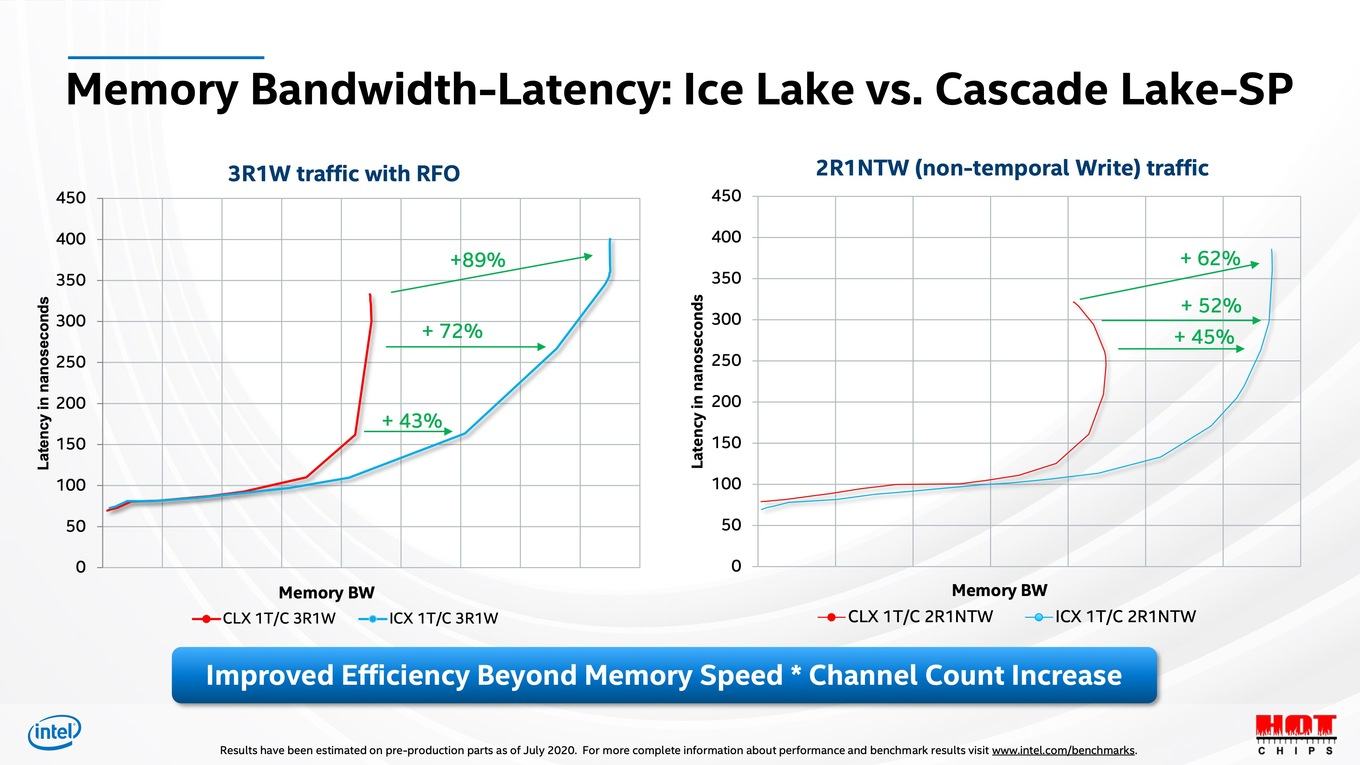

Die Verbesserungen im Speichercontroller sollen dazu beitragen, dass dessen Latenzen deutlich reduziert werden – auch ohne den Takt wesentlich anzuheben. Intel nennt noch keine Zahlen für die Speicherbandbreite. Will diese aber je nach Anwendung im Bereich von 45 bis fast 90 % erhöht haben. Diese Zahlen beziehen sich aber auch die Speicherbandbreite für einen Thread auf einem Kern und entsprechen nicht den Werten, die man auf einem kompletten Speicherinterface sehen wird.

Zumindest im Rahmen der HotChips-Konferenz verrät Intel noch keine weiteren Details zu Ice Lake-SP. Unklar ist unter anderem, ob die hier gezeigten 28 Kerne das Maximum dessen darstellen, was man als Extreme Core Count in 10 nm fertigen lässt. Die Xeon-Prozessoren auf Basis von Ice Lake-SP werden gegen Ende des Jahres erscheinen.

Da die Präsentation auf der HotChips-Konferenz aktuell stattfindet, werden wir diesen Beitrag um zusätzliche Informationen ergänzen.