Werbung

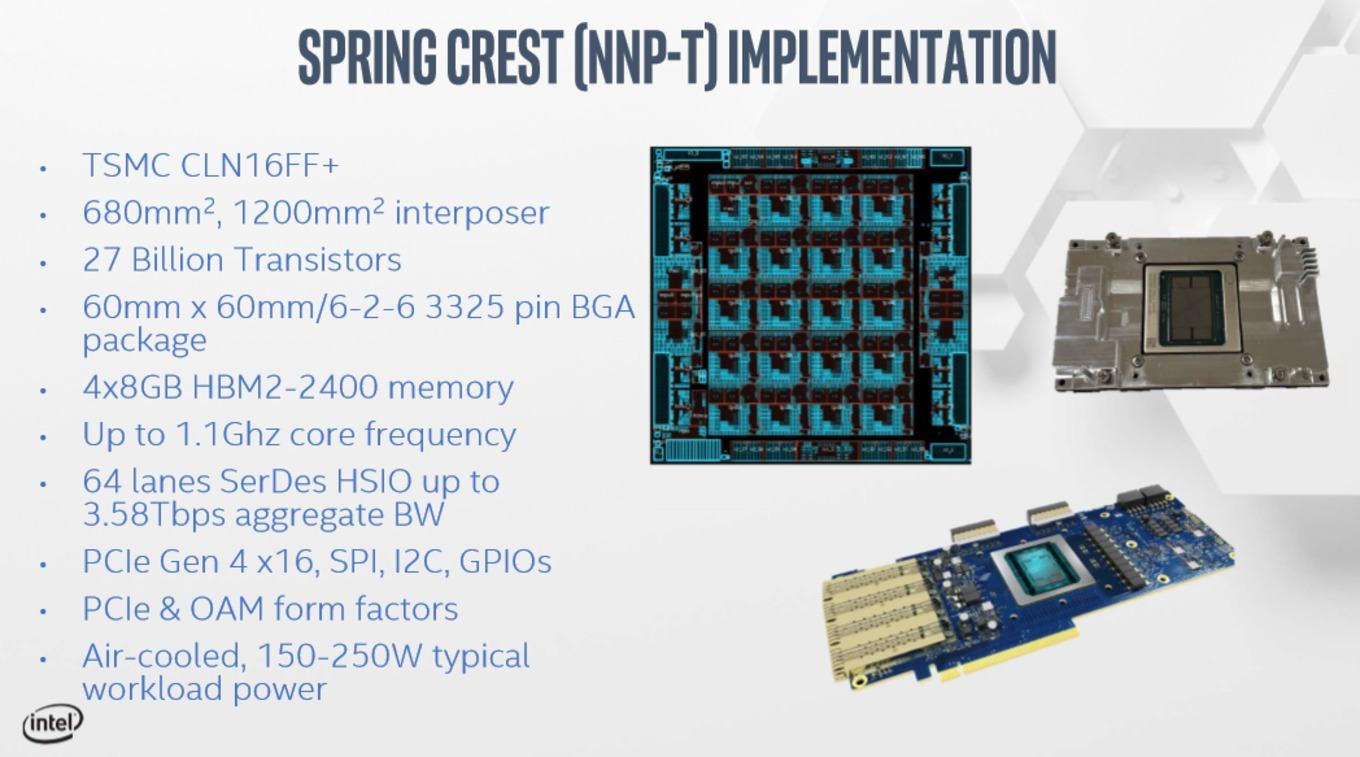

Intel hat weitere Details zum Nervana Neural Network Processor for Training (NNP-T) veröffentlicht, die Tomshardware aufbereitet hat. Aus den Informationen gehen bisher unbekannte technische Details hervor. So verwendet der NNP-T 27 Milliarden Transistoren sowie 32 GB HBM2-Speicher und packt dies alles auf einen Interposer mit einer Fläche von 1.200 mm².

Der NNP-T ist das Gegenstück zum NNP-I – letztgenannter ist für das Inferencing vorgesehen, während der NNP-T das Training von Deep-Learning-Netzwerken übernimmt. Der NNP-I verwendet unter anderem Sunny-Cove-Kerne und AVX512 zur Beschleunigung der Berechnungen.

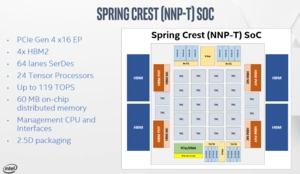

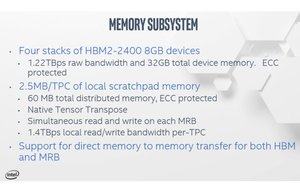

Doch nun zum Aufbau des NNP-T. Dieser besteht aus 24 Tensor Processoren (TPCs). Diese kommen auf eine Rechenleistung von 119 TOPS. Auf dem SoC befinden sich zudem 60 MB an on-chip Speicher (SRAM). Um möglichst viele Daten möglichst nahe an den TPCs zu haben, verbaut Intel vier HBM2-Speicherchips mit einer Kapazität von jeweils 8 GB – zusammen also 32 GB. Zusammen mit einem PCIe-4.0-Interface mit 16 Lanes sowie 64 SerDes (Serialisierer/Deserialisierer) und weiteren Kompomenten sitzen der SoC und die vier HBM2-Speicherchips auf einem Interposer mit einer Fläche von 1.200 mm².

Gefertigt wird der NNP-T von TSMC im 16-nm-Prozess (CLN16FF+). Erst kürzlich zeigte TSMC einen Chip mit zwei großen Dies und mehreren HBM2-Speicherchips, dessen Interposer es auf 2.500 mm² bringt. Beim NNP-T kommt auch die Chip-on-Wafer-on-Substrate (CoWoS) Packaging-Technologie zum Einsatz. Es liest sich immer etwas seltsam, wenn Intel bei der Vorstellung eines Prozessors von der Fertigung bei TSMC spricht.

Verpackt ist der NNP-T in einem 60 x 60 mm großen Package, welches ein BGA-Interface mit 3.325 Pins besitzt. Der NNP-T wird aber nicht in einem Sockel, sondern fest verlötet verwendet. Der NNP-T arbeitet mit einem Takt von 1,1 GHz und kann mit einer TDP von 150 bis 250 W konfiguriert werden.

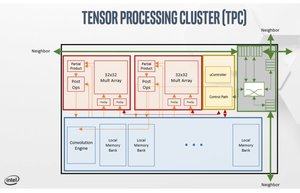

Die einzelnen TPCs sind vor allem darauf ausgelegt, schnell mit Daten gefüttert zu werden. Jeder der TPCs verfügt über vier schnelle Anbindungen an den Interconnect, von denen zwei für die Anbindung an den HBM2 und zwei weitere für die Anbindung an den 2D-Mesh-Interconnect gedacht sind. Die TCPs selbst können Daten in Form von bFloat16 Matrix-Multiplikationen, FP32 und FP16 verarbeiten.

Ein einzelner NNP-T wird aber in den seltensten Fällen zum Einsatz kommen und so plant Intel das Design für größere Server, die aus 1.024 Nodes bestehen. Jeder dieser Knoten besitzt dann acht NNP-T-Beschleuniger. Getestet hat Intel dies aber nur bis 256 Beschleuniger bzw. bis zu dieser Größe ist die Software bisher in der Lage zu skalieren. Alle weiteren Ausbaustufen müssen in den kommenden Monaten erarbeitet werden.

Laut Intel befindet sich der NNP-T derzeit in der Sampling-Phase und soll noch in diesem Jahr an enge Partner ausgeliefert werden. 2020 soll dann eine breitere Verfügbarkeit sichergestellt werden. Derzeit verwendet Intel ein B-Stepping des Chips, welches auch das finale Design sein soll.