Werbung

Zukünftige CPUs und GPUs werden wohl den Weg eines Multi-Chip-Ansatzes gehen. Ganz ähnlich wie AMD dies bei den Ryzen-Prozessoren bereits heute tut, werden solche Designs auf vielen kleineren Modulen aufgebaut sein, die entsprechend des Einsatzzweckes des jeweiligen Produktes skaliert werden können. Dementsprechend arbeiten auch viele CPU- und GPU-Hersteller an einer technischen Umsetzung dieses Ansatzes.

AMD verwendet für seine GPUs mit HBM einen Interposer, der jedoch recht kompliziert zu fertigen und dementsprechend recht teuer ist. Intel setzt auf eine Technologie namens Embedded Multi-die Interconnect Bridge oder kurz (EMIB) und anstatt Through-Silicon Vias (TSVs) können auch induktive Verfahren wie ThruChip Interface (TCI) zum Einsatz kommen.

Beim Auftragsfertiger TSMC arbeitet man derzeit verstärkt in Richtung einer Fertigung in 7 nm, denkt aber natürlich auch schon über die nächsten Schritte nach. Für zukünftige Produkte, die aus mehreren Chips bestehen, will TSMC eine weitere Technologie anbieten und arbeitet in diesem Bereich mit dem Unternehmen Cadence zusammen. Diese hört auf den Namen Wafer-on-Wafer oder kurz WoW. Nach Chip-on-Wafer-on-Substrate (CoWoS) und Integrated-Fan-Out (InFO) handelt es sich bei WoW um die dritte Iteration einer 3D-Technologie.

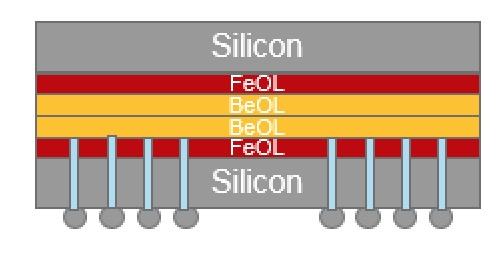

Für Wafer-on-Wafer kommen zwei Wafer zum Einsatz, von denen eine kopfüber über die zweite geführt wird. Die Pads, also Kontakte der Wafer, müssen überdeckend gefertigt werden, damit ein der Kontakt auch hergestellt werden kann. Wie TSMC die beiden Bonding Layer (BEOL und FEOL) zusammenführt ist das Geheimnis des zugrundeliegenden Prinzips. Muss der obere der beiden Chips IO-Signale ausgeben können, werden diese durch TSVs aus dem Package herausgeführt.

Das WoW-Verfahren hat aber auch einige Hürden, die vor allem eine möglichst hohe Ausbeute guter Chips voraussetzt. Die zusammengelegten Wafer werden erst nach diesem Vorgang geschnitten. Auf einem Belichteten Wafer können noch keine Tests der Chips stattfinden. Es könnte also passieren, dass ein funktionierender und ein nicht funktionierender Chip zusammenkommen. Das Gesamtkonstrukt ist dann aber noch immer nicht mehr funktionstüchtig. Eine hohe Ausbeute der Wafer ist für das WoW-Verfahren also eine Grundvoraussetzung.

Laut TSMC lassen sich WoW und andere Verfahren auch kombinieren. So kann ein WoW-Package mit einem weiteren mittels Interposer zusammengebracht werden. Außerdem ermöglicht das WoW-Verfahren auch mehr als zwei Wafer übereinander – sofern alle bis auf den untersten auch TSVs anbieten.

TSMC plant den Einsatz von Wafer-on-Wafer für Chips, die in 7 oder 5 nm gefertigt werden sollen. Konkrete Ankündigungen gibt es noch nicht. Das Verfahren eignet sich besonders für große Chips und wird daher für HPC-Prozessoren zum Einsatz kommen. Cadence fertigt IC-Design-Werkzeuge und stellt entsprechende Techniken zur Verfügung. In der Pressemitteilung werden diese wie folgt beschrieben:

- Innovus Implementation System: Supports single database top-die including front/back-side routing and backside-through-silicon-via (BTSV) support, creating connections between multiple dice

- Quantus Extraction Solution: Supports back-side routing layers, sub-circuit replacement for BTSV and die-to-die interface coupling capacitance extraction, enabling electrical analysis between the dice

- Voltus IC Power Integrity Solution: Provides die-level power map generation, enabling concurrent power analysis of multiple dice

- Tempus Timing Signoff Solution: Provides multi-die static timing analysis (STA) support, enabling a checking of timing paths that cross multiple dice

- Physical Verification System (PVS): Offers design rule checking (DRC) and layout vs. schematic (LVS) for die with BTSV, interface alignment and connectivity checks, ensuring that the two dice connect properly

- Virtuoso Platform: Includes features for bump placement and alignment on top of the existing PDK via the Virtuoso Incremental Technology Database (ITDB), creating connections between multiple dice

- OrbitIO interconnect designer: Provides interface connectivity, device flattening, port connectivity and configurable module definitions to manage top-level connectivity, enabling unified planning of die interconnect and alignment

- Sigrity PowerSI 3D-EM Extraction Option: Offers electrical modeling of the combined die and interposer, validating that the power and ground distribution is sufficient for multiple dice

- Sigrity PowerDC technology: Thermal analysis solution with interposer and die analysis capabilities that allow co-simulation with Voltus IC Power Integrity Solution, enabling inclusion of temperature into concurrent electromigration analysis of multiple dice

- Sigrity XcitePI Extraction: Provides accurate interposer-level interconnect model extraction, enabling validation of high-speed signal propagation in the time and frequency domains

- Sigrity SystemSI technology: Automatic construction of complete model-based interconnect topologies used to drive simultaneous switching noise (SSN/SSO) analysis for concise eye-diagram validation