Werbung

Für die Steigerung der Rechenleistung moderner Prozessoren sind möglichst viele Datenverbindungen essentiell – gleiches gilt für die Anbindung von schnellem Speicher. Im Falle von High Bandwidth Memory verwenden die meisten Hersteller sogenannte Through-Silicon Vias (TSVs). Bei den TSVs handelt es sich um eine Halbleitertechnik, die durch das Silizium-Substrat geführt wird.

Neben der enorm komplizierten Fertigung dieser TSVs bestehen die Herausforderungen in der finalen Prüfung dieser Verbindungen. Da keine externe Verbindung hergestellt werden kann, gibt es indirekte Verfahren im BEOL-Prozesse, vor dem Anbringen der Bumps und dem Zerteilen des Wafers.

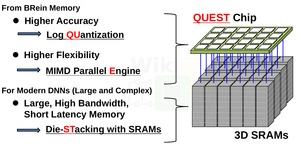

Die Komplexität der TSVs ist eine der größten Herausforderungen bei der Fertigung gestapelter Chips. Teams der Universitäten Hokkaido und Keio haben bereits vor einigen Jahren eine Technik namens ThruChip Interface (TCI) entwickelt und nun einen ersten Prototypen-Chip vorgestellt, der diese Technik verwendet. Bei TCI handelt es sich um eine Nahfeldkommunikation im induktiven Verfahren – also in gewisser Weise eine drahtlose Technologie. Für solche Datenverbindungen hat Intel ein eigenes Verfahren namens EMIB entwickelt, welches unter anderem bei den Core-Prozessoren mit Radeon RX Vega M Grafik zum Einsatz kommt.

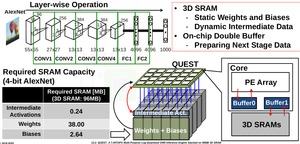

Auf der International State Circuits Conference (ISSCC) zeigte das Forscherteam den QUEST, einen Inferencing-Chip, der gestapelten SRAM mittels TCI verbindet.

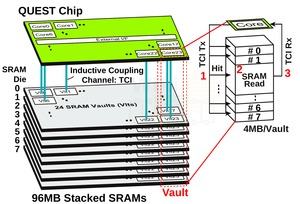

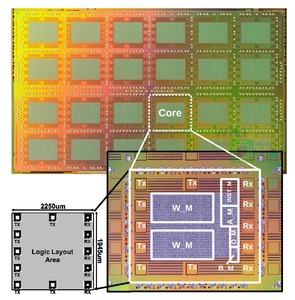

Der QUEST besteht aus neun Dies. Acht davon sind SRAM-Dies und eine weitere die Logic-Die. Ähnlich ist auch HBM mit acht Layern aufgebaut. Hergestellt wird der Chip bei TSMC im CMOS-40-nm Low-Power-Verfahren. Die Die-Größe beträgt 121,55 mm². Aus thermischen Gründen sitzt der eigentliche Prozessor (Logic-Die) mit 24 Kernen als zehnte Schicht oben auf dem SRAM. Die 24 Kerne teilen den SRAM in 24 sogenannte Vaults auf, die direkt unterhalb des Rechenkerns liegen. Jedem Kern stehen 4 MB an SRAM zu jeweils 8x 512 kB zur Verfügung. Für die Kommunikation innerhalb der einzelnen Schichten wird das TCI verwendet. Für die Strom- und Spannungsversorgung werden im QUEST noch immer TSVs verwendet.

Alternativ möglich wäre auch der Einsatz von Highly-Doped Silicon Vias (HDSVs). Dabei handelt es sich um hochdotierte Kanäle in vertikaler Richtung, die zur Versorgung, aber nicht zur Kommunikation verwendet werden. Anders als TSVs ist die Fertigung der HDSVs aber deutlich einfacher. Allerdings ist die Entwicklung dieser HSDVs noch in einem recht frühen Stadium und daher wurde noch auf TSVs zurückgegriffen.

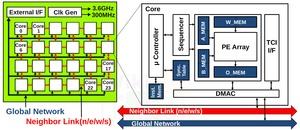

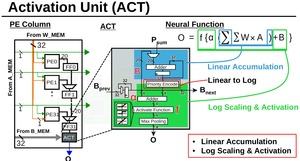

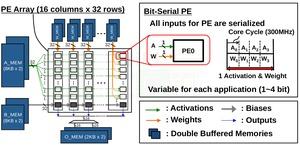

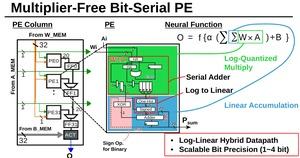

Die 24 Inferencing-Kerne des QUEST arbeiten mit einem Takt von 300 MHz. Die TCI-Kanäle laufen mit 3,6 GHz und bestehen aus sieben Transceiver-und fünf Empfangs-Spulen. Die Latenzen für das Lesen und Schreiben von Daten belaufen sich auf 3 Cycles. Die Bandbreite beläuft sich auf 9,6 GB/s pro Vault oder 28,8 GB/s pro Modul. Untereinander sind die 24 Kerne in einem Mesh organisiert und kommunizieren auch über eine solche Topologie. Es gibt einen Link zum direkten Nachbarn und zu einem globalen Interconnect.

Die Rechenaufgaben für QUEST sind das Inferencing, also die Auswertung von Deep-Learning-Netzwerken. Dabei geht es beispielsweise um eine schnelle Bilderkennung oder Sensorauswertung im Allgemeinen. Bisher wird Hardware häufig wird das Training solcher Netzwerke und deren Auswertung verwendet. Auf die jeweiligen Aufgabe spezialisierte Hardware kann diese häufig aber deutlich schneller bewältigen.

Die Rechenleistung des QUEST-Chips hängt von der Komplexität der Aufgabe ab. Die Genauigkeit kann zwischen 1 und 4 Bits gewählt werden. Bei 4 Bit erreicht der QUEST 1,96 TOPS, für 1 Bit sind es 7,49 TOPS. Die Leistungsaufnahme soll bei 3,3 W inklusive des SRAMs liegen.