Werbung

Irgendwann ab dem zweiten Quartal will AMD auf dem Servermarkt erneut einen Angriff starten und die Dominanz von Intel brechen. Mit den RYZEN-Prozessoren ist AMD dies weitestgehend gelungen, wenngleich auch nur ein Anfang gemacht ist. Auf dem Servermarkt dürfte die Aufgabe ungleich schwerer sein, denn hier spielte AMD in den vergangenen Jahren gar keine Rolle mehr.

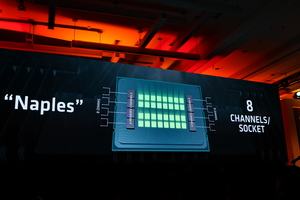

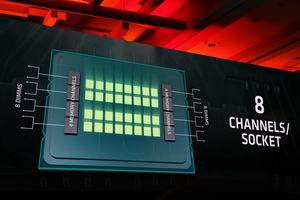

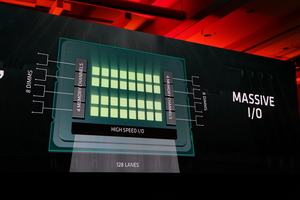

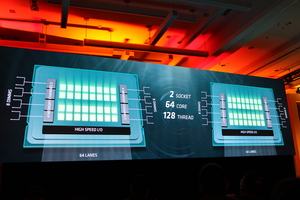

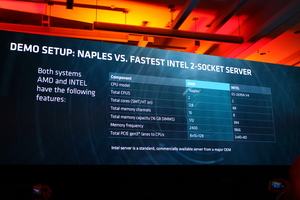

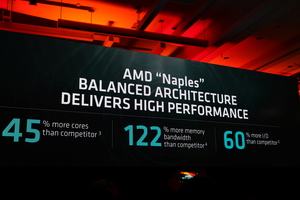

Die zuletzt zu den Naples-Prozessoren veröffentlichten Informationen beschrieben auch erstmals die PCI-Express-Konfiguration, Anbindung des Infinity Fabric und die Unterstützung von DDR4 im Quad-Channel-Betrieb. Erstmals zeigte AMD auch einen Leistungsvergleich zu Intel und sieht sich dementsprechend gut aufgestellt.

RYZEN macht bei acht CPU-Kernen Schluss

Die aktuellen RYZEN-Prozessoren bieten bis zu acht Kerne und können dank SMT bis zu 16 Threads gleichzeitig verarbeiten. Bei Intel ist auf dem High-End-Desktop aber auch der Intel Core i7-6950X verfügbar, der zehn CPU-Kerne und 20 Threads verarbeiten kann. Mit den zukünftigen High-End-Prozessoren von Intel dürfte es auch bei acht Kernen und mehr bleiben.

Die Frage ist also: Plant AMD Ableger von Naples für den High-End-Desktop? Auf dem RYZEN-Tech-Day verneinte AMD dies. Die RYZEN-Prozessoren seien für den Desktop vorgesehen und die Naples-Prozessoren demnach auf den Servermarkt beschränkt.

Pour rappel, les samples actuels de Naples 32c/64t (64 MB L3) sur SP3 en stepping B0 tournent à 1.9/2.5/3.0 GHz pour un TDP de 180W. pic.twitter.com/ee61e6Y0u3

— Canard PC Hardware (@CPCHardware) March 18, 2017

Nun sind weitere Details zu den Samples von Naples aufgetaucht. Demnach bietet der Naples-Prozessor mit 32 Kernen und 64 Threads im B0-Stepping Taktraten von 1,9, 2,5 und 3,0 GHz – je nachdem wie viele Kerne aktuell aktiv sind. Bei allen 32 Kernen dürften es dementsprechend 1,9 GHz sein. Der maximale Boost bei nur wenigen CPU-Kernen beträgt offenbar 3,0 GHz. Die Thermal Design Power dieses Modells soll sich auf 180 W belaufen.

Bisher hat sich AMD noch nicht zu weiteren Naples-Varianten geäußert. Bisher bekannt ist nur das 32C/64T-Modell. Das französische Magazin Canard PC Hardware war auch schon bei den RYZEN-Samples sehr gut informiert und bringt nun erstmals Informationen zu einem 16C/32T-Modell in Erfahrung. Demnach soll dieser in vier bis sechs Monaten vorgestellt werden.

Il y a bien des Ryzen 16C/32T axés HEDT prévus sur X399 dans 4/6 mois. Clocks ~2.4/2.8G. 2 dies MCM. 4 chan DDR4. Socket LGA SP3r2. ~150W. ?

— Canard PC Hardware (@CPCHardware) March 18, 2017

Um auf 16 CPU-Kerne zu kommen, verwendet AMD zwei Zeppelin-Dies mit jeweils acht Kernen. Diese sind in einem MCM (Multi Chip Module) aufgebaut. Der DDR4-Speicher wird hier über vier Kanäle angebunden. Die Taktraten sollen sich auf 2,4 bzw. 2,8 GHz belaufen. Als Sockel kommt der SP3r2 zum Einsatz, also eine Weiterentwicklung des SP3, der ansonsten bei den Naples-Prozessoren verwendet wird. Die Thermal Design Power soll 150 W betragen.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Derzeit wird spekuliert, ob nicht ein 16-Kern-Naples-Prozessor auch für den High-End-Desktop in Frage kommt. Belastbare Hinweise darauf gibt es nicht. Aber warum nicht einmal zumindest darüber nachdenken?

Update:

Die Kollegen von Canard PC Hardware haben weitere Informationen zu einem 16-Kern- 32-Thread-Prozessor, der hier als RYZEN-Modell bezeichnet wird. Damit dürfte die Frage geklärt sein, ob dieses Modell ausschließlich für den Server-Markt vorgesehen ist oder aber AMD tatsächlich auch den Workstation-Mark und High-End-Desktop-Markt bedienen will.

2nd Gen B1 ES for Ryzen 16C/32T on X399 platform incoming. Speed (and TDP) bumped to 3.1/3.6 GHz @ 180W on these samples. Still not QS.

— Canard PC Hardware (@CPCHardware) March 22, 2017

Beim Prozessor soll es sich um ein Modell aus dem 2. Generation des B1-Steppings handeln, der aber noch immer ein Engineering Sample und kein Quality Sample ist. Die Taktraten sollen mit 3,1 bzw. 3,6 GHz etwas höher ausfallen. Die Thermal Design Power beträgt 180 W.