Werbung

Im Rahmen des "Advancing AI 2025"-Events hat AMD mit der Instinct-MI350-Serie die nächste Generation seiner Instinct-Beschleuniger vorgestellt, die auf Basis der CDNA-4-Architektur in zahlreichen Bereichen Verbesserungen vorzuweisen haben, die AMD näher an den großen Konkurrenten NVIDIA bringen sollen. Ob dies gelungen ist, hängt von zahlreichen Faktoren ab. AMD hatte für die Instinct-MI350-Serie allerdings einige selbst gesteckte Ziele, die man nach eigener Aussage erfüllen konnte und die den Weg zu einer erfolgreichen Plattform ebnen sollen.

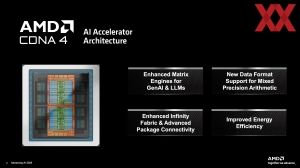

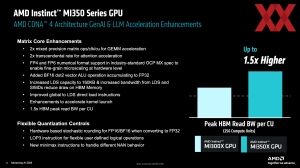

Für die Instinct-MI350-Serie sieht AMD für bestimmte Datentypen eine Verdopplung der Rechenleistung vor, ohne den Energieverbrauch ebenfalls zu verdoppeln. Um dies umsetzen zu können, wurde sowohl die Speicherbandbreite als auch die Datennutzung optimiert. Darüber hinaus wurden Innovationen im Bereich der Quantisierung vorangetrieben, wobei insbesondere bei den Datentypen wie FP8 sowie den wohl künftig immer wichtiger werdenden Formaten FP6 und FP4 eine große Rolle spielen wird.

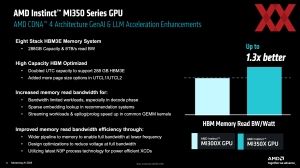

Zusätzlich soll die Energieeffizienz durch eine Reduktion des Stromverbrauchs im sogenannten Un-Core-Bereich verbessert worden sein. Hier spielen vor allem das Speicher-Subsystem rund um den HBM3E und die Speichercontroller eine wichtige Rolle. Zu diesen Details kommen wir allerdings noch.

In der Vergangenheit hat AMD bereits zu zahlreichen Gelegenheiten bewiesen, dass man zusammen mit TSMC Chips und Packages auf dem höchsten technologischen Level fertigen kann. Die Instinct-MI250-Serie setzte erstmals auf eine 2.5D-Bridge, um zwei Compute-Chips miteinander zu verbinden. Mit der Instinct-MI300-Serie kam dann noch ein 3D Hybrid-Bonding hinzu (SoIC), bei dem die Compute-Chips (ab hier XCD genannt) auf den IODs platziert wurden.

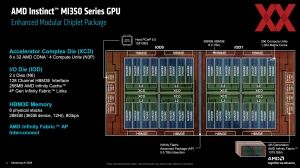

Die Instinct-MI350-Serie setzt dies nun fort, ohne dabei einen völlig neuen Ansatz zu wählen, denn es bleibt bei der Integration mittels 2.5D-Bridge und einem 3D Hybrid-Bonding. In der Fertigung gibt es jedoch einen Fortschritt zu vermelden. Denn wurden die XCDs bisher in N5 bei TSMC gefertigt, laufen diese nun in N3P vom Band. Der IOD wird weiterhin in N6, ebenfalls bei TSMC, gefertigt.

| Instinct MI300X | Instinct MI300A | Instinct MI325X | Instinct MI350X/355X | |

| Architektur | CDNA 3 | CDNA 3 | CDNA 3 | CDNA 4 |

| IODs | 4 (N6) | 4 (N6) | 4 (N6) | 2 (N6) |

| XCDs | 8 (N5) | 6 (N5) | 4 (N5) | 8 (N3P) |

| CCDs | - | 3 | - | - |

| Anzahl der Transistoren | 153 Milliarden | 146 Milliarden | 153 Milliarden | 185 Milliarden |

| Compute Units | 304 | 152 | 304 | 256 |

| Stream-Prozessoren | 19.456 | 14.592 | 19.456 | 16.384 |

| Matrix-Kerne | 1.216 | 912 | 1.216 | 1.024 |

| Zen-4-Kerne | - | 24 | - | - |

| Infinity Cache | 256 MB | 256 MB | 256 MB | 256 MB |

| HBM3 | 192 GB | 128 GB | 256 GB | 288 GB |

| Speicherbandbreite | 5,3 TB/s | 5,3 TB/s | 6 TB/s | 8 TB/s |

| TDP | 750 W | 760 W | 750+ W | 1.000 / 1.400 W |

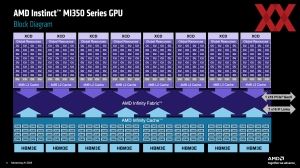

Im Aufbau des Packages ist zu erkennen, dass AMD einige Änderungen am Package als solches und dem XCD und IOD vorgenommen hat. Anstatt vier IODs kommen für die Instinct-MI350-Serie derer nur noch zwei zum Einsatz. Auf den zwei größere IODs sitzen mit acht XCDs die gleiche Anzahl an Compute-Chips. Diese sind ebenfalls leicht anders aufgebaut. Neben dem Wechsel auf die CDNA-4-Architektur hat AMD die Anzahl der Compute-Units von 38 auf 32 reduziert.

Der Grund dafür liegt im Instinct-MI300A-Beschleuniger, bei dem zwei XCDs gegen einen CCD mit Zen-4-Kernen ersetzt wurde. Dennoch wollte AMD eine gewisse FP64-Rechenleistung pro Beschleuniger sicherstellen, so dass die Anzahl der Compute-Units auf 304 festgelegt wurde. Da es zunächst einmal keinerlei neue Beschleuniger-APU für das Rechenzentrum geben wird, kann man mit den acht XCDs die notwendigen Recheneinheiten mit 256 Compute-Units darstellen. Diese sind in Shader-Engines zu jeweils 32 Compute-Units organisiert. In der Fertigung sieht AMD je Shader-Engine vier Compute-Units als Redundanz vor, so dass die Schwankungen in der Ausbeute der Fertigung ausgeglichen werden können.

Der weitere Aufbau des Packages sieht vor, dass diese XCDs per Hybrid-Bonding mit dem darunterliegenden IOD verbunden sind. Als Protokoll kommt Infinity Fabric zum Einsatz. Diese Verbindung kommt pro XCD auf eine Bandbreite von XX TB/s (in der Instinct-MI300-Serie waren es 2,1 TB/s). Im IOD befinden sich wiederum die 256 MB an Infinity Cache, die in 128 jeweils 2 MB große Blöcke aufgeteilt sind. Die Speichercontroller für die HBM3E-Chips befinden sich ebenfalls im IOD. Insgesamt kommen die 288 GB an HBM3E auf eine Speicherbandbreite von 8 TB/s.

Die verwendeten HBM3E-Chips bestehen aus 12-DRAM-Layern und kommen somit auf eine Kapazität von jeweils 36 GB. Bei 8 GBit/s/Pin werden eben die insgesamt 8 TB/s an Speicherbandbreite erreicht.

Ebenfalls über den IOD bereitgestellt werden 128 SerDes-Endpunkte (Serialisierer/Deserialisierer), welche wiederum für die PCI-Express- und Infinity-Fabrik-Links benötigt werden. 7x 153,6 GB/s für insgesamt 1.075 GB/s stehen für die Anbindung der GPUs untereinander in einem Rack zur Verfügung. Hinzu kommen 16 PCI-Express-5.0-Lanes für die Anbindung an die Host-CPU.

Die beiden IODs sind mittels Infinity Fabric Advanced Package (AP) miteinander verbunden. AMD gibt eine bidirektionale Bandbreite von 5,5 TB/s an.

| Instinct MI300 | Instinct MI325 | Instinct MI350 | |

| IOD-IOD | 1,5 / 1,2 TB/s | 1,5 / 1,2 TB/s | 5,5 TB/s |

| XCD-IOD | 2,1 TB/s | 2,1 TB/s | 1,53 TB/s |

| IOD-HBM | 665 GB/s / HBM-Stack | 768 GB/s / HBM-Stack | 1.024 GB/s / HBM-Stack |

| IOD-Infinity Fabric | 4x 64 GB/s | 8x 64 GB/s | 7x 153,6 GB/s |

In der Instinct-MI-300/325-Serie sind die vier IODs untereinander in horizontaler oder vertikaler Richtung mit jeweils 3 TB/s (2x 1,5 TB/s) und 2,4 TB/s (2x 1,2 TB/s) angebunden. Für die Instinct-MI350-Serie gibt AMD 5,5 TB/s an, was ziemlich genau auf dem gleichen Niveau liegt, wie bisher auch schon.

Zwischen einem XCD und den IOD gibt AMD die Bandbreite mit 1,53 GB/s an, was unter dem liegt, was die Instinct-MI300-Serie zu bieten hatte. Laut AMD hat man die Bandbreite daran angepasst, was über den HBM3E an den XCD geliefert werden muss und hier sollen 1,53 TB/s ausreichend sein für eine XCD. Maßnahmen wie breitere Datenpfade des Infinity Fabric und ein Filtern der Transaktionen zwischen dem Infinity Cache und HBM3E sollen die nutzbare Bandbreite effektiver nutzbar machen.

Änderungen im Partitioning und den NUMA-Domänen

Die Beschleuniger der Instinct-MI350-Serie können in verschiedene Compute-Partitionen unterteilt werden, was im Hinblick auf eine Single Root Input/Output Virtualisierung (SR-IOV) auch notwendig ist.

Der Instinct-MI300X/325X-Beschleuniger bietet die Unterstützung von NPS1 und NPS4-Modus – der Speicher kann also als einzelne NUMA-Domäne angesprochen werden oder wird in vier aufgeteilt. Hinzu kommt eine Unterteilung in zwei, vier und acht Partitionen, wobei die Blöcke aus jeweils zwei XCDs jeweils den kleinsten Baustein dieser Aufteilung darstellen. Auch hier wird die maximale GPU-Auslastung bei acht Partitionen erreicht.

Mit der Instinct-MI350-Serie neben NPS1 wird nun nur noch NPS2 unterstützt – NPS4 fällt weg. AMD wählt NPS2 aus mehreren Gründen: Einerseits haben die Modelle Größen erreicht, die 2x 144 GB als sinnvoll einsetzbar ansehen, eine weitere Halbierung aber kaum sinnvoll ist. Zudem ist in NPS2 der HBM3E genau auf die zwei IODs und deren Anbindung aufteilt. Weiterhin unterstützt wird eine Partitionierung, wobei für SPX (Single Partition) auch ein NPS1 vorgesehen ist, während für DPX (zwei Partition), QPX (vier Partition) und CPX (acht Partitionen) immer NPS2 verwendet wird.

Möglich ist somit eine Aufteilung der Instinct-MI350-Hardware in acht Instanzen, die jeweils ein Llama-3.1-Modell mit 70 Milliarden Parametern verarbeiten, während die großen Modelle in einer einzelnen Partition verbleiben müssen.

Vergleich der Datentypen und theoretischen Rechenleistung

Innerhalb der CDNA-4-Architektur hat AMD einige Änderungen vorgenommen, welche vor allem darauf ausgelegt sind, dass hier die Datentypen FP8, FP6, FP4 und die dazugehörigen Matrix-Operationen eine höhere Rechenleistung erreichen.

| Instinct MI300X | Instinct MI355X | |

| fmax | 2,1 GHz | 2,4 GHz |

| Vektor FP64 | 81,7 TFLOPS | 78,6 TFLOPS |

| Vektor FP32 | 163,4 TFLOPS | 157,3 TFLOPS |

| Vektor FP16 | 163,4 TFLOPS | 157,3 TFLOPS |

| Matrix FP64 | 163,4 TFLOPS | 78,6 TFLOPS |

| Matrix FP32 | 163,4 TFLOPS | 157,3 TFLOPS |

| Matrix FP16/BF16 / mit Sparsity | 1,3 / 2,6 PFLOPS | 2,5 / 5 PFLOPS |

| Matrix FP8 / mit Sparsity | 2,6 / 5,2 PFLOPS | 5 / 10 PFLOPS |

| Matrix INT8/INT4 / mit Sparsity | 2,6 / 5,2 POPS | 5 / 10 POPS |

| Matrix FP6/FP4 / mit Sparsity | - | 10 / 20 PFLOPS |

Durch die Reduzierung der Compute-Units von 304 auf 256 geht die theoretische Rechenleistung trotz einer Taktsteigerung (fmax) von 2,1 auf 2,4 im Vergleich zwischen dem Instinct MI300X und MI355X für Vektorberechnungen (FP64, FP32 und FP16) sowie Matrix FP32 leicht zurück. Für Matrix FP64 wird sie sogar halbiert, aber der Fokus für den Instinct-MI350-Beschleuniger lag auch nicht auf der FP64-Rechenleistung.

Für das Training und Inferencing von KI-Modelle weitaus wichtiger sind die Matrix-Operationen bei einer geringeren Genauigkeit. Für diese können die Instinct-MI350-Beschleuniger die Rechenleistung fast verdoppeln. Anders als die Instinct-MI300-Familie auf Basis der CDNA-3-Architektur sieht AMD für die Instinct-MI350-Familie dedizierte FP6-Recheneinheiten vor, die keine FP8-Recheneinheit belegen. Der Durchsatz für FP6 und FP4 ist identisch – ein Novum in diesem Bereich.

Wie bereits in der ersten Tabelle erwähnt, sieht AMD zwei Varianten der Instinct-MI350-Beschleuniger vor: Einen Instinct MI350X sowie einen Instinct MI355X. Der Unterschied zwischen diesen beiden liegt in der Kühlung und damit auch dem maximalen Takt. Während der Instinct MI350X eine TDP von 1.000 W und einen maximalen Takt von 2,2 GHz vorzuweisen hat, sind es beim Instinct MI355X 1.400 W und ein maximaler Takt von 2,4 GHz. Die Kühlung erfolgt bei erstgenanntem Beschleuniger mittels Luft und beim zweiten mittels Wasser.

Entsprechend sieht AMD vollständige Racks vor, die in der luftgekühlten Variante Instinct MI350X bis zu 64 Beschleuniger und in der wassergekühlten Variante Instinct MI355X bis zu 128 Beschleuniger zusammenfassen. Die Peak-Rechenleistung und Gesamtkapazität des Speichers wird hier einfach aufaddiert.

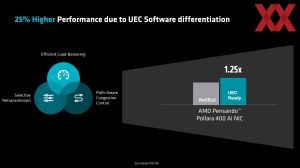

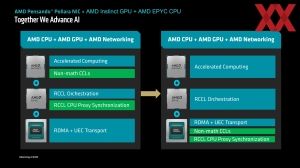

Zudem wird deutlich, dass AMD weiterhin an Infinity Fabric auf Node-Ebene festhält, was die Anzahl der direkt miteinander verbundenen Beschleuniger auf acht begrenzt. NVIDIA kann via NVLink bis zu 72 Blackwell-GPUs miteinander verbinden, während AMD bei allem, was über die acht Beschleuniger hinausgeht, auf Ethernet zurückgreifen muss.

Instinct MI300X vs. Instinct MI350X

Durch die Optimierungen in der CDNA-4-Architektur, der neuen Fertigung sowie dem größeren und schnelleren Speicher sieht AMD einen signifikanten Leistungssprung vom Instinct MI300X zum Instinct MI350X.

Alleine auf die Speicherbandbreite und Lese-Bandbreite pro Compute Units bezogen orientiert sich AMD an einem theoretischen Plus von 30 bis 50 %. Abseits der theoretischen Maximalwerte für den Speicher und die Datentypen sucht man jedoch vergebens einen direkten Vergleich.

Stattdessen will AMD zugleich mit ROCm 7 eine neue Version der Software veröffentlichen, die signifikante Vorteile mit sich bringen soll.

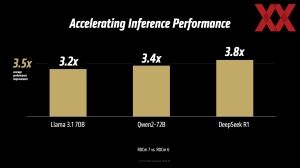

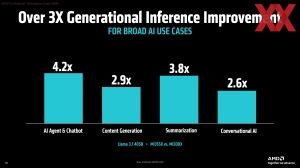

In der Inferencing-Leistung präsentiert AMD einige Vergleiche zwischen dem neuen Instinct MI355X und dem Vorgänger Instinct MI300X – den Zwischenschritt Instinct MI325X mit mehr HBM3E-Speicher sieht man nicht als typischen Upgrade-Pfad. Je nach Anwendungsbereich soll der neue Beschleuniger um den Faktor 2,6 bis 4,2 schneller sein.

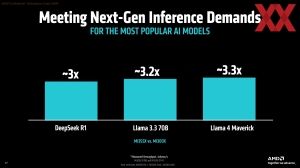

Bezogen auf das Inferencing (Durchsatz von Tokens) von Large Language Models soll der Instinct-MI355X-Beschleuniger für DeepSeek R1, Llama 3.3 70B und Llama 4 Maverick um mindestens den Faktor drei schneller sein. Allerdings sei hier angemerkt, dass der Instinct-MI300X-Beschleuniger mit FP8 arbeitete, während der neue Instinct-MI355X-Beschleuniger das kompaktere Datenformat FP4 verwendete und der Durchsatz hier bereits doppelt so hoch ausfällt.

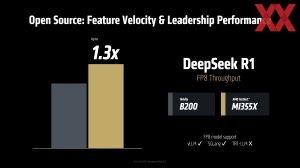

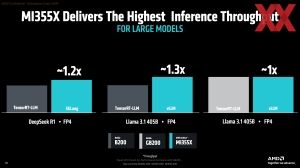

Einen Vergleich zur Konkurrenz wagt man dennoch. Dazu herangezogen werden der B200- und GB200-Beschleuniger von NVIDIA. AMD sieht sich durchaus auf Augenhöhe.

In einem weiteren Leistungsvergleich soll der Instinct-MI355X-Beschleiniger um 30 % schneller als NVIDIAs B200-Beschleuniger sein – bezogen auf den Durchsatz im FP8-Datenformat.

Welchen Einfluss allein die Software hat, zeigt der abschließende Vergleich zwischen ROCm 6 und ROCm 7. Ein Instinct-MI300X-Beschleuniger wird durch den Einsatz von ROCm 7 im Vergleich zu ROCm 6 um den Faktor drei schneller. Allerdings sei an dieser Stelle darauf verwiesen, dass AMD nicht mit der aktuellen ROCm-6-Version vergleicht, sondern hier Werte nimmt, die mit der zum Zeitpunkt des Erscheinens des jeweiligen Modells verfügbaren Version gemacht wurden. Es kann also nicht davon ausgegangen werden, dass die Nutzer einer Verdreifachung der Leistung durch den Wechsel auf ROCm sehen. Dies ist auch abhängig vom jeweiligen KI-Modell, der Quantisierung und vielem mehr.

Bei den Benchmarks muss man also sehr genau hinschauen, welche Voraussetzungen hier angewendet werden.

Ab dem dritten Quartal verfügbar

Aktuell befinden sich die Instinct-MI350-Beschleuniger bei den ersten Partnern. Mit einer großflächigen Verfügbarkeit ist im dritten Quartal zu rechnen. Ob AMD mit den neuen Beschleunigern eine echte Konkurrenz zu NVIDIAs Blackwell Ultra sein wird, werden die kommenden Monate zeigen müssen.