Werbung

Gestern Abend fand in New York City der Financial Analyst Day vom AMD statt, der sich maßgeblich an Investoren richtet, auf dem AMD aber auch immer ein paar Details zu zukünftigen Produkten verrät.

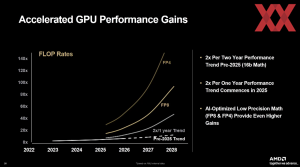

Ein wesentlicher Themenbereich der vierstündigen Veranstaltung beschrieb natürlich das mögliche Wachstum und das Potenzial im Datacenter-Segment - und hier vor allem den KI-Sektor. Die letzten Quartalszahlen zeigten ein Wachstum von 22 % gegenüber dem Vorjahreszeitraum. Damit liegt man zwar noch immer weit hinter NVIDIA, aber die Auftragsbücher von AMD sind dennoch prall gefüllt. So verkündete man kürzlich eine strategische Partnerschaft mit OpenAI und will über mehrere Jahre hinweg 6 GW an Rechenleistung installieren. Auch mit dem Department von Energie (DoE) und den lokalen Laboratorien gibt es Vereinbarungen zu neuen Supercomputern.

In den kommenden Jahren will AMD im KI-Datacenterbereich um jeweils 80 % wachsen. Der Marktanteil am Umsatz bei den Server-Prozessoren soll 50 % und mehr erreichen. Aktuell liegt AMD hier bei etwa 30 %, vor 2020 lag der Marktanteil noch im einstelligen Prozentbereich. Auch der Marktanteil am Endkundenmarkt soll weiter steigen. Ziel sind 40 % und mehr. In den letzten Erhebungen lag AMD hier bei 20 bis 30 % – je nach Marktsegment.

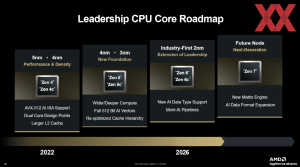

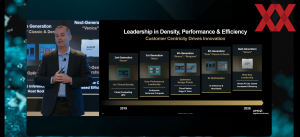

Angekündigt wurden auch neue Roadmaps, wenngleich das, was man präsentiert hat, kaum eine Überraschung bot. Mit der Zen-6-Architektur führt AMD seine Strategie der "vollen" und "kompakten" Kerne fort. Zen 6 und Zen 6c werden vermutlich für die Epyc- und Notebook-Prozessoren zum Einsatz kommen – analog zur aktuellen Zen-5-Generation. Den Anfang machte diese Strategie mit der Zen-4-Architektur.

Für Zen 6 sieht AMD weitere Anpassungen zur Unterstützung der neuen KI-Datenformate vor und auch die Rechenpipeline der Kerne selbst wird dahingehend ausgelegt werden. Weitere Details zur Zen-6-Architektur gibt es nicht. Die Fertigung der CCDs mit den Zen-6-Kernen in 2 nm bei TSMC N2 ist bereits bekannt.

Zen 7 scheint ebenfalls voll auf ein weiteres Wachstum bei der KI-Rechenleistung ausgelegt zu sein. AMD nennt eine neue Matrix Engine zur Verarbeitung von KI-Datenformaten sowie weitere Erweiterungen für diese KI-Datenformate.

Bereits in diesem Jahr will AMD mit der 5. Epyc-Generation alias Turin die 40 % an Marktanteil beim Umsatz erreichen. Vor allem seit 2022 und der Einführung der 3. Generation alias Milan konnte AMD seinen Marktanteil deutlich steigern. Einerseits lag dies laut AMD an der starken allgemeinen Kern- und auch der Plattform-Leistung. Anders gesagt: Die Kern-Architekturen und Anzahl der Kerne pro Sockel überbot das Angebot des Konkurrenten und bei den Plattform-Funktionen war man an diesem längst vorbeigezogen, was viele Kunden von einem Wechsel überzeugte.

Mit der Einführung der SKUs mit mehr Cache (analog zu den X3D-Modelle bei den Ryzen-Prozessoren bzw. dem 3D V-Cache) und gezielt auf höhere Taktraten ausgelegte Modellen adressierte AMD auch den aufkommenden KI-Markt, wo die KI-Beschleuniger auf schnelle Host-Prozessoren angewiesen sind.

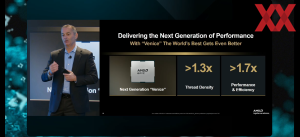

Die 6. Generation alias Venice auf Basis der Zen-6-Architektur soll eine um 30 % höhere Thread-Dichte zu bieten haben (sprich in etwa 30 % mehr Kerne) und bietet eine um 70 % höhere Leistung und Effizienz. Mit Venice will AMD dann endgültig den besten Server-Prozessor am Markt zu bieten haben, der seine Konkurrenz in allen Belangen aussticht.

Im Client-Geschäft wird es erst 2027 wieder interessant

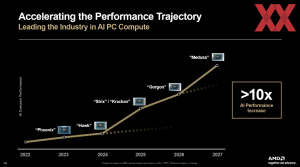

Die fundamentalen Funktionen von Zen 6 und Zen 7, die AMD hier nennt, beziehen sich maßgeblich auf das Datacenter-Geschäft. Aber auch die Client-Sparte bekam ein paar Minuten an Aufmerksamkeit. Bereits auf dem OCP Global Summit 2025 nannte AMD erstmals offiziell den Codenamen einer APU mit Zen-6-Kernen: Medusa.

Nun ebenfalls genannt wurde die nächste Ryzen-Desktop-Generation. Olympic Ridge soll ab der zweiten Jahreshälfte 2026 gefertigt werden.

Darüber hinaus wollte AMD aber keinerlei Details verraten. Zudem zeigt der Zeitstrahl bzw. die X-Achse, dass Medusa erst für 2027 geplant ist. Es ist also nicht davon auszugehen, dass 2026 neue Ryzen-Prozessoren das Licht der Welt erblicken werden. Stattdessen wird es eher einen Refresh geben, wie er sich schon vor einigen Wochen angekündigt hat.

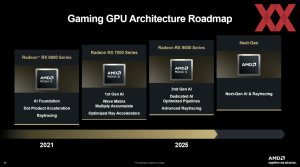

Für die Radeon-RX-Grafikkarten zeigte AMD nur die schon bekannte Roadmap, die aber einfach nur von "Next-Gen" spricht.

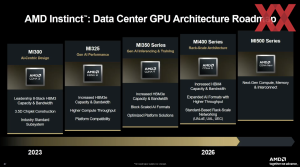

Instinct MI400 und 500 greifen NVIDIA an

Bereits am Anfang dieses Berichts haben wir erwähnt, dass AMD im KI-Datacenterbereich großes Wachstum zu verzeichnen hat, dieses in den kommenden Monaten und Jahren aber weiter stark steigern will. Mit der Instinct-MI350-Serie wurde eine Basis geschaffen, die mehr als nur eine verfügbare Alternative zu NVIDIA darstellte.

Mit der Instinct-MI400-Serie will man dann final auf Augenhöhe mit NVIDIA angekommen sein. Die schon erwähnte Partnerschaft mit OpenAI soll dies unterstreichen und auch andere Hyperscaler wie Microsoft, AWS sowie zahlreiche weitere haben den zukünftigen Einsatz von Instinct-MI400-Hardware im größeren Maßstab angekündigt.

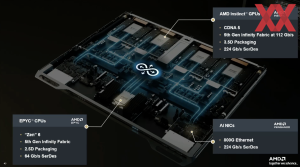

Die ersten Details zur Instinct-MI400-Serie hat AMD bereits auf dem "Advancing AI 2025"-Event verkündet. 40 PFLOPS an FP4-Rechenleistung, 432 GB an HBM4, 19,6 TB/s an Speicherbandbreite und 300 GB/s an Scale-Out-Bandbreite sind die Kerndaten.

Mit der Instinct-MI400-Serie fährt AMD in gewisser Weise zweigleisig. Es wird Hardware in Form einer Instinct MI400X und MI455X geben, die klar auf das KI-Segment ausgelegt sind. Daneben wird es aber auch noch HPC-Beschleuniger geben, die als Instinct MI430X bereits für die Supercomputer Lux und Discovery angekündigt wurden. Hier wird die FP64-Rechenleistung noch eine größere Rolle spielen, da sie für Simulationen weiterhin nicht durch eine simulierte oder KI-gestützte FP64-Rechenleistung ersetzt werden kann.

Auf die Instinct-MI400-Serie wird die Instinct-MI500-Serie folgen, die dann auf Basis einer nächsten CDNA-Architektur die Rechenleistung weiter steigern soll. Neue Speicherstandards und noch schnellere Interconnects sollen diesen Prozess unterstützen.

AMD füllt TSMCs Fertigungsstraßen

Egal ob in N2 gefertigte CDDs mit Zen-6-Kernen oder die Herstellung der Compute- und Base-Dies für die kommenden Instinct-Beschleuniger sowie das Packaging: AMD ist und bleibt ein wichtiger Partner für TSMC und stürmt hier in gewisser Weise auch auf die Pole Position, wenn es um neue Technologien geht.

Die erwähnten CCDs mit den Zen-6-Kernen werden die ersten Chips sein, die bei TSMC in N2 in einem 2-nm-Prozess im größeren Maßstab gefertigt werden.

Auch für die Instinct-MI400-Serie wird AMD voll aus TSMC setzen, wenngleich hier noch keinerlei spezifische Details verraten wurden. Während man für die Instinct-MI350-Beschleuniger auf N3P und N6 im Zusammenspiel mit einem CoWoS-S-Packaging gesetzt hat, wird man für die Instinct-MI400-Serie ebenfalls auf ein 3.5D-Stacking setzen und dies mit einem CoWoS-L-Packaging kombinieren.

CoWoS-S und CoWoS-L sind beide 2.5D-Packaging-Technologien von TSMC, unterscheiden sich aber in mehreren wesentlichen Aspekten. CoWoS-S, das seit 2016 in Produktion ist, verfügt über einen Silizium-Interposer mit einem maximalen Reticle-Limit von 3,3x (was etwa 2.700 mm² entspricht) und kann bis zu acht HBM-Chips (HBM2, HBM2e oder HBM3) integrieren. Die Logic-Chiplets werden dabei in den Prozesstechnologien N5 oder N4 gefertigt.

CoWoS-L hingegen ist die neuere Generation, die mit deutlich größeren Interposern von bis zu 9,5x Reticle-Größe aufwartet und somit theoretisch bis zu 7.900 mm² Fläche bietet, während der darunter liegende Substrat-Layer sogar 18.000 mm² Platz bereitstellt. Der entscheidende Vorteil von CoWoS-L liegt in der erheblich erweiterten Integrationsfähigkeit: Die Technologie unterstützt bis zu 12 HBM3E/HBM4-Chips gleichzeitig und ermöglicht die Integration von größeren und mehr Logic-Chiplets in fortgeschritteneren Prozesstechnologien wie N3 und N2. Zusätzlich integriert CoWoS-L aktive Komponenten wie Voltage-Regulatoren (FIVR – Fully Integrated Voltage Regulators) direkt im Silizium-Interposer, was das System flexibler gestaltet und die Gesamtkosten senkt. Während CoWoS-S für etablierte Hochleistungs- und HPC-Anwendungen wie NVIDIA H100 und AMD MI300 das Standard-Packaging darstellt, zielt CoWoS-L auf zukünftige KI-Trainings-Beschleuniger und komplexe Multi-Chip-Systeme ab, die größere Datenmengen und höhere Speicherbandbreiten erfordern.

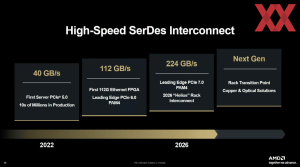

224 GB/s SerDes und 5. Generation des Infinity Fabric als Basis

Zen-Kerne, Matrix-Einheiten, HBM4 – all diese einzelnen Blöcke der Epyc-Prozessoren und Instinct-Beschleuniger können nur dann funktionieren, wenn sie ausreichend schnell miteinander kommunizieren können.

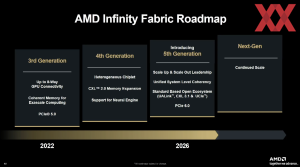

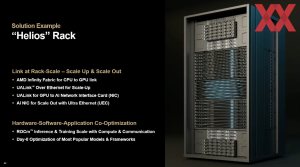

Ein schneller Interconnect ist daher auch ein essentieller Bestandteil des Helios-Racks, welches die Epyc-Prozessoren im Venice-Design mit den Instinct-MI400-Beschleunigern zusammenbringen soll. Für diese Generation an CPUs und Beschleunigern sieht AMD die Umsetzung eines SerDes vor, der 224 GB/s ermöglicht. Auf Basis dieser physikalischen Umsetzung der Schnittstelle können dann die Übertragungsebenen in Form der 5. Generation des Infinity Fabric, PCI-Express 7.0, UALink, CXL 3.1 und UCIe umgesetzt werden.

Im Helios-Rack sind die Epyc-Prozessoren und Instinct-Beschleuniger via Infinity Fabric miteinander verbunden. Das Scale-Out, sprich die Verbindung mehrerer Compute-Nodes untereinander, findet mittels UALink über Ethernet statt. UALink kommt auch zur Anbindung der Instinct-Beschleuniger mit dem Netzwerk-Interface zum Einsatz.

Mit der Auslieferung der einzelnen Komponenten in Form der Epyc-Prozessoren und Instinct-MI450-Beschleuniger werden wir sicherlich noch weitere Details zu deren Aufbau etc. erfahren. Auf dem diesjährigen Financial Analyst Day zeichnete AMD jedenfalls eine weitblickende Roadmap über alle Produktsparten hinweg. Sollte die Ausführung dieser Pläne in Form gelingen, wie dies in den vergangenen Jahren der Fall war, dürfte AMD in allen Marktsegment weiter Boden gutmachen können. Die Konkurrenz wird sich nicht ausruhen können, zumal AMD in einigen Bereichen fast schon als Marktführer bezeichnet werden kann.