News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

CoPoS

-

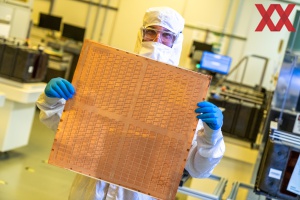

CoPoS-Packaging: TSMC ist auf der Suche nach Interposer-Alternativen

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei... [mehr]

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei... [mehr]