News und Artikel durchsuchen

{{#data.error.root_cause}}

{{/data.error}}

{{^data.error}}

{{#texts.summary}}

[{{{type}}}] {{{reason}}}

{{/data.error.root_cause}}{{texts.summary}} {{#options.result.rssIcon}} RSS {{/options.result.rssIcon}}

{{/texts.summary}} {{#data.hits.hits}}

{{#_source.featured}}

FEATURED

{{/_source.featured}}

{{#_source.showImage}}

{{#_source.image}}

{{/_source.image}}

{{/_source.showImage}}

{{/data.hits.hits}}

{{{_source.title}}} {{#_source.showPrice}} {{{_source.displayPrice}}} {{/_source.showPrice}}

{{#_source.showLink}} {{/_source.showLink}} {{#_source.showDate}}{{{_source.displayDate}}}

{{/_source.showDate}}{{{_source.description}}}

{{#_source.additionalInfo}}{{#_source.additionalFields}} {{#title}} {{{label}}}: {{{title}}} {{/title}} {{/_source.additionalFields}}

{{/_source.additionalInfo}}

Substrat

-

HBM4, C-HBM4 und SPHBM4: Weitere Variante reduziert Breite des Speicherinterface

Ab dem kommenden Jahr werden alle neuen KI-Beschleuniger auf den schnelleren HBM4 setzen. Dieser erhöht nicht nur die Speicherbandbreite im Vergleich zum HBM3E, sondern auch in der Kapazität werden die Beschleuniger noch einmal deutlich zulegen. So werden die Instinct-MI400-Beschleuniger von AMD auf 432 GB an Kapazität und eine Speicherbandbreite von 19,6 TB/s kommen. In ähnliche Dimensionen wird NVIDIA mit der Rubin-Generation vorstoßen,... [mehr]

Ab dem kommenden Jahr werden alle neuen KI-Beschleuniger auf den schnelleren HBM4 setzen. Dieser erhöht nicht nur die Speicherbandbreite im Vergleich zum HBM3E, sondern auch in der Kapazität werden die Beschleuniger noch einmal deutlich zulegen. So werden die Instinct-MI400-Beschleuniger von AMD auf 432 GB an Kapazität und eine Speicherbandbreite von 19,6 TB/s kommen. In ähnliche Dimensionen wird NVIDIA mit der Rubin-Generation vorstoßen,... [mehr] -

Silicon Photonics: TSMC will Partner frühzeitig mit einbeziehen

Neben weiteren Details zur Fertigung der Chips, dem Packaging und der zukünftigen Entwicklung beim Custom-HBM hat TSMC auf dem hauseigenen Open Innovation Platform Ecosystem Forum auch einige Details zur weiteren Entwicklung bei der optischen Datenübertragung verraten. An Technologien wie Silicon Photonics wird seit Jahrzehnten gearbeitet. Chiphersteller wie Intel und NVIDIA stellen die Vorteile einer optischen Datenübertragung auch für extrem... [mehr]

Neben weiteren Details zur Fertigung der Chips, dem Packaging und der zukünftigen Entwicklung beim Custom-HBM hat TSMC auf dem hauseigenen Open Innovation Platform Ecosystem Forum auch einige Details zur weiteren Entwicklung bei der optischen Datenübertragung verraten. An Technologien wie Silicon Photonics wird seit Jahrzehnten gearbeitet. Chiphersteller wie Intel und NVIDIA stellen die Vorteile einer optischen Datenübertragung auch für extrem... [mehr] -

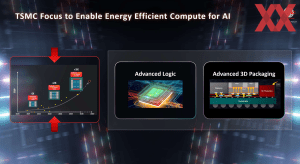

CoPoS-Packaging: TSMC ist auf der Suche nach Interposer-Alternativen

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei... [mehr]

Ein, zwei, vier Compute-Chiplets, dazu bis zu 12 HBM4-Chips und weitere I/O-Chiplets sind die Anforderungen an die Packaging-Technologien in den kommenden Jahren. Ende April legte TSMC auf dem Technology Symposium 2025 offen, wie man sich auf Seiten des Auftragsfertigers die Lösungen für die Zukunft beim Packaging vorstellt. CoWoS (Chip on Wafer on Substrate), InFO (Integrated Fan-Out) und TSMC-SoW (System on Wafer) sind dabei die drei... [mehr] -

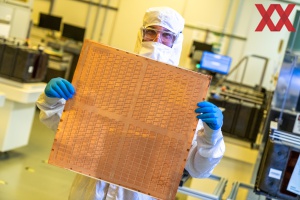

Immer größere Interposer: TSMC soll an rechteckigen Substrat-Trägern arbeiten

Fertigung der Chips, der HBM, der Interposer und das Packaging – all dies sind aktuell mögliche Bremsklötze in der Fertigung der KI-Beschleuniger. Während am Ausbau der Kapazitäten für die Chips, den HBM und das Packaging gearbeitet wird, scheint die Verfügbarkeit an ausreichenden Interposer-Stückzahlen nun zum Problem zu werden. Die Herstellung der Interposer klingt auf den ersten Blick trivial, da sie recht einfach strukturiert sind. Die... [mehr]

Fertigung der Chips, der HBM, der Interposer und das Packaging – all dies sind aktuell mögliche Bremsklötze in der Fertigung der KI-Beschleuniger. Während am Ausbau der Kapazitäten für die Chips, den HBM und das Packaging gearbeitet wird, scheint die Verfügbarkeit an ausreichenden Interposer-Stückzahlen nun zum Problem zu werden. Die Herstellung der Interposer klingt auf den ersten Blick trivial, da sie recht einfach strukturiert sind. Die... [mehr] -

Intel zu Glassubstraten: Das Trägermaterial für die Chips der Zukunft

Am Vorteil der Innovation-Konferenz ergänzte Intel seine im Mai gemachte Veröffentlichung zur Entwicklung bei Glassubraten für zukünftige Chip-Packages. Seit Jahrzehnten kommt das sogenannte organische Substrat zum Einsatz, welches aus einer gewebten Struktur besteht, durch die Signal- und Stromleitungen geführt werden. Das organische Substrat löste dabei vor 30 Jahren das anorganische Keramik-Package ab und ist nun seit 30 Jahren für... [mehr]

Am Vorteil der Innovation-Konferenz ergänzte Intel seine im Mai gemachte Veröffentlichung zur Entwicklung bei Glassubraten für zukünftige Chip-Packages. Seit Jahrzehnten kommt das sogenannte organische Substrat zum Einsatz, welches aus einer gewebten Struktur besteht, durch die Signal- und Stromleitungen geführt werden. Das organische Substrat löste dabei vor 30 Jahren das anorganische Keramik-Package ab und ist nun seit 30 Jahren für... [mehr]